一种高速数据接口的设计方法*

2014-09-25杨瑞瑞张文沛

章 睿,杨瑞瑞,张文沛

0 引言

随着数字通信业务的蓬勃发展导致通信系统对传输带宽提出了更高的挑战,例如10 Gb/s高速并行接口在光纤通信、数据交换、网络通信等方面有着广泛的应用。目前主流元器件解决方案中,主要采用高速串行接口(SerDes)实现高速接口,但SerDes接口工作频率高、设计复杂、价格昂贵。文中设计了一种高速并行差分接口方式,利用国内流片厂商IP,结合自行设计的控制和同步逻辑,可以实现双向10 Gb/s数据接口,满足高速接口的国产化需求。

1 简介

高速并行传输的瓶颈之一是对数据的有效恢复,数据恢复中主要存在两个问题:一是当单线传输速率越来越快时,相应的每位数据所占的时间窗口不断减小,导致时钟很难在数据的有效窗口准确采样;二是由于并行传输的各条数据路径延迟不同,导致接收端无法有效的同步接收并行传输的各路数据。

文中描述一种基于数字的高速并行数据恢复和同步的设计方法,通过对训练数据采样时钟相位的计算反馈输出到DLL锁相环从而改变时钟的采样相位,使时钟采样发生在数据有效窗口的中央,因此能够保证时钟、数据在外界温度、湿度和干扰等情况下正确地采样和恢复出数据。

2 系统结构

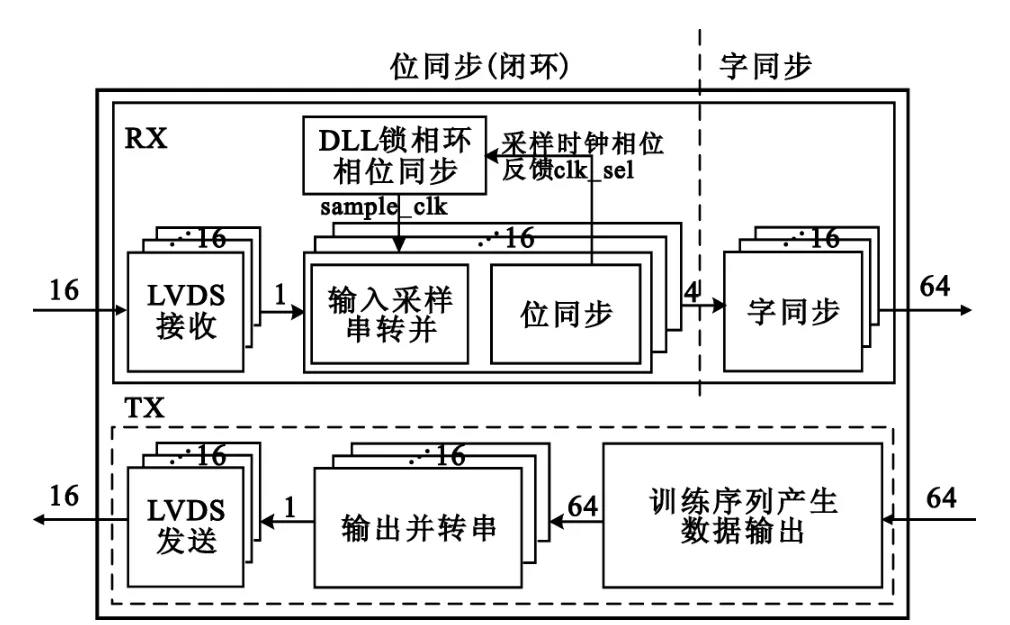

系统结构如图1所示,其包括接收RX与发送TX两个独立部分。

图1 系统结构框Fig.1 System structure

接收部分包括每个通道的低电压差分信号(LVDS)接收电路[1],每个通道的接收串行转并行电路,每个通道的数据采样时钟相位计算和调整模块以及所有通道的字同步模块。其中采样时钟相位调整模块包括一个DLL锁相环和每个通道对应的时钟相位调整无毛刺选择电路MUX。

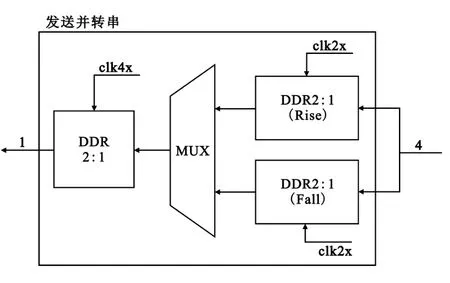

发送部分包括训练序列产生器[2]和数据输出,每个通道的并行转串行电路,每个通道的低电压差分信号(LVDS)发送电路,见图2。

发送部分的电路设计比较简单,控制好640 MHz、320 MHz、160 MHz这三组时钟的相位关系[3],保证64位并行数据通过两次并串转换压缩到16位并行数据,从160 MHz时钟域逐级进入320 MHz时钟域、640 MHz时钟域,最终数据以DDR方式伴随320 MHz随路时钟输出。

图2 并串转换电路Fig.2 P-to-Scircuit

下文重点介绍数据接收部分电路的设计。

3 输入电路

3. 1 串转并电路

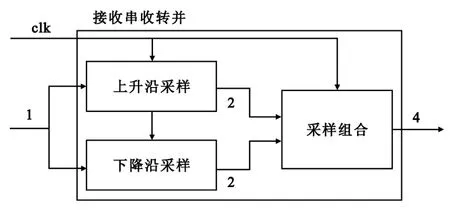

在10G高速并行接收电路中,以16对低电压差分信号(LVDS)差分对接收10G并行数据流[4]。每对LVDS管脚通道的数据为双沿串行数据(DDR),随路时钟320 MHz,经过图3描述的串并转换电路后转换为4位并行数据,并降频进入160 MHz时钟域。

图3 串并转换电路Fig.3 S-to-P circuit

如图3所示,串行数据流进入串并转换电路后,同时接入一个上升沿采样寄存器和一个下降沿采样寄存器[5],采样时钟320 MHz。然后对采样后的数据进行组合,由下一级160 MHz时钟将4 bit的并行数据输出。

3. 2 相位同步电路

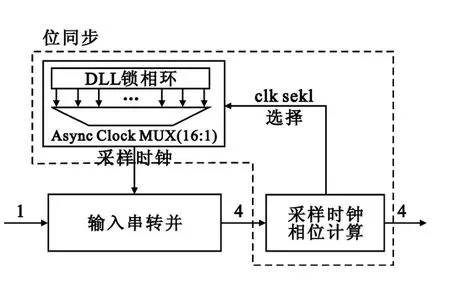

图4为采样时钟相位同步电路框图,包括一个采样时钟相位计算模块和一个由DLL与异步无毛刺时钟切换MUX组成的时钟相位调整模块。

DLL可以对每个数据通道的采样时钟进行1/16精度的相位调整,每个通道每次调整的相位由相位计算模块对采样数据进行处理后反馈给相位调整模块。在高速并行接口正常工作前,发送端与接收端首先发送多组训练数据,选择与每个通道数据相位匹配的时钟信号。

图4 相位同步电路Fig.4 Phase synchronization circuit

高速并行接口正常工作之前,外部器件首先按照约定的方式发送训练数据“0000_0000_0000_0000_0011_1111_1111_1111_1111”,重复发送多次训练数据。

接收端将串行数据转为并行4位数据进行处理,其过程如下:

1)首先通过相位计算电路搜索出串行数据电平的变化沿即对4为数据进行异或,如以“0001”为例得到右边沿“001”。

2)然后每次对采样时钟相位加1/16,即选择DLL的一个相邻输出,直到数据沿变化为“010”的中间沿,此时记下移相次数counter1。

3)重复上述移相过程直到得到左边沿“100”,同样记下移相次数counter2。

4)最终计算出采样时钟移相位(counter1+counter2)/2。

3. 3 字同步电路

图5为并行数据字同步框图,包括一个移位计算模块和一个基于流处理的异步FIFO。

每个通道数据相位调整完成后给出BitRdy信号,字同步模块即可以对数据进行处理。字同步同样会用到训练数据的跳变沿,且以“0011”为同步字,例如,当接收到并行数据是“0001”时则移位计算模块会将数据向左移一位。

当每个通道都计算出移位数后会产生WrdRdy,将所有通道的WrdRdy作逻辑与处理得到AllRdy信号,如图5所示。

图5 字同步电路Fig.5 Word synchronization circuit

当AllRdy有效且同步字到来时将数据存入到异步FIFO中,对于异步FIFO的读信号则在AllRdy有效至少一个周期同时在将FIFO写满之前有效,因此理论上本字同步方法能够纠正的周期偏差在于FIFO深度,即将FIFO写满的周期数。

4 仿真结果分析

采用文中设计的高速接口方法,在中芯国际(SMIC)的0.13μm工艺上,已经设计实现了双向10 Gb/s传输速率的高速接口芯片。

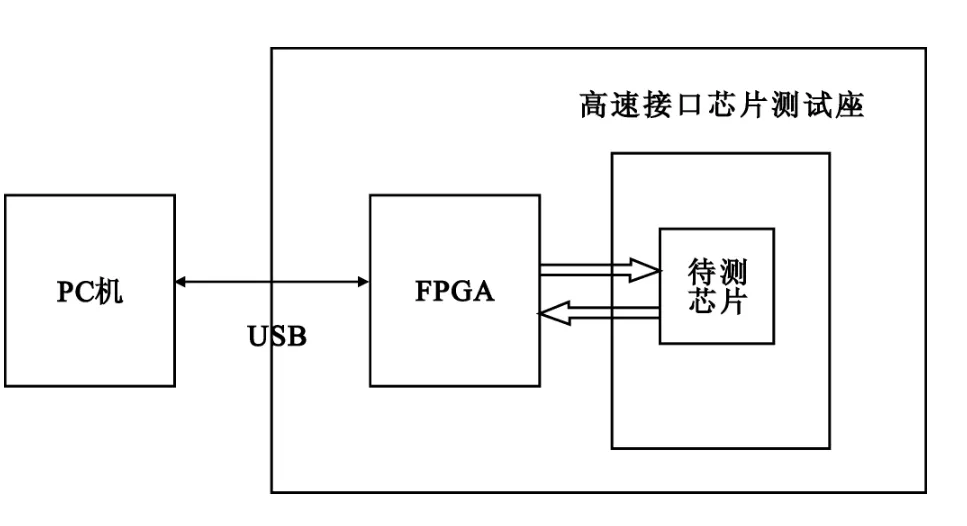

为验证文中设计的高速接口方法的正确性,设计了高速接口芯片专用测试板,如图6所示。

图6 测试板框Fig.6 Test circuit diagram

1)用FPGA对接所设计的高速接口芯片。

2)用PC机通过USB接口,与FPGA通信。

3)由FPGA发起数据传输,将内置于FPGA内的待处理数据,分成大数据包,通过FPGA发送给高速接口芯片的10G数据接收口(其中数据总线16位,时钟320 MHz,DDR采样方式,传输带宽达10 240 Mb/s,即10.24 Gb/s,超过了10 G光纤信道接口规范要求的10 Gb/s)。

4)高速接口芯片接收到FPGA发送的数据后,进行算法运算处理。

5)运算结果通过高速接口芯片的10 G数据发送口输出给FPGA。

6)FPGA接收高速接口芯片发送的运算结果,与FPGA内置的理想结果对比,如一致则证明在传输过程中没有发生数据错误。

7)因数据量较大,循环使用FPGA内置的数据来实现接口上的大数据量传输。

8)一旦有一个数据包发生数据错误,FPGA将出错信息通过USB接口发给PC机报警。

经48小时实际测试,高速接口芯片连续传输数据无错误产生。

该设计方法已用于某款“核高基”高速芯片,该芯片经过第三方测试机构测试证明接口性能超过双向10 Gb/s,并以成功应用于10 G SDH光纤信道设备。

5 结语

文中首次公开披露利用国内流片厂商IP,结合自行设计的控制和同步逻辑,可以实现双向10 Gb/s数据接口的方法。

文中研究内容基础上,今后将通过扩展数据位宽、提高接口随路时钟频率等方法,进一步提升接口带宽,实现10 Gb/s以上,甚至40 Gb/s的高速数据接口。

[1] IEEE1596.3 ,1996[S].USA:IEEE.

[2] WAKERLY J F.Digital Design:Principles and Practices[M].Third Edition.NJ,USA:Prentice-Hall,2000.

[3] 陈春章,艾霞,王国雄.数字集成电路物理设计[M].北京:科学出版社,2008:60.

CHEN Chun-zhang,AI Xia,WANG Guo-xiong.Digital Integrated Circuit Design[M].Beijing:Science Press,2008:60.

[4] 唐杉,徐强,王莉薇.数字IC设计-方法、技巧与实践[M].北京:机械工业出版社,2006:50.

TANG Shan,XU Qiang,WANG Li- wei.Method,the Design of Digital ICSkills and Practice[M].Beijing:Machinery Industry Press,2006:50.

[5] 王彬,任艳颖.数字IC系统设计[M].西安:西安电子科技大学出版社,2005:22.

WANG Bin,REN Yan-ying.Digital IC System Design[M].Xi'an:Xi'an Electronic and Science University press,2005:22.