基于ARM11的电源完整性分析

2014-09-23黄西,徐晓

黄 西,徐 晓

(华南理工大学 理学院,广东 广州 510641)

基于ARM11的电源完整性分析

黄 西,徐 晓

(华南理工大学 理学院,广东 广州 510641)

为了解决高速多层PCB的电源完整性问题,缩短其开发周期,提高其工作性能,以ARM11核心系统为例,提出利用Cadence PI对PCB进行电源完整性分析的方法。通过对电源系统目标阻抗分析,确定去耦电容的数值,数量以及布局;对电源平面进行直流压降和电流密度分析,改善PCB设计,优化系统的电源完整性。利用动态电子负载搭建的测试平台,对电源仿真分析后制作的PCB进行测试,系统电源完整性较好,表明分析的结果是有效的。关键词:电源完整性;目标阻抗;Cadence PI;ARM11;S3C6410

随着现代高速信号的速率越来越快,信号边缘越来越陡,芯片的供电电压的进一步降低,时钟频率和数据读取速率的增加要求消耗更多的电能,在进行电子系统信号完整性分析研究的同时,如何提供稳定可靠的电源给电子系统也已成为重点研究方向之一[1]。电源完整性工程的分析方法和实践目前还处在不断探索的阶段,利用仿真技术,在满足加工制造与测试条件的总体方案和设计准则下,在产品设计早期尽可能地解决电源完整性问题,能最大限度地降低产品成本,缩短研发周期[2]。目前,一些EDA工具提供相应的电源完整性(Power Integrity, PI)仿真分析功能,其中Allegro 提供良好的交互工作接口,和它前端产品Cadence、Orcad、Capture紧密结合,为当前高速、高密度、多层的复杂 PCB 设计提供了最完美解决方案[3]。文中采用 Allegro中的组件Cadence PI对ARM11[4]核心系统进行了电源完整性分析,并对PCB板进行电源完整性的测试,验证仿真分析的结果。

1 电源完整性理论分析

1.1 电源分配系统的概念

在电子系统中,电源子系统的作用是为所有器件提供稳定的电压参考和足够的驱动电流,因此,电源电路和功能电路之间应该是低阻抗的电源连接和接地连接。一个理想的电源系统,其阻抗为0,在平面任何一点的电位都是恒定的,但实际电源系统具有复杂的寄生电容和电感,而且供电芯片所提供的供电电压也非理想的恒定值。

电源分配系统(Power Distribution System, PDS)由目标阻抗,电压调节模块(Voltage Regulator Module, VPM),电源/地平面、去耦电容与高频陶瓷电容组成。

电源完整性问题是指高速系统中的电源分配网络在不同频率下,有不同的输入阻抗,导致电源/地平面上存在由噪声电流ΔI 和瞬态负载电流ΔI '引起的电压抖动ΔV。这个电压波动,一方面影响平面为数字信号提供稳定的电压参考,另一方面会使提供的电源电压抖动,影响器件工作性能。当平面电压波动超出器件的容忍范围时,会造成系统不能正常工作。电源分配系统设计的关键是目标阻抗Z,其定义如式(1)[5]:

式中,Vdd为芯片电源电压,ripple为系统允许的电压波动,ΔImax为负载芯片的最大瞬态电流变化量。电源系统的目的在于能够在有限的反应时间内,以恒定的电压值提供足够的驱动电流,因此需要有足够低的电源阻抗。

1.2 解决电源完整性的方法

电压调节模块,电源/地平面、去耦电容与高频陶瓷电容在不同频率范围内对电源分配系统的阻抗起决定性作用。在1KHz到几Hz 低频段,电压调节调整输出电流以调节负载电压;几MHZ到几百MHZ中频段,电源噪声主要是由去耦电容和PCB的电源/地平面对来滤波;在1 GHz以上高频部分,电源噪声主要是由PCB的电源/地平面对和芯片内部的高频电容来滤波。在做电源完整性仿真的时候,真正有意义的频段主要是在几MHZ到几百MHZ这个频段[6]。目前解决电源完整性问题的途径主要有以下两个方面:

一是优化PCB的叠层设计和布局布线。在高速PCB 设计中通常采用整块铜层作为电源/地平面,尽可能减小输入阻抗。电源和地平面可以看作是一个平面电容,特别是在低中频阶段,等效串联电阻,等效串联电感很小,具有良好的去耦滤波特性[7]。综合前期信号完整性所做阻抗匹配和目前的生产标准,合理的设置层间间距,选择合适的板间电容值,可以很好的改善高速设计的电源完整性。电源和地平面的电容值可以估计为式(2)[8]:

式中,ε0=8.854 pF;εr=4.5(FR-4材料标定值);A为电源层铺铜面积(m2);d为铺铜电源层之间的间隔(m)。根据仿真结果可知,较小平面电容C拥有更高的阻抗响应曲线和更高的谐振频率。

二是布置去耦电容。这是目前最有效的解决电源完整性问题的途径。在高频系统中,电源分配系统中的寄生电感不能忽略,它直接导致电源分配系统的阻抗增加。由于电容与电感在频域具有相反特性,因此可以采用添加电容的方法来减小由于电感导致的阻抗增加。同时,电容具有储能效应,能以极快的速度响应变化的电流需求,所以它能有效改善局部区域内电源的瞬态反应能力。如何选择合适容值的电容、以及确定电容恰当的摆放位置,使电源分配系统阻抗在PCB系统的整个工作频率范围内都小于目标阻抗成为解决电源完整性问题的关键。借助Cadence PI 可以快速地确定去耦电容的容值、数量和摆放位置,提高开发效率。

2 电源完整性仿真

2.1 ARM11核心系统

文中以Cadence PI为仿真工具,对ARM11核心系统进行电源完整性分析,本文中的ARM11核心系统采用S3C6410芯片。S3C6410是一款ARM11体系架构,FBGA封装,需要多电源工作的芯片。本文中该芯片有2个工作电压:核心供电电源1.2 V ,有26个电源引脚(10个核心电源引脚,16个逻辑电源引脚);输入/ 输出接口供电电源3.3 V ,有30个I/ O电源引脚。芯片内部的工作频率是667 MHz ,外部存储器输入/ 输出接口工作频率是266 MHz。ARM11核心系统采用8层层叠结构,在信号仿真阻抗匹配和生产标准的前提下,设定层间间距。本文利用Cadence PI对ARM11核心电压电源网络VDD_ARM进行电源完整性仿真。

由S3C6410芯片数据手册可知,核心电流消耗是200 mA,加上100%的容限,系统允许的电压波动值取4%,核心电压1.2 V,根据式(1),在仿真中设定目标阻抗为0.12 Ω。

2.2 电源完整性仿真

2.2.1 单节点仿真,分析验证并优化电容选择

在单节点仿真中,忽略电源系统中各元件实际的物理连接,假设电源调压模块VRM、仿真激励源、电流源和所有电容都并联在一起,单结点仿真可以得到维持目标阻抗所需要的电容。VDD_ARM电源网络单节点仿真结果如图1所示,所有电容有效时(下面曲线)和所有电容无效(上面曲线) 电源分配系统的阻抗,目标阻抗(中间直线)。最后选择0603贴片封装,150 pF电容4个,390 pF电容3个,0.1μF电容3个,4.7 μF电容2个。

图1 单节点仿真结果Fig. 1 Simulation results of the single-node

2.2.2 多节点仿真,放置去耦电容优化布局

由于单节点仿真没有考虑去耦电容的布局,为了获得更精确的结果,考虑噪声源和去耦电容的放置位置,在全频率范围内进行多节点仿真。在多节点仿真时, Cadence PI根据用户定义将电源平面分隔成多个网格,并对每一个网格进行建模,然后将放置的去耦电容、电压调节模块VRM和噪声源与具体的网格点连接起来,产生每一个节点的频率-阻抗仿真波形。

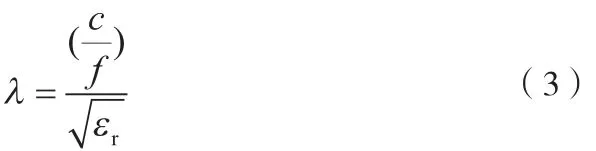

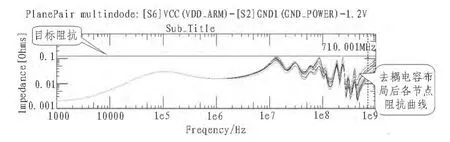

为获得较高的精确度,网格尺寸大小必须大于系统最高频率对应波长的1/10。波长 计算如式(3)[9]:

本系统最高频率为667 MHz,电路板材料是FR-4,介电常数为εr=4.5。由式(3)计算得到λ为212.033 mm。VDD_ARM电源平面为80 mm×70 mm,选择4 4可精确分析,为了便于分析,本文选择8 8的网格。放置电容时,电容的有效去耦半径是一个比较重要的参数,根据经验数据,这一半径在实际应用中的取值最好小于λ/50[10]。不断进行多节点仿真,使得所摆放的电容数目最小化。图2为VDD_ARM/地平面对多节点的仿真结果。从结果可知,在放置相应的去耦电容之后,除极个别点外,平面阻抗在小于710 MHz的范围内都是小于目标阻抗的,而ARM11核心系统的最高时钟频率为667 MHz,因此此次去耦电容的布局完全满足要求。

图2 多节点的仿真结果Fig. 2 Simulation results of the multi-node

2.2.3 电源平面静态IR-Drop直流压降分析

芯片要正常工作需将供电电压限定在允许的波动范围之内。电源波动是由DC损耗和AC噪声两部分造成的,直流压降DC IR-Drop是产生DC损耗的主要原因。静态IR-Drop直流压降主要与金属连线的宽度及所用层、该路径所流过的电流大小、过孔的个数和位置有关。在Cadence PI中设置电源供给管脚和灌电流后,对布局布线完成后的ARM11核心供电电压网络VDD_ARM进行直流压降分析,当ARMll核心系统工作频率为667 MHz时,其1.2 V的直流电压的允许波动幅度为+/-0.05 V。Cadence PI仿真软件计算出VDD_ARM网络电压梯度,其中Drop的最大值为0.013 V,小于允许波动的幅度为+/-0.05 V,完全满足S3C6410工作电压要求,可以保证系统工作的稳定性。

2.2.4 电源平面电流密度分析

当电源平面上过孔过多或者分布不合理时,会出现电流流过狭窄区域,从而造成该区域电流密度过大。电源平面上最大的电流密度区域称之为热点,热点有可能会导致严重的热稳定性问题,因此要合理地设计过孔,使板的电流密度分布均匀,避免在关键芯片和高速走线附近出现热点。图3为VDD_ARM网络电流密度分布,图中标注点为该平面热点,其位置周围为一块空白区域,平面其他部分电流密度较均匀。

图3 VDD_ARM电流密度Fig. 3 Current density of VDD_ARM

3 PCB电源完整性测试

在第1版PCB中,没有利用Cadence PI分析,只是根据经验放置了一些去耦电容。在调试时,发现高速数字信号的波形不好,有时会有误码。在第2版中,通过Cadence PI进行分析,对去耦电容的数值数量和位置,部分原件的布局布线进行了调整。

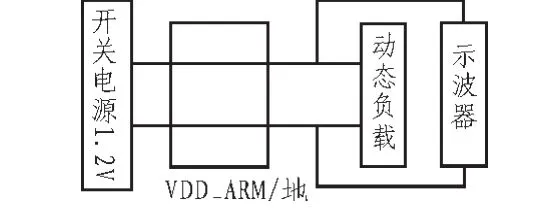

利用动态电子负载模拟高速电子线路中多芯片同时切换时所造成的系统供电电流的高速周期性突变,对ARM11核心系统的PCB板搭建如图4所示的测试平台,分别对第1版安装了去耦电容PCB,第2板没安装去耦电容和第2板安装了去耦电容的VDD_ARM/地电源平面对进行测试。

图4 测试平台框图Fig. 4 Schematic of test environment

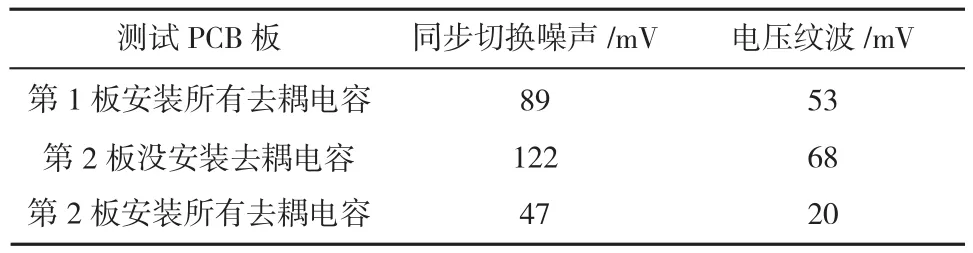

开关电源1.2 V为电源平面提供0.2~0.8A左右的输出电流,动态负载在恒压的情况下,输出阻抗周期变化,电流幅度可完成同周期的0.2~0.8 A的跳变,测试数据如表1。从数据可看出经过Cadence PI分析后生产的第2版PCB的电源完整性得到较大幅度的改善。

表1 测试数据Tab.1 Test data

4 结 论

经过Cadence PI的仿真分析后,制作出ARM11核心系统PCB板,通过电路实际测量,发现各电源分配系统均能很好工作,与仿真结果基本一致。随着系统频率高速增加,电源分配系统复杂化,工程生产成本和周期的严格控制,在设计电子系统时,于系统层面进行电源完整性仿真分析、模拟真实系统的行为,对提高设计效率、减少设计误差很有必要。

[1] ERIC Bogatin.Signal and Power Integrity-Simplified[M].USA:Prentice Hall PTR,2009.

[2] 李钰峰.高速电源完整性研究[D].北京:北京邮电大学,2012.

[3] Anon.Product description of Allegro[EB/OL].[2013-05-16]http://www.allegromicro.com/.

[4] 冯新宇. ARM11嵌入式Linux系统实践与应用[M]. 北京:机械工业出版社,2012.

[5] 周景润,苏良碧.Cadence 高速电路板设计与仿真[M].4版.北京:电子工业出版社,2011.

[6] 邵鹏.高速电路设计与仿真分析:Cadence 实例设计详解[M].北京:电子工业出版社,2010.

[7] 周子琛,申振宁.高速嵌入式系统中的电源完整性设计方法[J].单片机与嵌入式应用,2010,(3):19-21.

ZHOU Zi-chen,SHEN Zhen-ning.Power integrity de sign in high speed embedded system[J].Microcontrollers & Embedded Systems,2010(3):19-21.

[8]申伟,唐万明,王杨.高速PCB的电源完整性分析[J].现代电子技术,2009(24):213-218.

SHEN Wei,TANG Wan-ming,WANG Yang.Analysis of Power Integrity for High-speed PCB[J].Modern Electronic Technology.2009(24):213-218.

[9] 张木水.高速电路电源分配网络设计与电源完整性分析[D].西安:西安电子科技大学,2009.

[10] 白同云.高速PCB电源完整性研究[J].中国电子科学究研院学报,2006(1):22-30.

BAI Tong-yu.Research into High speed PCB power integratio[J]. Journal of CAEIT, 2006(1):22-30

Power integrity analysis based on ARM11

HUANG Xi, XU Xiao

(School of Sciences, South China University of Technology, Guangzhou 510641, China)

In order to solve the problem of the integrity of the power supply of high speed multilayer PCB, shorten the development period and improve its working performance, this paper puts up with the analytical method of PCB power integrity based on the ARM11 core system, using Cadence PI. The decoupling capacitor parameter, quantity and corresponding layout can be determined by analyzing the target impedance of the power system. It is possible to improve the PCB design, optimize the power integrity of the system by analyzing the DC power drop and ampere density of the power plane. The test of the PCB, which is made after the power supply simulation using the dynamic electronic load test platform, reveals the the analysis is effective.

power integrity; target impedance; Cadence PI; ARM11; S3C6410

TN86

A

1674-6236(2014)03-0153-03

2013–06–21 稿件编号:201306132

黄 西(1985—),女,重庆梁平人,硕士研究生。研究方向:机器视觉与人机工程。