频率合成技术的发展及应用

2014-09-23张献中

张献中,张 涛

(武汉科技大学 信息科学与工程学院,湖北 武汉 430081)

频率合成技术的发展及应用

张献中,张 涛

(武汉科技大学 信息科学与工程学院,湖北 武汉 430081)

本文基于对目前频率合成技术的横向比较,详细介绍了频率合成技术的历史、现状;介绍并分析了几种主要频率合成技术的基本原理,最后,介绍了频率合成技术数字化、集成化和软件化。本文对全面了解频率合成技术具有非常重要的实际应用价值。

频率合成器;PLL;DDS;芯片;FPGA

频率合成技术是用一个或数个高频率稳定度的参考频率源,通过频率域的线性运算产生多个与参考频率稳定度相同或接近的新频率的技术。频率合成技术不但能提高通信频率和通信设备的稳定度、准确度,而且还能满足通信自动化对频率可控和存储的要求,以及抗干扰对快速跳频的要求。在通信、雷达和导航等设备中,频率合成器既是发射机的激励信号源,又是接收机的本地振荡器;在电子对抗设备中,它可以作为干扰信号发生器;在测试设备中,可作为标准信号源,因此频率合成器被人们称为许多电子系统的“心脏”。

1 频率合成技术的发展

频率合成技术最早开始于上个世纪30年代,发展至今,已经比较成熟,主要有以下几类,分别为:直接模拟频率合成、锁相式频率合成、直接数字频率合成和混合频率合成。

1.1 直接模拟频率合成技术

直接模拟频率合成技术是一种早期的频率合成技术,它用一个或几个参考频率源经谐波发生器变成一系列谐波,再经混频、分频、倍频和滤波等处理产生大量的离散频率,直接模拟频率合成技术简单易行、频率转换时间短、相位噪音低,但因采用了大量的分频、混频、倍频和滤波等模拟元件,使合成器的体积大、易产生杂散分量、元件的非线性影响难以抑制。

直接频率合成法的优点是工作可靠,频率转换速度快,相位噪声低,缺点是需要大量的混频器、分频器和滤波器、且难以集成化,所以体积大,价格也贵,目前已基本不用。

1.2 锁相式频率合成技术

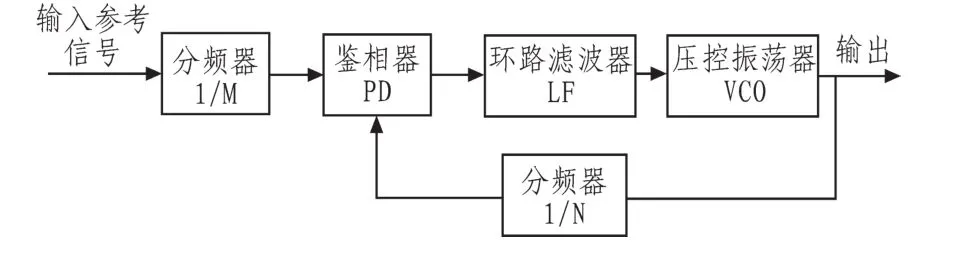

锁相式频率合成器[1]是采用锁相环(Phase-Locked Loop,PLL)进行频率合成的一种频率合成技术。PLL是一个能够跟踪输入信号相位的闭环自动控制系统,它通常由鉴相器(Phase Detector,PD)、环路滤波器( Loop Filter,LF)、压控振荡器(Voltage Controlled Oscillator,VCO)和两个分频器等几部分组成。锁相环组成的原理框图如图1所示。

图1 锁相式频率合成器基本原理图Fig. 1 PLL frequency synthesizer basic schematic

锁相环频率合成器的工作原理是:输出信号频率与外部参考频率进行相位比较,由误差相位θe(t)产生误差电压ud(t),误差电压经过环路滤波器F(p)的过滤得到控制电压uc(t),控制电压加到压控振荡器上使之产生频率偏移,来跟踪输入信号频率ωi(t)。若输入ωi为固定频率,在uc(t)的作用下,ωv(t)向ωi靠拢,一旦达到两者相等时,若满足一定条件,环路就能稳定下来,达到锁定。锁定之后,被控的压控振荡器频率与输入信号频率相同,两者之间维持一定的稳态相位差。

PLL主要分为3类:模拟PLL、数字PLL和数模混合PLL。若在锁相环中插入数字分频器和数字鉴相器,即成为数字锁相环;数字锁相频率合成技术是目前的主流技术。数模混合PLL又叫电荷泵锁相环CPPLL(Charge Pump PLL),它的组成既有模拟电路也有数字电路。电荷泵锁相环与模拟锁相环相比,具有无限的捕获范围和跟踪范围,捕获时间短,线性范围大,成本低等优点,得到广泛的应用。目前单片集成频率合成器锁相环几乎全部采用电荷泵锁相环。

1.3 直接数字合成技术

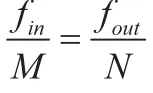

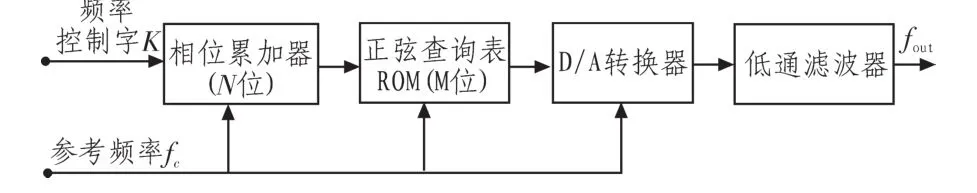

近年来,随着微电子技术的迅速发展,直接数字频率合成器(Direct DigitaI Freguency Synthesis 简称 DDS)得到了飞速的发展。DDS的基本结构包括[3]:相位累加器、正弦查询表ROM、数模转换器DAC和低通滤波器LPF等。其基本框图如图2所示。

图2 DDS基本原理图Fig. 2 DDS Basic Schematic

相位累加器PA (Phase Accumulator)在K位频率控制字FCW(Frequency Control Word)的控制下, 以参考时钟频率关为采样频率,产生待合成信号的数字线性相位序列,将相位累加器的高N位作为地址码通过正弦查询表ROM变换, 产生M位对应信号波形的数字序列, 再由数模转换器DAC将其转化为阶梯模拟电压波形,最后由低通滤波器 LPF将其平滑为连续的正弦波形作为输出, 这就是DDS 的基本工作原理。

该DDS系统的核心是相位累加器,它由一个加法器和一个位相位寄存器组成,每来一个时钟,相位寄存器以步长增加,相位寄存器的输出与相位控制字相加,然后输入到正弦查询表地址上。正弦查询表包含一个周期正弦波的数字幅度信息,每个地址对应正弦波中 0~360° 范围的一个相位点。查询表把输入的地址相位信息映射成正弦波幅度的数字量信号,驱动DAC,输出模拟量。相位寄存器每经过2N/K 个时钟 后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS系统输出一个正弦波。

由上可知 , DDS技术可以理解为数字信号处理中信号综合的硬件实现问题,即给定信号幅度、频率、相位参数,产生所需要的信号波形。从系统的角度可以认为是给定输入时钟和频率控制字K,输出一一对应的正弦信号。由于DDS采用了不同于传统频率合成方法的全数字结构,所以DDS技术具备了直接模拟频率合成和间接频率合成方法所不具备的许多特点:

由于DDS中几乎所有部件都属于数字电路,易于集成,功耗低、体积小、重量轻、可靠性高,且易于程控,使用相当灵活,因此性价比极高。但DDS也有局限性,主要表现在:

1)输出频带范围有限 受器件速度(特别是DAC)的限制,使得工作时钟频率fc较低,DDS不能直接运用于微波频段,这也是DDS的主要缺点之一;2)杂散抑制差 DDS全数字结构带来了许多优点,但正是由于这种结构以及寻址ROM时采用的相位截断、DAC位数有限等决定了DDS的杂散抑制较差。

通过以上3种频率合成技术的分析,我们可以简要总结出各自的性能特点[4]。如表1所示。

表1 三种频率合成器的性能比较Tab.1 Performance comparison of the three frequency synthesizer

1.4 混合频率合成技术

根据PLL和DDS的特点可知,PLL频率合成技术具有高频率、宽带、频谱质量好的优点,但是其频率转换速度低。而DDS技术则具有高速频率跳变能力、频率和相位分辨率高,但在设计电路时经常要在带宽、频率精度、频率转换时间、相位噪声等要求中折衷考虑。因此,出现了多种将两种技术结合起来构成DDS与PLL混合技术实现频率合成的方案[5],DDS+PLL频率合成就是以DDS作为PLL的参考源驱动PLL的一类混合型频率合成技术。DDS有输出步长小而又有较高相噪的优点,但同时又有杂散较多的缺点。而PLL在输出步长小时,相位噪声差,但它对杂散的抑制性能良好。所以DDS与PLL两种频率合成技术结合起来,取长补短,相得益彰,是一种非常合理的频率合成解决频率合成技术的性能指标。

DDS+PLL混合频率合成的方案主要有DDS激励PLL组合以及DDS与PLL混频组合两种。

1.4.1 DDS激励PLL频率合成器系统

DDS激励PLL是目前最简单和最常用的频率合成组合方案[6],将PLL设计成N倍频环, DDS输出通过带通滤波器BPF后直接作为PLL的参考信号,此处加入的带通滤波器是为了抑制DDS的宽带频率杂散。这个DDS组合PLL的频率合成方法,是将DDS作为PLL的参考源来驱动PLL,系统稳定性高,结构简单易实现,可以实现较高的频率输出,具有很高的分辨率,在N不太大时,相位噪声和杂散都可以较低,充分体现了DDS+PLL组合系统的优越性。另一方面,由于DDS输出端的带通滤波器无法滤除通带内的杂散,在PLL将DDS输出频率N倍频的同时,这些杂散将会被放大,这对系统频谱纯度有一定影响。DDS激励PLL系统原理图如图3所示。

图3 DDS激励PLL系统原理图Fig. 3 DDS Incentive PLL System Schematic

由此可知,DDS激励PLL组合系统的输出频率fOut为:fOut=N×fDDS,通过程序控制改变DDS输出频率或PLL倍频系数N就可以改变输出频率。输出频率分辨率fd=N×fDDSd,其中fDDSd为DDS的频率分辨率。

1.4.2 DDS内插PLL频率合成方案

DDS内插于PLL环路,将DDS的输出与PLL中的反馈分量相混频,经过N分频后作为鉴相器的参考输入,通过改变DDS的输出频率来改变鉴相器的鉴相频率,最终达到控制系统输出频率的目的[7]。该方案的优点是:DDS没有参与倍频,因此杂散和相位噪声的倍频恶化问题对系统的影响比较小,其他优点和DDS激励 PLL差不多,理论上能够得到很好的相噪和杂散特性。但是此方案也存在一些缺点:1)如果用于很高频段,则系统中的带通滤波器需要有很好的选择性,从而不易实现;2)如果用于稍低的频段,那么交调分量一旦接近混频输出信号,也将加大滤波器的设计难度。该系统原理图如图4所示。

图4 DDS内插PLL系统原理图Fig. 4 DDS interpolate PLL system schematic

该方案把DDS内插到PLL环内,具体来说就是用DDS的输出和PLL中的反馈分量相混频,然后作为鉴相器的参考输入,通过改变DDS的输出频率,从而改变鉴相器频率,来达到控制系统输出频率的目的。

2 频率合成技术的新进展

2.1 频率合成器芯片

随着微电子技术和计算机技术的飞速发展,频率合成技术从分立元件迅速发展到全集成化,即所有元件集成到一块芯片上。频率合成器的发展趋势是频率更高、系统功能更强、制作工艺更先进、集成度更高、成本更低、功耗更低、系列产品更加完善等。频率合成器在国外已经发展的比较成熟,形成了各种类型的锁相式频率合成器、直接数字频率合成器、双环或多环锁相式频率合成器、DDS与PLL混合式频率合成器等系列产品。

生产频率合成器的国外厂商主要有美国国家半导体(NSC)(已被TI公司收购)、美国模拟器件公司(AD)、德州仪器(TI)、凌特尔特公司(Linear)、Hittite、意法半导体等。

AD公司的ADF41020频率合成器,可以用于无线接收机和发射机的上变频和下变频部分,频率范围达到4~18 GHz,供电电流30 mA。ADF41020提供极高的带宽,设计中无需倍频,从而简化系统框架并降低成本。其工作带宽高达18 GHz,是当今市场上能够提供的最高PLL频率合成器。

美国国家半导体(NSC)公司的用于射频个人通信Δ-∑的低功耗双路PLL频率合成器LMX2487E,频率范围3~7.5 GHz,供电电压2.5~3.6 V。具有集成VCO的PLL频率合成器LMX2541可以实现32 MHz~4 GHz的频率范围。

TI公司的TRF3765频率合成器是一款宽频带整数-N/分数-N频率合成器,此合成器具有一个整数型宽频带压控振荡器(VCO)。可编程输出分配器可实现 300 MHz~4.8 GHz之间的连续频率范围。

凌力尔特公司(Linear) 推出高性能6GH整数 N 频率合成器 LTC6945,该器件具卓越的 -226 dBc/Hz 归一化闭环带内相位噪声、出色的-274 dBc/Hz归一化带内1/f噪声、-157 dBc/Hz的宽带相位噪声层和同类最佳的-102 dBc 杂散输出该器件有一个内置的输出分频器,可从1到6编程,以将调谐频率覆盖范围扩展为低至350 MHz。

2.2 频率合成器的软件实现

随着DSP和FPGA技术的发展,人们运用软件无线电的思想,采用大规模可编程逻辑器件构成锁相环与频率合成器的硬件平台,可以在不改变硬件平台的情况下,采用软件编程的方法实现锁相环的功能[8]。

目前,DDS系统基本上都是采用现场可编程门阵列(FPGA)来实现其数字部分。它不仅具有高速、可靠,内嵌RAM模块,而且可以根据需要方便地把波形存储表内嵌入FPGA中,实现不同波形的灵活设计。在DDS系统中,FPGA主要实现如下功能:1)实现相位累加器;2)波形数据存储的查找表。

3 结束语

文中综述了频率合成技术的发展历史,分析了几种主要频率合成技术的工作原理,也介绍了频率合成技术的最新进展。总之,频率合成技术正向集成化、数字化、软件化、高速化、低成本、低功耗方向发展,这也会使频率合成技术在现代航空,遥控遥测,雷达,通信等电子系统得到更广泛的应用。

[1] 张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,2004.

[2]万天才.频率合成技术发展动态[J].微电子学,2004,34(4):366-370.

WAN Tian-cai. The latest development of frequency synthesizer technology[J].Microelectronics,2004,34(4):366-370.

[3] 吴曙荣.直接数字频率合成器的设计[D].西安:西安电子科技大学,2006.

[4] 张涛,陈亮.现代DDS的研究进展与概述[J].电子产品世界,2008(2):126-129.

ZHANG Tao, CHEN Liang.The summary and research of modern DDS[J].Electronic Engineering & Product World.2008(2):126-129.

[5]杨檍,鲍景富.现代频率合成技术的研究进展[J].电视技术,2007,47(2):344-349.

YANG Yi,BAO Jing-fu. Research progress of frequency synthesis yechniques[J].Telecommunication Engineering,2007,47(2):344-349.

[6] 王轶.基于DDS+PLL技术的高性能频率源研究与实现[D].长沙:国防科学技术大学,2004.

[7] 刘全,高俊.基于DDS+PLL的高速宽带频率合成器的研究[J].无线电通信,2007(4):60-66.

LIU Quan,GAO Jun.Research on frequency synthesizer of high speed and wide band based on DDS Hybird PLL[J].Radio Engineering,2007(4):60-66.

[8] 邱迎锋,刘光斌.频率合成技术:历史、现状及发展[J].工业仪表与自动化装置,2005(5):13-15.

QIU Ying-feng,LIU Guang-bin.Frequency synthesis technology:history,actuality and development[J].Industrial Instrumentation &Automation,2005(5):13-15.

The development and application of frequency synthesis technology

ZHANG Xian-zhong, ZHANG Tao

(Information Science and Engineering, Wuhan University of Science and Techndgy,Wuhan 430081, China)

This paper,based on the horizontal comparison of latest frequency synthesis technology, details the history and current situation of frequency synthesis technology; Presents and analyzes the basic principles of the main frequency synthesis technology; Finally, introduces the digitization、integrated and the software of the frequency synthesis technology. This paper has a very important practical value to comprehensive understanding of the frequency synthesis technology.

frequency synthesizer; PLL; chip; FPGA

TN74

A

1674-6236(2014)03-0142-04

2013–05–14 稿件编号:201305156

张献中(1987—),男,河南南阳人,硕士。研究方向:模拟CMOS集成电路设计。