AXI标准协议在微型机载采集设备中的应用

2014-09-23范秋香吴琼之孙宁霄金兆健

范秋香,吴琼之,孙宁霄,金兆健

(北京理工大学 信息与电子学院,北京 100081)

AXI标准协议在微型机载采集设备中的应用

范秋香,吴琼之,孙宁霄,金兆健

(北京理工大学 信息与电子学院,北京 100081)

本文介绍了AXI片内总线协议规范,指出了其高性能、高带宽、低延迟的特点。针对微型机载采集设备中FPGA设计的难点,本文提出了采用AXI标准总线协议作为采集系统FPGA控制逻辑的结构框架,使得整个采集系统的软件架构具有高度规范性和灵活性,同时兼顾了较高的性能需求,并取得了较好的实用效果。

AXI协议;片上总线;采集系统;FPGA

本文设计的微型机载采集设备用于遥感数据采集,存储以及数据导出。其具有功能多样,外围设备丰富,控制逻辑复杂等特点。选择一种合适的片内总线协议不仅能够极大降低系统设计复杂性,还有利于系统内模块的扩展和移植,此外,一种标准的片上总线协议还便于多人协作编程,缩短系统开发周期。

目前有很多种总线规范,由ARM公司提出的高级微控制器总线架构片上总线规范(advanced micro-controller bus architecture, AMBA)是芯片总线的主流标准。AXI(Advanced extensible Interface)总线协议是AMBA3.0协议中最重要的部分,是一种面向高性能、高带宽、低延时的片内总线,本设计采用AXI标准接口协议作为微型机载采集设备FPGA片内总线协议,在实际应用中取得了良好的效果。

1 AXI总线协议简介

在现代SOC设计中,随着CPU处理能力的大幅提升以及外围设备接口的多样化,如何提高总线的带宽和各个从设备的工作效率成为了提高整个系统性能的关键。ARM公司提出用于SOC设计中的AMBA总线结构由于它的高性能以及ARM微处理器的广泛应用,已经成为了SOC设计中使用相当广泛的总线标准。AXI是AMBA中一个新的高性能协议。AXI协议丰富了现有的AMBA标准内容,满足超高性能和复杂的SOC设计要求,并且能够后向兼容现存的高级高速总线(advanced high performance bus, AHB)和高级外围总线(advanced peripheral bus, APB)接口。

1.1 AXI协议特点

AXI协议的主要特点包括:

1)通道体系结构:5个独立的通道,分别是读地址、写地址、读数据、写数据和写响应通道。地址通道和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提升到最高,并将延时降到最低。信息流只以单方向传输,不仅简化了时钟域间的桥接,而且减少了延时。

2)支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

3)增强的灵活性。AXI拥有对称的主从接口,无论在点对点或在多层系统中,都能十分方便地使用AXI技术。

4)低功耗节电模式。AXI 总线定义了在进出低功耗节电模式前后的握手协议。规定如何通知进入低功耗模式, 何时关断时钟, 何时开启时钟, 如何退出低功耗模式。这使得所有IP 在进行功耗控制的设计时, 有据可依, 容易集成在统一的系统中[1]。

为了提高SOC系统的灵活性,AXI协议定义了3种协议接口:

1)AXI4:内存映射接口,一个地址在一次猝发中最多可进行256个数据传输。

2)AXI-LITE:内存映射接口,一次猝发只传输一个数据。AXI-LITE接口信号是AXI4接口信号的子集,专用于系统上控制指令的通信。AXI-LITE接口信号简单,对设计和验证方面的要求比较少。本文所设计的系统控制指令的传输采用AXI-LITE接口。

3)AXI-STREAM:没有地址通道,非内存映射接口,一次猝发传输的数据量不限。AXI-STREAM接口用于连接进行大量数据交换的模块。本文所设计的系统数据流的传输采用AXI-STREAM接口。

1.2 AXI数据传输

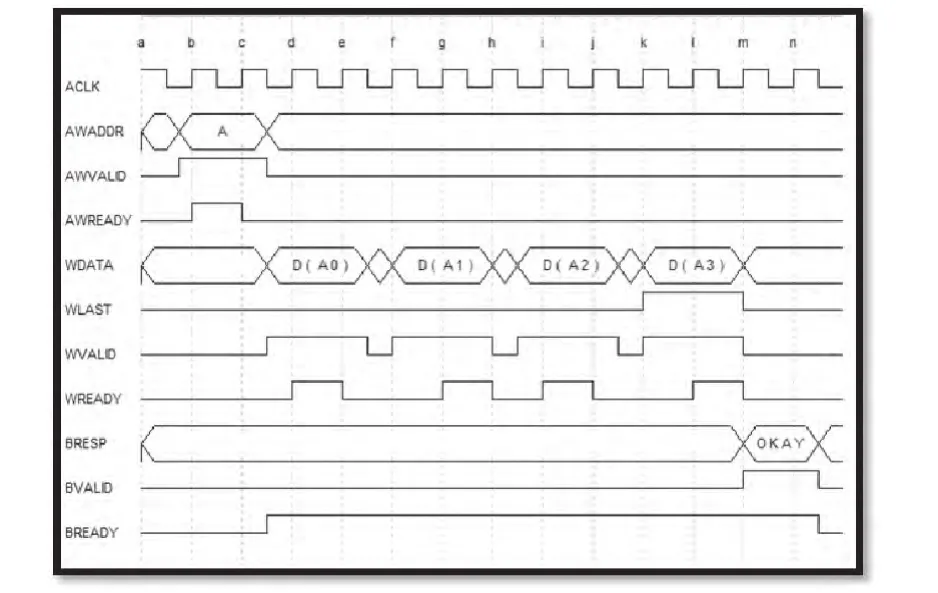

AXI总线实现读写操作要通过5个通道,分别是读地址通道,读数据通道,写地址通道,写数据通道,写响应通道。数据在一个master(主模块)与一个slave(从模块)之间传输,如果数据是从master到slave,则在一个写数据通道上,如果数据是从slave到master,则在一个读数据通道上。每个通道上均存在握手信号(VALID, READY),仅当握手成立的情况下,该通道上的信号才有效。图1表示AXI总线写数据过程写地址、写数据和写响应3条通道的数据流向[2-3]。

图1 写地址、写数据和写响应通道Fig. 1 Write address, write data and write response channel

图2 AXI总线写数据时序图Fig. 2 Write timing diagram of AXI bus

图2显示了AXI总线写数据时序。master(主设备)首先通过写地址通道发送地址。接着通过写数据通道发送写数据。当master发送最后一个数据时,WLAST信号变高。slave(从设备)接收完所有的数据后,向master返回写响应信号(OKAY),表明写传输完成。

2 基于AXI总线的微型机载采集系统设计

2.1 系统概述

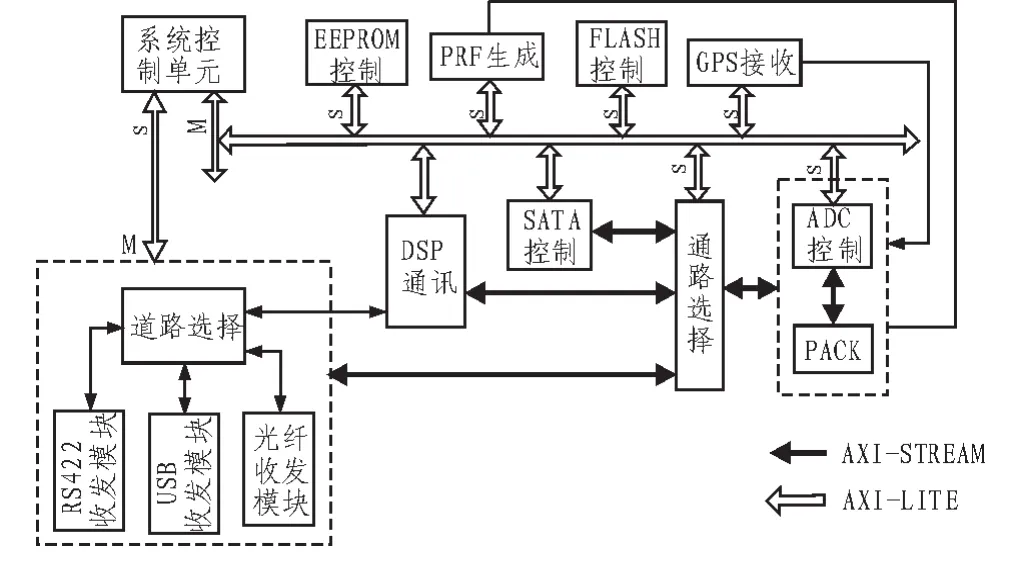

图3为本文所设计的微型机载采集设备系统框图。

图3 微型机载采集设备系统框图Fig. 3 System block diagram of mini airborne acquisition device

系统具备以下功能:

采集状态下,以一定的速率采集系统前端模拟信号,同时通过RS232接口接收GPS信号,采集的数据和对应的实时GPS信息封装成固定格式存储在系统的固态存储器中。

系统具备3种存储介质:FLASH存储介质用于存储FPGA程序,系统上电后可自动往FPGA中加载程序;SATA存储介质具有高速存储和导出数据的功能,用于存储采集数据和GPS信息;EEPROM存储介质用于存储一些系统信息,如SATA存储器可用存储空间、已用存储空间等信息。

通过4种接口与上位机之间进行数据传送:USB接口、RS422接口、光纤接口和以太网接口。这四种接口不仅能将系统存储介质中的数据传送到上位机,还能接收上位机传给采集系统的控制指令。系统与上位机连接时,上位机能够对各个模块进行状态查询,控制采集系统进行数据的导出,此外,上位机还能够清除采集系统存储介质中的数据以便系统重新采集记录[4]。

系统的主要数据流向如下:

采集过程:(AD+RS232串口)→FPGA→ATA存储器;

数据读出过程:SATA存储器 /EEPROM存储器→FPGA→上位机通信接口。

2.2 系统FPGA程序设计

FPGA是本系统的主控模块,完成数据采集存储和数据读出功能,产生相应的时钟和控制信号,实现多种接口协议。本设计采用Xilinx公司的Virtex5系列FPGA,Xilinx公司提供一套丰富的IP核资源,设计时直接调用能够极大的降低系统设计复杂性。

本文设计的采集系统具有以下特点:1)功能多样:系统具备采集、存储和回传数据功能,同时支持多种接口与上位机通信。2)外围设备丰富:包括SATA存储器,EEPROM存储器,FLASH存储器,ADC芯片,GPS芯片,DSP处理器,每种设备接口各异,采集系统需要将这些接口各异的设备集成在一片SOC上。3)控制逻辑复杂:当系统与上位机连接时,采集系统的主控制器为上位机;当模块脱离上位机时,采集系统的主控制器为FPGA处理器。主控制器需能够有效控制采集系统众多接口各异的外围设备协调、有序工作[5]。

以上特点给FPGA程序设计带来了极大的困难,寻求一种高性能的片上总线标准协议成为简化FPGA程序设计的关键。一种合适的片上总线协议能够有效地将采集系统各个功能模块互连起来,为整个系统解决功能模块间的相互通信问题,从而为设计人员免去大量精力去考虑如何将各个功能模块连接起来,有利于多人协作开发,缩短系统开发周期。

本设计采用AXI标准协议作为FPGA片上总线协议。系统中控制指令通过AXI-LITE接口传输,数据流通过AXISTREAM接口传输。Virtex5 FPGA提供了基于AXI-LITE接口和AXI-STREAM接口的FIFO的IP核,设计时可直接调用以降低系统设计复杂度[6]。图4为系统FPGA程序结构图。

图4 采集系统FPGA程序结构框图Fig. 4 FPGA program architecture of acquisition system

系统的硬件设计采用功能模块化的思想,即根据硬件功能将系统分解成多个模块,各模块之间既相对独立又相互关联,如此不仅便于系统调试又有利于系统功能扩展。

上位机通讯单元用于实现模块与上位机间通过RS422通路、USB3.0通路、光纤通路通信,模块内部包含RS422、USB以及光纤收发模块,上位机通讯单元可根据上位机与采集系统实际的物理连接选择正确的通路。当采集系统与上位机连接时,上位机通信单元是FPGA程序的主控模块。

系统控制单元是FPGA程序的核心单元,可根据其内部的预置信息,自动向FPGA上除上位机通讯单元外的其他模块发送指令,控制各个模块协调、有序工作,当上位机与系统连接时,该模块能够被上位机控制,接收上位机的指令控制采集系统工作。

AD采集单元负责控制ADC芯片工作,接收AD采集数据和GPS信息,在PRF脉冲到来时将二者封装成固定格式转存到SATA存储器。

PRF生成单元生成采集系统所需的PRF脉冲。

通路选择单元用于控制FPGA内部数据流方向,当系统进行数据采集时,将AD采集单元的数据包转存到SATA存储器,当系统进行数据导出时,将SATA存储器内部数据传送到上位机通信单元。

DSP通讯单元用于实现FPGA与DSP的通信。EEPROM控制单元,SATA控制单元和FLASH控制单元分别用于控制EEPROM存储器、SATA存储器和FLASH存储器工作。

2.2.1 控制指令传输

系统控制指令通过AXI-LITE接口传输,FPGA程序中包含以下两组AXI-LITE接口:

1)master:上位机通信单元,slave:系统控制单元。

2)master:系统控制单元,slave:SATA控制模块,AD采集单元,GPS接收模块,EEPROM控制模块,PRF脉冲生成模块,DSP通讯模块,FLASH控制模块。表1给出了AXILITE接口的信号。

表1 AXI-LITE接口信号Tab.1 Signal of AXI-LITE interface

系统与上位机连接时,上位机通信单元作为FPGA处理器内部mater,通过第一组AXI-LITE接口控制采集系统,包括选择采集系统与上位机的连接通路,读取系统各个模块的状态,导出和清空采集系统的存储数据等。系统脱离上位机时,系统控制单元作为FPGA处理器内部的master,通过第二组AXI-LITE接口控制采集系统进行信号采集和存储。

FPGA片上的各个模块对应不同的地址值,读写操作均由master模块发起。master模块传输控制指令时,分别通过写地址通道和写数据通道发出相应寄存器的地址值和控制指令, slave模块接收到控制指令后发出写完成信号并通过写响应通道传回master模块。读寄存器时,master模块通过读地址通道发出寄存器的地址值,slave模块接收到读地址后通过读数据通道返回寄存器值。所有的控制指令均由master模块发出。

由以上分析可以看出,采用AXI-LITE标准接口作为控制信号接口能够有效将系统各个模块连接起来,简化模块间的控制关系。此外,采用AXI-LITE接口还有利于系统模块的扩展和移植。当系统需要移入新的模块时,只需将模块接口转化为AXI-LITE标准接口并给模块分配新的地址即可直接连在系统的AXI总线上。

2.2.2 数据流传输

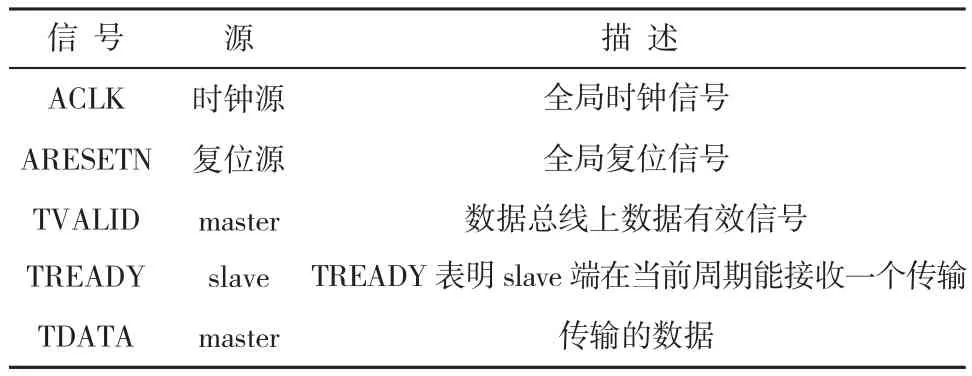

模块间数据流的传输通过AXI-STREAM接口进行,表2给出了AXI-STREAM接口的信号。

AXI-STREAM接口没有地址通道,数据流源端为master,数据流终端为slave,数据只能从master到slave单向传输,与AXI-LITE接口一样,一个master可与多个slave相连,当master和多个slave相连时需加入总线仲裁电路。

表2 AXI-STREAM接口信号Tab.2 Signal of AXI-STREAM interface

数据流传输时采用READY和VALID双向握手机制,当READY和VALID同时有效时进行一次数据传输。采用双向握手机制能够有效控制数据流传输的速度。

3 结束语

综上所述,采取AXI标准总线作为采集系统FPGA内部总线协议使系统便于设计,能够有效解决FPGA程序设计过程中遇到的困难。AXI标准协议信号简单,可以很容易被各个不同模块所采用,控制信号和数据流采用不同的AXI标准接口传输有利于提高系统的数据传输效率。AXI总线从技术上讲简单、灵活、功能强大,它的广泛应用将把SOC设计推向一个新的台阶。本文设计的采集系统工作稳定,已经在某微型机载遥感探测系统上得到应用。

[1] 蒋国良,权进国,林孝康.AMBA总线新一代标准AXI分析和应用 [J].微计算机信息,2006(29):46.

JIANG Guo-liang, QUAN Jin-guo,LIN Xiao-kang.analysis and application of new generation AMBA 3 AXI protocol [J].Microcomputer Information,2006(29):46.

[2] ARM Co.AMBA AXI Protocol specification,REV2.0[EB/OL].(2010).http//www.arm.com.

[3] ARM Co.AMBA 4 AXI4-Stream Protocol Specification,REV1.0[EB/OL].(2010).http//www.arm.com.

[4] 马明建. 数据采集与处理技术[M]. 西安:西安交通大学出版社,2012.

[5] 田耕,胡彬,徐文波,等.Xilinx ISE Design Suite 10.X FPGA开发指南[M].北京:人民邮电出版社,2008.

[6] XILINX Co. AXI Reference Guide[EB/OL].(2012). http//www.xilinx.com.

Application of AXI bus interface protocol in mini airborne acquisition device

FAN Qiu-xiang,WU Qiong-zhi,SUN Ning-xiao,JIN Zhao-jian

(School of Information and Electronics, Beijing Institute of Technology, Beijing 100081, China)

This paper introduces AXI Bus Interface Protocol, and points out its high performance, high bandwidth and low-latency characteristic. According to the difficulty in FPGA design in mini airborne acquisition device, this paper puts forward a solution that using AXI bus interface protocol as FPGA control logic architecture. This solution makes the software architecture of the acquisition system highly normative and flexible. It meets high performance demand and achieves good practical effect.

AXI protocol; on-chip bus; acquisition system; FPGA

TN705

A

1674-6236(2014)03-0062-04

2013–06–03 稿件编号:201306015

范秋香(1989—),女,福建莆田人,硕士研究生。研究方向:高性能电路技术与信号处理技术。