基于CPLD的FSK调制解调电路及其测试

2014-09-19武立华赵恩铭刘志海

武立华,黄 玉,王 姣,赵恩铭,刘志海

(哈尔滨工程大学a.理学院 理学之光科技创新中心;b.信息与通信工程学院,黑龙江 哈尔滨 150001)

基于CPLD的FSK调制解调电路及其测试

武立华a,黄 玉a,王 姣b,赵恩铭a,刘志海a

(哈尔滨工程大学a.理学院 理学之光科技创新中心;b.信息与通信工程学院,黑龙江 哈尔滨 150001)

根据数字式FSK调制和解调的工作原理,对比分析了基于CPLD和单片机的2种电路实现方案.设计了基于CPLD的FSK调制解调模块,利用QuartusⅡ开发平台对CPLD进行编程,实现了FSK调制与解调功能,用IAR FOR AVR平台对单片机ATMEGA16进行编程,实现了位同步功能,同时与外部用SPI接口进行通信.搭建了实际的硬件电路,仿真与实验测试均验证了设计的正确性.

FSK调制解调;CPLD;单片机;位同步

1 引 言

数字调制解调技术是现代通信的重要研究内容之一[1].在数字通信系统中,由于基带数字信号包含了丰富的低频部分,如果要远距离传输特别是在有限带宽的高频无线或光纤信道传输时,必须对数字信号进行载波调制,把基带信号的功率谱搬移到较高的载波频率上.FSK利用数字信号调制载波的频率,是信息传输较早的一种传输方式,具有抗噪声性能好、传输距离远、误码率低等优点,在衰落信道的中低速数据传输中有着广泛的应用.近年来,国内外的学者和一些公司在为调制与解调器的研究和推广方面做出了很多的努力,在蓝牙通讯设备、医学植入微电子器件和便携式消费电子产品等方面己有大量的研究成果.FSK的调制与解调可以用单片机实现,也可用CPLD实现.若采用单片机实现方案,单片机资源的占用率比较高,对ATMEGA16单片机来说,每隔1/300 ms时间就得产生1次中断[2].由于单片机把大部分时间用来处理中断,则在调制与解调过程中,容易发生抢中断,使系统工作不稳定.单片机的端口操作频率最多只有1 MHz,产生的FSK信号波特率也不会很高.一般的CPLD端口的操作频率可达120 MHz,基于CPLD的FSK调制解调系统能达到较高的波特率,且CPLD内部程序并行运行,不会存在争抢资源情况.因此采用CPLD实现FSK调制与解调.

2 系统实现方案

2.1 调制方案

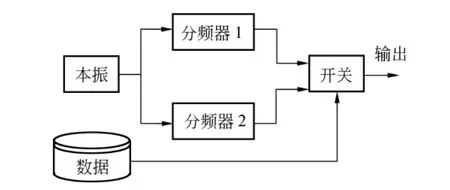

采用CPLD产生FSK信号的原理框图如图1所示,系统时钟作为调制用的本振信号由1个10 MHz的有源晶振提供,本振信号通过分频器1得到载波f1,输入时钟经分频器2得到载波f2,2个载波与1个选通开关(2选1数据选择器)相连,选通开关根据数据选通相应频率的载波.当数据为“1”时选通f1,输出频率为f1的载波;当数据为“0”时选通f2,输出频率为f2的载波,完成载波频率的选择,产生FSK信号.

图1 基于CPLD的FSK调制原理框图

2.2 解调方案

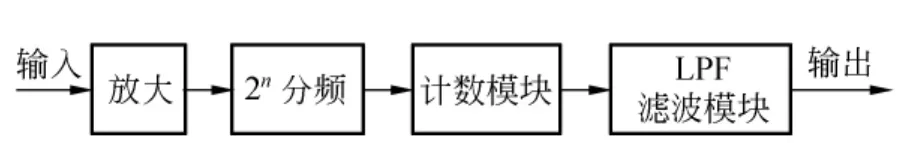

基于CPLD的FSK解调采用过零检测法[3-8],它是一种既经济又实用的数字解调方法,与其他解调方法相比有如下特点:结构简单,易于实现,对增益起伏不敏感,特别适用于数字化实现.基于CPLD的FSK解调方框图如图2所示,利用信号波形在单位时间内与零电平轴交叉的次数测定信号频率.解调电路系统接收模拟信号,经过前置电路进行限幅放大等信号处理,去掉幅度信息,最后由CPLD识别并加以解调.分频模块负责脉冲展宽;计数整流模块进行边沿检测;LPF模块为低通滤波器,低通滤波器滤出待判决基带信号.这样就完成了FSK信号的解调.

图2 基于CPLD的FSK解调原理框图

2.3 整体方案

基于CPLD的FSK调制解调整体方框图如图3所示,一共有电源、前置信号处理、CPLD与单片机控制等4个模块.采用1片MAX II系列CPLD实现调制与解调功能,器件型号为EPM240,其内部拥有240个逻辑单元,典型等效宏单元为192,最大用户管脚80个,用户Flash存储器8 192字节,速度等级3~5 ns.采用ATMEGA16单片机作为控制器.由于单片机的串行口本身就是数字通信系统,自带异步位同步功能,采用ATMGEA16的串口,可把得到的解调信号还原成数字信号,省去CPLD的位同步功能,且留出1个SPI接口与外部进行通信.

图3 FSK调制与解调的系统方框图

在调制过程中,单片机通过串口TXD向CPLD发送串行数据,串行数据包含了起始位、停止位和1位奇偶校验位.CPLD将从TXD得到的基带信号进行调制,得到FSK信号,再经过缓冲电路发射出去.解调过程正好与调制过程相反,接收到的FSK信号先经过前置信号处理模块进行限幅放大,放大的FSK信号输入CPLD进行解调,而后通过TXD交给单片机,再由单片机的串口进行位同步,将数据提取出,由SPI接口与外部进行通信.

3 系统软件设计

3.1 调制模块设计

利用VHDL程序设计的FSK调制模块逻辑结构如图4所示,接口信号规定如下:

1)clk是FSK调制的载波信号,采用10 MHz有源晶振,在上升期间进行计数,内部的三位计数器对10 MHz的时钟信号进行计数,实现8分频和4分频.

2)data数据信号输入端,即基带信号的输入端.

3)fsk_out是FSK调制信号的输出端.调制模块的选择开关使得当data为高电平时,fsk_out与内部的4分频信号相连接,当data为高电平时,fsk_out与内部的8分频信号连接,实现了FSK调制.

图4 FSK调制模块

3.2 解调模块设计

图5 FSK解调程序框图

解调程序框图如图5所示,解调模块是FSK调制解调中最重要和最复杂的模块.FSK信号在CPLD中先进行4分频得到信号S1,这样做的目的是降低信号频率,让解调出的数据更稳定.同时系统内有8位计数器对10 MHz系统时钟进行计数,在S1上升沿将计数值赋给寄存器1,并产生1位标志位.根据要求的信号,分别把寄存器1的值分别赋值给寄存器2和寄存器3.软件自动根据标志位判断寄存器2和3数据的时间前后,相减计算出信号周期T0,如果T0<T1,输出高电平,如果T0≥T1,输出低电平.

FSK解调模块如图6所示.

图6 FSK解调模块

4 实验测试

4.1 软件仿真

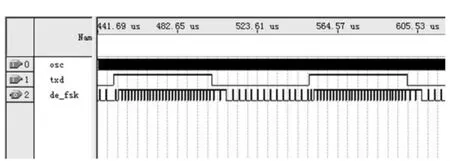

仿真软件为QuartusⅡ开发平台,打开波形仿真程序,把相应的引脚波形加入仿真程序.运行结果见图7,图中osd为10 MHz时钟输入,txd为数据输入端口,fsk_out为FSK调制输出.

从图7可以看出,当数据为“1”时,FSK输出频率为2.5 MHz,当数据为“0”时,FSK输出频率变为1.25 MHz,表明调制模块工作正常.

图7 FSK调制模块仿真图

QuartusⅡ的波形仿真程序不能直接加入FSK信号,为产生FSK信号直接把调制模块的输出加到解调模块的FSK信号输入端,把所有引脚加入波形仿真程序,进行仿真.运行结果如图8所示,图中osc为10 MHz系统时钟输入,txd为FSK调制模块的输入信号,调制模块的调制信号在内部与FSK解调模块输入端相连,de_fsk为解调输出信号.

由图8可知,解调出的信号与输入的信号相同,FSK解调模块工作正常.但由于在解调过程中出现了竞争冒险,因此解调出的信号有很多毛刺,为使解调出的信号不会在位同步时产生误码,必须在解调电路后附加滤波模块以消除毛刺.

图8 FSK解调模块仿真图

4.2 实际测试

4.2.1 调制解调器测试

FSK调制与解调系统的实际电路如图9所示,由2块CPLD电路板构成,1块用作FSK调制,另一块用作FSK解调,2块电路用三芯排线相接.

图9 基于CPLD的FSK调制与解调电路

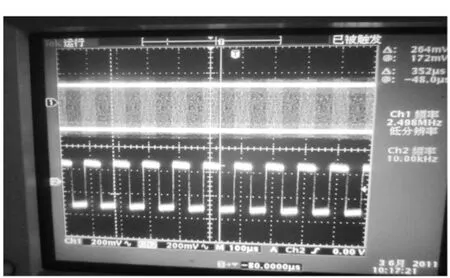

信号源的输出设置成频率为10 k Hz,幅值为3.3Vp-p,直流偏置为1.65 V 的方波信号,加入CPLD基带信号输入端.示波器的一个通道测量FSK调制的输出,另一通道测量FSK解调经滤波器后的输出.得到的FSK调制解调结果如图10所示,图中通道1为FSK调制的信号,通道2为经CPLD解调与滤波后的信号,解调出的数据与调制信号相同.另外,从解调出的数据波形可知,解调输出端加上一级截止频率为40 k Hz的RC滤波器后,信号变得很平滑.

图10 FSK调制解调的测试结果

4.2.2 串行通信与功能测试

测试系统如图9所示,把ATMEGA16单片机插入电路板,通过单片机的串口向FSK调制器发送串行数据,由另一块相同电路板的FSK调制器进行解调,并通过串口与电脑相联,在串口不同的波特率下,测试调制解调的误码率,测试结果如表1所示.

表1 在串口不同波特率下调制解调的误码率

经测试,基于CPLD的调制信号最高可工作在15 k Hz,表明基于CPLD调制解调系统的波特率最高可实现30 kb/s,工作速度由单片机SPI与USART的交换速度决定.为了保证在高速下发调制与解决数据的正确性,需要在串口发射时,开启奇偶校验,并在程序中进行冗余码校验,如果发现有错误,可以重新发送.

5 结 论

对比分析了FSK调制解调的单片机与CPLD两种实现方法,提出了基于CPLD的FSK调制与解调的整体方案.设计了基于MAXⅡ系列CPLD的全数字FSK调制解调电路,对调制解调系统的各模块进行了软件设计及仿真验证.实际电路测试表明,基于MAXⅡ系列CPLD的FSK调制解调器结构简单、可靠性好,具有较强的抗干扰能力.

[1] 方彦军,孙军,朱小平.基于MSP430的FSK调制解调器[J].仪表技术与传感器,2008(7):60-61,64.

[2] 张克飞,周智鑫,苏照杰,等.基于单片机的自动寻迹摄像小车[J].应用科技,2011,38(11):75.

[3] Bassel F,Chalres L.Asynchronous classification of MFSK signals using the higher order correlation domain[J].IEEE Transactions on Communications,1998,46(4):480-493.

[4] 应亚萍,许建凤,陈婉君.2FSK调制解调系统的FPGA设计与实现[J].浙江工业大学学报,2010,38(3):282-285.

[5] Rosti A V,Koivunen V.Classification of MFSK modulated signals using the mean of complex envelope[J].Proc.EUSIPCO,2000:581-584.

[6] Le B,Rondeau T W,Maldonado D,et al.Modulation identification using neural networks for cognitive radios[A].SDR05 Technical conference[C].Phoenix,2005.

[7] Mobasseri B G.Constellation shape as a robust signature for digital modulation recognition[J].IEEE Conf.of Military Communications,1999,1:442-446.

[8] Hsue S Z,Soliman SS.Automatic modulation classification using zero crossing[J].IEEE Proc.Radar and Signal Processing,1990,137(6):459-464.

[9] Arulampalam G,Ramakonar V,Bouzerdoum A,et al.Classification of digital modulation schemes using neural networks[J].IEEE Proc.Signal Processing and Its Applications,1999,2:649-652.

[责任编辑:郭 伟]

FSK modulation and demodulation circuit based on CPLD and its test

WU Li-huaa,HUANG Yua,WANG Jiaob,ZHAO En-minga,LIU Zhi-Haia

(a.Science of Optical Science and Technology Innovation Center,College of Science;b.College of Information and Communication Engineering,Harbin Engineering University,Harbin 150001,China)

According to the working principle of digital FSK modulation and demodulation,two kinds of circuit schemes based on CPLD and single chip were compared.FSK modulation and demodulation module based on CPLD was designed and programmed by Quartus II software.ATMEGA16 single chip was programmed by IAR FOR AVR software to carry out the function of bit synchronization and communication with outside through SPI interface.Both simulations and experimental tests proved the exactness of design.

FSK modulation and demodulation;CPLD;single chip;bit synchronization

TP212

A

1005-4642(2014)04-0019-04

2013-06-21;修改日期:2013-12-25

国家自然科学基金资助(No.61004130);中国博士后科学基金资助(No.2012M511446,2013M530145);中国博士后科学基金特别资助(No.2013T60348);中央高校基础科研业务费专项资金资助(No.HEUCF2013)

武立华(1979-),女,吉林松原人,哈尔滨工程大学理学院讲师,博士,从事精密测量技术方面的研究.