基于简化电阻电容电路的单粒子效应应用研究

2014-09-15王天琦张民选肖立伊

邓 全,王天琦,李 鹏,张民选,肖立伊

(1.国防科学技术大学计算机学院,湖南 长沙 410073;2.哈尔滨工业大学航天学院,黑龙江 哈尔滨 150006)

基于简化电阻电容电路的单粒子效应应用研究

邓 全1,王天琦2,李 鹏1,张民选1,肖立伊2

(1.国防科学技术大学计算机学院,湖南 长沙 410073;2.哈尔滨工业大学航天学院,黑龙江 哈尔滨 150006)

随着器件尺寸缩小至纳米级,微观粒子对半导体器件的影响变得越来越明显。器件可靠性的研究近年来逐渐引起了人们的重视,开展了很多相关研究。以研究单粒子翻转效应为核心,在传统混合仿真的基础上,采用简化RC电路模型对简化电路的应用进行研究,总结了电阻和电容值变化对等效电路中敏感节点处电学特性变化的规律,探究了使用Id-Vd曲线判断单粒子翻转的准确性,提出了在研究临位翻转时,通过单次实验即可有效预测临位翻转情况的方法。根据实验所得的电压电流曲线图形特点对它们进行分类,从而判断临位翻转。通过模拟实验与预测结果比对,两者的结果相符,预测有较高准确性。

单粒子效应;软错误;简化电阻电容电路模型;临位翻转预测

1 引言

随着电子技术和空间科技的发展,微电子器件尺寸逐渐缩小,面临辐射环境的时间逐渐增多,原本忽略不计的效应产生的影响越来越大。研究单粒子效应变得更加重要,对单粒子效应的研究逐渐成为一个热点[1,2]。

单粒子效应研究方法有很多,如全3D仿真、混合仿真以及电路仿真。各种方法的优缺点不同,在全3D仿真中仿真结果与实验结果最相符合,结果准确,而电路仿真仿真时间相对较快,但实验结果误差较大。相比于之前的方法,简化RC(Resistor-Capacitor)电路结构模型具有效率高、仿真时间少、实验结果准确、电路结构简单的优点。但是,相比于传统电路,它的相关研究开展较少,缺乏面对多样应用环境的使用方法和判断相关效应的标准。由于简化RC电路和传统电路存在细节差异,并不是所有传统电路的判断标准以及研究方法都适用于简化电路。针对这一问题,本文以简化RC电路为基础,综合各方面研究论述已有的简化电路应用标准,总结规律,提出了在复杂环境下适用简化电路更有效的判断方法。

2 简化RC电路简介

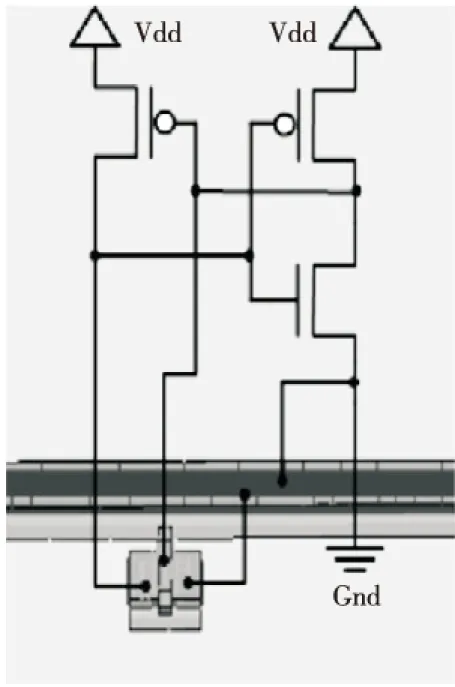

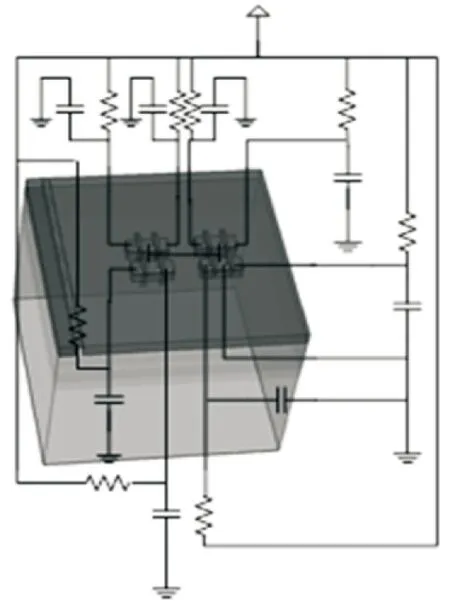

以基本4管SRAM存储单元为例,对简化RC电路[3]进行说明。传统的仿真结构如图1所示,使用简化电路的结构如图2所示。在这个例子中,仅对单个反相器NMOS管漏极进行粒子轰击[4],所以将其他三个MOS管等效为电阻和电容。发生单粒子翻转的情况下,以敏感期间器件的漏电流和漏电压为对比量,考察了两个电路的等效性。其中漏电流与时间的变化关系如图3所示。

Figure 1 Mix simulation of SRAM unit图1 SRAM单元混合仿真示意图

Figure 2 Simplified RC circuit mode图2 简化RC电路模型示意图

通过实验总结漏区电流电压随电阻值和电容值的变化规律如下:

电阻值越小,漏区电流峰值越大,电阻值变化对电流峰值影响不是很明显,一般调节10倍的关系才能看出电流变化。电阻值越小,漏区电压的谷值越高,电阻值变化对电压谷值的影响显著。这种现象的出现是由于当单粒子碰撞效应发生的时候,漏区产生的脉冲电流是一定的,所以漏区上半部分电阻和电压成正比,电阻值越小,电压越小,在漏区节点的电压值越大。

Figure 3 Current of drain in intrinsic circuit and simplified circuit图3 简化电路和原有电路漏区电流对比

改变电容值对漏区电压谷值的影响很小,但是电压恢复速度变快了。改变电容值对漏区电流峰值的影响显著,电容值越小漏区电流越小。

利用这两个规律,通过调节电容值来匹配脉冲电流峰值,调节电阻值来匹配漏区电压谷值的方法已达到匹配两种电路的目的。

建立好简化RC电路后,进行模拟仿真,相比于普通混合模拟而言,仿真时间缩短为原来的1/3,而仿真结果基本一致,测量临界LET(Linear Energy Transfer)值的误差在0.1%~0.2%。

3 简化电路单粒子翻转判断方法

3.1 电路抗辐照能力评估

在常规电路中一般使用单粒子翻转效应SEU(Single Event Upset)截面积 (σ=Ν/Φ)进行判断。通常是测量翻转截面σ(每单位通量所测到的翻转个数)随有效能量线性传递(离子的线性能量传输值除以入射束流表面夹角的余弦值)的变化关系曲线来表示某器件的抗单粒子能力。

3.2 现有单粒子翻转判断方法及改进

3.2.1 平稳效应

简化电路模型中出现了平稳效应[5],在简化RC电路中截止NMOS管的漏区电流时会在电流脉冲之后出现一段平稳的电流,通过实验对比发现,当发生单粒子翻转效应时有平稳阶段,当没有发生单粒子效应时不会出现平稳阶段。

图4显示了在RC电路中在三个不同LET值下漏极电流随时间变化的曲线。在混合仿真电路中,当LET=0.3 MeV·cm2/mg时,电路状态未发生翻转;当LET=5 MeV·cm2/mg时,两种电路状态发生了翻转。如图4所示,在简化电路中,漏电流随时间的变化在LET=5 MeV·cm2/mg时出现了平稳态,由此看出,平稳阶段可以作为存储单元翻转的一个指示器。但是这种方法存在一个不准确的地方,就是临界LET值下也不会出现平稳效应。混合仿真电路测出截止NMOS管的临界LET值为0.5 MeV·cm2/mg,在这个LET值下截止管恰好没发生翻转,而图4中在LET为0.5 MeV·cm2/mg的简化电路中漏区电流还是出现了平稳效应。

Figure 4 Steady effect in simplified circuit图4 简化电路平稳效应图

3.2.2 封闭曲线法

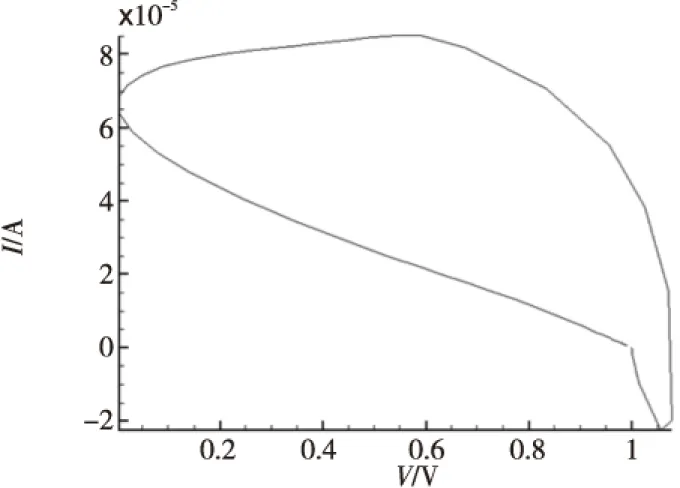

在混合仿真的情况下,可以利用Id-Vd曲线图是否封闭来判断状态是否发生翻转。在简化电路中仍然可以利用这对变量来考察,不过判断的方法发生了改变。

在传统电路仿真中,漏区电流会产生一个脉冲,最终电流值会恢复到0 mA;而输入和输出电压在发生单粒子碰撞之后,也会恢复到初始值。观察Id-Vd曲线变化特性,可以看出当未发生单粒子翻转效应的时候,在Id-Vd曲线中会呈现一个如图5所示的封闭圆圈;反之,当发生单粒子翻转效应时,漏区电流的变化情况基本保持一致,输入和输出电压不会恢复到初始状态,而是变成相反的极性,所以在Id-Vd曲线中不会产生封闭的圆圈,出现的是一个开放式曲线。第一个被破坏的环形就是临界LET值。如图5所示为各个LET值下的图形变化规律。

在简化电路中,输入和输出电压不管在哪种情况下都会恢复到原来的初始电压,所以在Id-Vd电压曲线中形成封闭环形,也就不会有被破坏的临近曲线,所以需要找到一个标准来帮助判断SEU是否发生了。在图5中画出的临界线,可以被看成是一个界线。这个曲线是混合仿真电路发生临界翻转时封闭环形沿y轴的切线。从图6中可以看出VD=0.178 V,使用这个切线可判断状态是否发生翻转。对于切线左边的Id-Vd曲线会发生翻转,对于切线右边的Id-Vd曲线不会发生SEU。对比混合仿真的实验结果,临界LET都为0.5 MeV·cm2/mg。

Figure 6 Id-Vd in simplified circuit图6 简化电路中漏极电流电压变化示意图

4 简化电路临位翻转研究

4.1 实验环境

采用8个SRAM单元组成的存储阵列为研究电路环境。由于在多SRAM单元中,每个单元具有相对独立性,所以在单个SRAM单元得到的判断单个位置单粒子翻转效应的结论可以用在多单元结构之中。单粒子打击某个位置的时候可能引起多位翻转[6],对打击点的相邻位置进行考察。

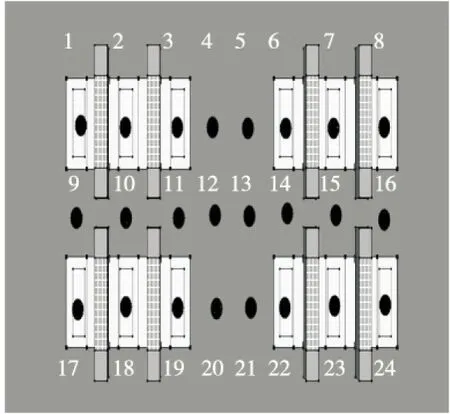

利用TCAD工具绘制90 nm条件下的8个单元的SRAM存储器结构,由于发生单粒子效应的敏感区域是截止管的漏区,所以本文只画出了8个处于截止状态的NMOS管,如图7所示。在此使用截止管NMOS的3D模型,采用了共源区的结构,其中这8个NMOS共用一个P阱,根据单个SRAM单元的连接方法利用简化电路图连接这8个NMOS管。

器件平面为XZ平面,本例沿着Y轴方向垂直入射,入射点均匀分布在器件表面,共计24个节点,其中12个节点位于NMOS器件的源区或者漏区,12个节点位于器件的P阱区。从上到下从左到右定义1~24号入射位置。其中12个入射在器件源区漏区的点一起对比,另外12个入射阱区域的点放在一起对比,如图8所示。

Figure 7 Simplified circuit structure of eight SRAM units图7 八个SRAM单元简化电路等效结构图

Figure 8 Location of gain impacting图8 粒子打击位置示意图

当LET=5 MeV·cm2/mg时,入射1号NMOS管漏区,对比混合仿真和简化电路仿真曲线,在混合仿真中观察到NMOS管发生单粒子翻转,利用简化电路判断标准考察Id-Vd,发现结果一致。这证明在多单元SRAM电路中简化电路一样适用。

4.2 临位翻转判断和预测方法

一般对临位翻转进行判断的时候,需要对单个节点进行多次不同LET值下的打击,然后分别进行测试,直到临位发生翻转才能做出临位发生翻转临界条件及可能性的判断。在此提出在简化电路环境下能有效预测临位是否具有发生翻转的可能性的方法,不需要多个临位的临界翻转条件即可在单次实验中分析临位翻转的可能性,减少了实验次数。由于不需要临界翻转条件这个信息,这种方法可以应用于复杂系统中多位翻转的研究[7],从而减少实验时间。

打击一个位置之后,对各个节点进行Id-Vd曲线测试,多次实验后可以发现曲线呈现规律。

如图9所示,该Id-Vd曲线一般出现在测试点为打击点的时候,采用之前讨论的简化电路判断翻转方法,观察左侧边界与V=0.175 V的位置关系判断翻转情况,如果左侧边界在V=0.175 V左侧则发生翻转,反之没有发生。观察相应SRAM单元输入输出电压,所得结论与判断一致。

Figure 9 First law图9 规律一

如图10所示,该Id-Vd曲线一般出现在测试点为打击点相邻位置的时候。其曲线左边界位于V=0.175 V左边,观察相应SRAM单元输入输出电压,判断出该点发生翻转,即临位翻转。

Figure 10 Second law图10 规律二

如图11所示,该Id-Vd曲线一般出现在测试点为打击点相邻位置的时候。其曲线左边界位于V=0.175 V右边,观察相应SRAM单元输入输出电压,判断出该点没有发生翻转,即无临位翻转。从后续实验可以看出,在打击点和测试点一致的情况下,提高LET值,图11总会转化为图10。

Figure 11 Third law 图11 规律三

如图12所示,该Id-Vd曲线一般出现在测试点为打击点相邻位置的时候。观察相应SRAM单元输入输出电压,判断出该点没有发生翻转,即无临位翻转。后续实验中不管如何提高LET,图形特征都不变,都不会发生翻转。

Figure 12 Forth law图12 规律四

从图10和图11中可以看出,两者的区别仅在于左边界的位置。通过对比实际翻转情况可以说明,在简化电路中判断单粒子翻转和判断临位翻转的标准一致,可以采用同样的方法判断。通过多次实验总结出图10和图11有内在联系,可以通过改变外部条件(如LET值)使其相互转化,即断定有如图10和图11所示的图形特征的点都具有发生临位翻转的可能。这为判断是否具有临位翻转可能性提供了依据。

4.3 预测验证

通过在两个LET值下进行仿真实验,得到不同位置的Id-Vd曲线,根据之前提出的标准进行判断,统计出发生多位翻转的次数。在这里选用两个LET值,LET= 5 MeV·cm2/mg,LET=75 MeV· cm2/mg。在第一种情况下,LET值相对较小,不会发生多位翻转;在第二种情况下,会发生多位翻转。之所以选用第一种情况是想利用上一节提出的图形规律来预测多位翻转的趋势,并与高LET值下多位翻转进行对比。

在第一种情况下LET很小,通过观察图形来进行预测。当这其中的某一个位置发生单粒子碰撞时,可以采用上面提出的规律进行预测,预测出在该位置高LET值下能否引起相应的临位翻转。

以位置10为例,当单粒子碰撞发生在10号位置时,1、3、17、19的Id-Vd曲线,规律符合上述规律中的第三个,说明没有发生单粒子翻转,不过有发生临位翻转的趋势。

观察其他点的Id-Vd曲线,基本图形特征相同,符合上述规律的第四种情况,在环形区域上方有一个尖峰,说明这些位置没有发生状态翻转,而且即使提高LET值在这些位置也不会发生临位翻转。

之后在LET=75 MeV·cm2/mg时,对10号位置进行碰撞仿真,从而对比实际情况和理论估计。根据新标准来比较封闭环形曲线,结果发现当单粒子入射10号位置时,发生了4位翻转,位置是1、3、11、19。与理论估计相一致,证明理论正确。观察低LET值下预测不能发生翻转的位置,图形规律仍然与之前符合,尖峰横跨电压值变化不大。

通过上述分析对比论证,总结预测规律如下:使用简化RC电路在低LET值下进行单粒子碰撞仿真实验,观察各个位置的Id-Vd仿真图形,根据其图形规律与之前的规律对比并归类,得到具体的图形规律。当符合第一种情况时,该位置已经发生了单粒子翻转,并且引起该位置翻转的恰好是该位置的单粒子碰撞;当符合第二条规律时,该位置也发生了单粒子翻转,不过引起该位置翻转的不是该位置的单粒子碰撞而是相邻位置的单粒子碰撞;当符合第三条规律时,该位置尚未发生单粒子翻转,不过该位置在高LET值下具有发生临位翻转的可能性;当符合第四条规律时,该位置没有发生单粒子翻转,在高LET值下也不会发生单粒子翻转。

5 结束语

本文以简化RC电路为基础,对SRAM单元和阵列进行了研究分析,总结了在建立简化电路过程中电阻和电容对相应电学参数的影响规律,确定了判断单粒子翻转效应的标准,找到了判断临位翻转的规律,而且对判断临位翻转的方法进行了优化。当测试临位点Id-Vd曲线符合之前的规律时,根据相应规律判断临位翻转可能性。

简化RC电路中的研究应用不仅仅适用于计算机仿真中也可以用在实物仿真中。由于实体质子发射器等普遍提供的LET值不高,所以在实物中可以利用简化RC电路进行实验。

[1] Xing Ke-fei,Yang Jun, Ji Jin-ming. Radiation effect to SRAM-based FPGA in space[J]. Microelectronics & Computer,2006,23(12):107-110.(in Chinese)

[2] He Chao-hui, Chen Xiao-hua, Li Guo-zheng. Simulation calculation of single event upset effects for high energy protons[J]. Chinese Journal of Computational Physics, 2002,19(4):367-371.(in Chinese)

[3] Castellani-Coulie K, Portal J-M, Micolau G, et al. Analysis of SEU parameters for the study of SRAM cells reliability under radiation[C]∥Proc of LATW’11, 2011 12th Latin American.2011:1-5.

[4] Ethan H.Cannon and manuel cabanas-holmen,heavy Ion and high energy proton-induced single event transients in 90 nm inverter, NAND and NOR gates[J]. IEEE Transactions on Nuclear Science, 2009, 56(6):3511-3518.

[5] Castellani-Coulie K,Toure G,Portal J M,et al.Circuit effect on collection mechanisms involved in single event phenomena:Application to the response of a NMOS transistor in a 90 nm SRAM cell[J]. IEEE Transactions on Nuclear Science, 2011,58(3):870-876.

[6] Correas V, Saigne F, Sagnes B, et al. Prediction of multiple cell upset induced by heavy ions in a 90 nm bulk SRAM[J]. IEEE Transactions on Nuclear Science, 2009,56(4):2050-2055.

[7] Rezgui S, Won R, Tien J. SET characterization and mitigation in 65-nm CMOS test structures[J]. IEEE Transactions on Nuclear Science,2012,59(4):851-859.

附中文参考文献:

[1] 邢克飞,杨俊,季金明.空间辐射效应对SRAM型FPGA的影响[J].微电子学与计算机,2006, 23(12):107-110.

[2] 贺朝会,陈晓华,李国政.高能质子单粒子翻转效应的模拟计算[J].计算物理,2002,19(4):367-371.

DENG Quan,born in 1989,MS candidate,his research interests include radiation effect and hardness technology.

王天琦(1983-),男,黑龙江哈尔滨人,硕士,研究方向为集成电路辐射效应。E-mail:wangtianqilove@126.com

WANG Tian-qi,born in 1983,MS,his research interest includes radiation effect of integrate circuit.

李鹏(1986-),男,吉林吉林人,博士,研究方向为集成电路辐射效应与加固技术。E-mail:li1986p@163.com

LI Peng,born in 1986,PhD,his research interests include radiation effect and hardness technology.

张民选(1954-),男,湖南邵阳人,教授,博士生导师,研究方向为高性能计算机系统和微电子技术。E-mail:mxzhang@nudt.edu.cn

ZHANG Min-xuan,born in 1954,professor,PhD supervisor,his research interests include high performance computer system, and microelectronics technology.

肖立伊(1960-),女,黑龙江哈尔滨人,博士,教授,博士生导师,研究方向为集成电路可靠性。E-mail:xiaoly@hit.edu.cn

XIAO Li-yi,born in 1960,PhD,professor,PhD supervisor,her research interest includes reliability of integrate circuits.

Single event effects applied research based on a simplified resistor-capacitor circuit

DENG Quan1,WANG Tian-qi2,LI Peng1,ZHANG Min-xuan1,XIAO Li-yi2

(1.College of Computer,National University of Defense Technology,Changsha 410073;2.School of Astronautics,Harbin Institute of Technology,Harbin 150006,China)

As technology scales down to nanometer, the effect of microscopic particles on semiconductor devices becomes more and more influential. In recent years, studies of device reliability gradually attract the attention of people and a lot of researches are carried out. The paper pays attention to the effect of Single Event Upset and uses the simplified RC circuit model to study the application of simplified circuit on the basis of traditional simulation. It also summarizes the law of resistance and capacitance values that changes the electrical properties at the sensitive node electrical properties of the equivalent circuit and explores the accuracy of SEU estimation using curveId-Vd. A method of predicting the adjacent position upset in single test is proposed. According to the characteristics of experiments’Id-Vdcurve, a prediction can be made by classifying them. Simulation results are compared with the prediction results, proving that they are the same and the prediction is accurate and valid.

SEU;soft error;simplified RC circuit;prediction of adjacent position upset

2013-08-06;

2013-10-27

国家自然科学基金资助项目(60970036);教育部博士点基金资助项目(20124307110016)

1007-130X(2014)03-0420-06

TN405

A

10.3969/j.issn.1007-130X.2014.03.008

邓全(1989-),男,吉林长春人,硕士生,研究方向为集成电路辐射效应与加固技术。E-mail:dq19890723@126.com

通信地址:410073 湖南省长沙市国防科学技术大学计算机学院学员5队

Address:Team 5,College of Computer,National University of Defense Technology,Changsha 410073,Hunan,P.R.China