基于动态目标阻抗的DDR3电源完整性仿真

2014-09-15李晋文曹跃胜肖立权

李晋文,曹跃胜,胡 军,肖立权

(国防科学技术大学计算机学院,湖南 长沙 410073)

基于动态目标阻抗的DDR3电源完整性仿真

李晋文,曹跃胜,胡 军,肖立权

(国防科学技术大学计算机学院,湖南 长沙 410073)

DDR3存储器已经成为目前服务器和计算机系统的主流应用,虽然DDR3采用双参考电压、片上校准引擎、动态ODT、fly-by拓扑以及write-leveling等技术在一定程度上提高了信号完整性,但高数据率DDR3的设计实现仍然比较困难。由于DDR3总线属于高速并行总线,同步开关噪声与电源本身的噪声耦合在一起,共同影响数据信号的质量。考虑到芯片实际工作电流并非恒定不变,而是一种动态变化的频率相关源,提出了一种新的基于目标阻抗与动态目标阻抗的混合仿真与设计流程,在前仿真阶段采用恒定目标阻抗,在后仿真阶段采用动态目标阻抗为设计目标,仿真结果证实了该方法的有效性,实现了设计优化速度与精度的权衡折衷。

DRR3 DIMM;电源完整性;动态目标阻抗

1 引言

当前计算机系统中已经普遍使用了高带宽的DDR3存储器。与DDR2相比,DDR3具有更高的性能、更低的功耗,最高目标速率达1.6 Gbps[1],市场上主流的DDR3 DIMM产品有1 066/1 333/ 1 600 Mbps。DDR3并行总线接口电路电压采用1.5 V,接口电压的降低导致系统噪声容限减小,时钟周期的进一步缩短,使得系统设计对信号质量、接口时序和噪声容限等方面的要求越来越高,使得芯片I/O、封装以及PCB板级设计都面临巨大挑战[2,3]。

为了获得更好的信号完整性,DDR3采用了串推(fly-by)拓扑结构,减少了链路上的分支(stub)反射,但却引起了内存颗粒之间数据采样信号DQS与时钟信号的时延偏差(skew),为降低实现难度,采用写均衡(write-leveling)技术来调整控制器内部延迟偏斜(skew),从而达到控制时延的目的。即使如此,高频率高带宽DDR3存储系统的设计实现还是比较困难,仍然需要细致的信号完整性和电源完整性仿真。文献[3]全面比较了DDR3和DDR2,分析了DDR3实现的难点;Chuang Hao-hsiang等人[4]通过对DDR3 DIMM信号完整性仿真,发现内存颗粒采用细线连接的fly-by拓扑是设计成功的关键之一;文献[5]应用统计与瞬态的混合仿真方法分析了GDDR3系统I/O的同步开关噪声SSN(Simultaneous Switch Noise)问题。由于DDR3总线属于高速并行总线,除串扰之外,总线中同组数据I/O同时翻转产生的噪声与电源本身的噪声耦合在一起,即同步开关噪声(SSN),共同影响数据信号DQ以及数据采样信号DQS的质量,因此电源完整性对DDR3总线的影响相当大。

目前的电源完整性仿真流程通常是给定电源噪声容限,反推出一个恒定的电源设计目标阻抗,并以此为优化目标,通过优化PCB板叠层中的电源平面、电源过孔数目、电源岛的形状、电源走线的线宽以及去耦电容的类型、数目和位置来实现设计优化目标[6]。前述的电源完整性仿真流程,通常没有考虑芯片供电电流的动态变化对于电源阻抗的影响,可能会导致过设计。考虑到芯片实际工作电流值并非恒定不变,而是一种动态变化的频率相关源,本文提出了一种新的基于目标阻抗与动态目标阻抗的混合仿真与设计流程,在前仿真阶段采用恒定目标阻抗,在后仿真阶段采用动态目标阻抗为设计目标,实现设计优化速度与精度的统一。

本文首先建立了供电网络模型,分析了电源完整性问题的根源—同步开关噪声,比较了电源目标阻抗与动态目标阻抗的定义以及对于信号质量的影响;然后介绍了所提出的基于目标阻抗与动态目标阻抗的混合仿真与设计流程,对DDR3系统的电源进行了仿真优化设计,给出了仿真的实验结果,并对实验结果加以了分析;最后,对本文进行了总结。

2 供电模型

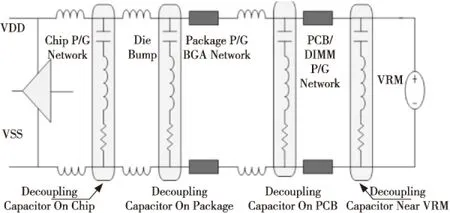

如图1所示,电源分配网络PDN(Power Distribution Network)由系统外配电网络出发经PCB电源分配网络(含VRM,Voltage Regulator Module)、封装电源分配网络,最终通过芯片内部分配网络给芯片供电[6]。

Figure 1 Power supplying model of chip图1 芯片供电网络模型

PDN纹波噪声往往会给系统带来致命影响,不仅造成时序容限减小,更可引起EMC效应增强。高速电路中通常采用大面积覆铜以达到低阻抗的PDN设计,而此种方法经常不能满足设计需要。

随着系统频率的不断提升,电源/地平面的诸多高频效应凸显,如谐振效应、边缘效应等,对电源阻抗产生显著影响,而解决此问题最简单有效的方案是添加大量去耦电容。去耦电容按所处位置分为三大类:片内去耦电容、封装(PKG)去耦电容、PCB去耦电容,其去耦速度依次降低,而所付代价也相应减少。PDN设计中,去耦电容对于集成电路(IC)的电流反应能力由各部件频率响应、距离IC远近和IC间寄生效应共同决定[7]。

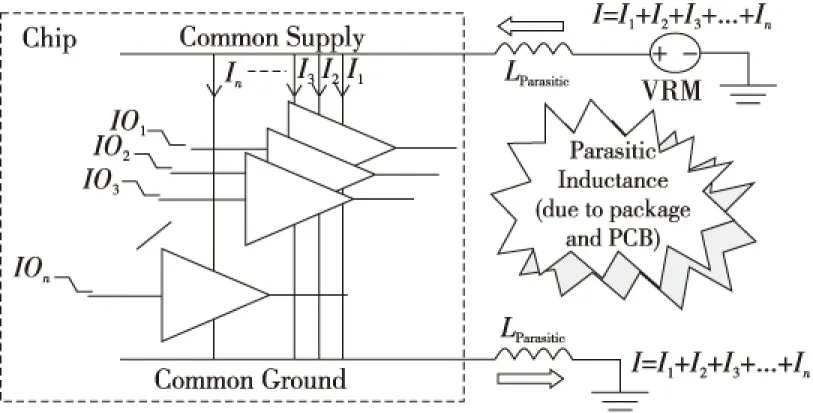

DDR3总线属于高速并行总线,数据信号DQ的同步开关噪声对DDR3总线的影响比较大。同步开关噪声SSN来自同时开关引起的瞬间变化电流(dI/dt),在经过回流路径上的分布电感时,形成交流压降,从而产生的噪声。由于压降产生于PDN上,而信号又以PDN为返回路径和参考点,因此噪声必然会影响信号回路[8]。SSN主要源于芯片键合、封装和连接器的寄生电感。量化SSN比较困难,但根据计算公式:VSSN=N*Lloop*(dI/dt),可知SSN正比于同时开关的驱动器数目N、回路总电感Lloop和电流变化率dI/dt。同时开关的驱动器数目越大,SSN就越严重,图2为等效同步开关噪声产生的原理[9]。

Figure 2 Simultaneous switch noise图2 同步开关噪声(SSN)

3 目标阻抗

PDN阻抗定义为,从用电器件端看整个电源分配网路的阻抗,通常使用Z参数表示。而目标阻抗则是用以评估PDN设计阻抗是否超标的准则,通常用Ztarget表示,如图3所示。若电压的允许波动为Vripple,则Ztarget可用公式Ztarget=Vripple/Imax计算。

Figure 3 Definition of PDN target impedance图3 PDN目标阻抗定义

根据关系式P=V*Imax和由已知的功率P、电压V可确定IC中流出的最大电流。目标阻抗Ztarget在频域范围内确定了IC电源端PDN最大阻抗上限,低于目标阻抗能够确保任何电流跳变引发的电压噪声均小于电压波动Vripple。

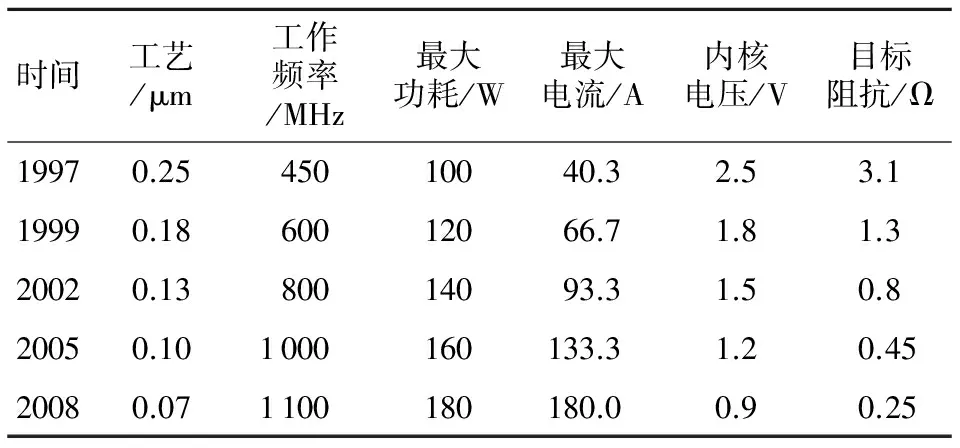

随着各种芯片(处理器)的各项性能指标不断提升,PDN的目标阻抗亦随之变化,表1为微处理器目标阻抗的变化表,可见目标阻抗值大约每三年下降1.6倍。越来越严苛的设计条件,使得目标阻抗的重要性更加凸显[10]。

Table 1 Roadmap of target impedance

4 动态目标阻抗

由目标阻抗的计算公式可见,电流值的计算是确定Ztarget的关键。使用Imax获得的固定值目标阻抗虽然简单方便,但随着设计复杂度的提高,描绘的阻抗界限过于保守,易造成过设计,从而提升设计复杂度。基于此缺点,可对目标阻抗计算式进行如下修改:Ztarget=Vripple/(50%*Imax)(Ω),式中假设开关电路流出的平均电流为最大电流的50%,然而此时的目标阻抗的确定仍比较粗糙。因为芯片实际工作电流值并非是恒定不变值,而是与工作状态相关,是频率相关源。

更严格的方法是施加测试向量作为激励,用spice电路仿真得到动态电流I(t),再使用傅里叶变换得到电流与频率的关系曲线I(f),再反推出Ztarget(f)。常用的激励包括脉冲源、PRBS码,也可以根据实际的访存提取出测试向量作为激励。这种方法的主要问题是计算结果与具体使用的测试向量相关,不可能覆盖到所有的情况。

图4为Ztarget(f)与Ztarget的比较图。相比Ztarget曲线给出的过于保守严苛的限制条件,获取的动态目标阻抗曲线Ztarget(f)在基于频变动态电流的基础上,能够更精准地给出不同电流情况下的PDN阻抗的约束条件。

Figure 4 Comparsion of Ztarget(f) and Ztarget图4 Ztarget(f)与Ztarget对比

5 基于动态目标阻抗的仿真流程

目前PI仿真流程中,通常使用恒定目标阻抗作为后仿真PDN阻抗的设计优化目标。如图5a所示是针对目前PI仿真流程中加入前仿真的优化设计流程。因为受前仿真中等效模型精度所限,I(f)的准确度难以保证。所以,基于Ztarget与Ztarget(f)的各自特性,分别将Ztarget应用于PI设计的前仿真阶段,用以指导PDN设计,而将Ztarget(f)应用于PI设计的后仿真阶段,用以优化改进PDN性能,二者同时结合共同应用于PI仿真流程,如图5b所示,可以更加高效地与设计相协同,减少迭代次数,提升PDN的一次设计成功率。

Figure 5 Design and optimization flow for PI图5 PI设计优化流程

6 仿真结果与分析

基于写仿真链路,对各DQ分别使用独立的200 bit随机码作为激励进行仿真。如图6为 fast、typical和slow三种情况下使用PRBS码(PI_PRBS)的VDDQ电压时域仿真结果。三种仿真条件下,VDDQ电压纹波均已超出要求的正常电压+/-5%波动范围,最高可达10%,尤其在初始20 ns范围内与仿真结束前波动较为明显。对比频域PDN阻抗曲线,如图7所示,得知DDR3电源网络阻抗设计不合理,在300 MHz~1 GHz范围反谐振值已严重超出动态目标阻抗限定范围。

Figure 6 Simulation waveform of VDDQ图6 VDDQ仿真波形

Figure 7 Impedance of VDDQ without PI optimization图7 PI仿真优化前VDDQ阻抗

Figure 8 Simulation waveform of VDDQ using pulse图8 Pulse激励下VDDQ的仿真波形

使用同步脉冲激励源(PI_Pulse)发现SSN效应更加明显。如图8所示是PI_Pulse仿真条件与Typical模式下,PDN阻抗优化前VDDQ电压波形。由图8可见,电源纹波已严重超过噪声容限范围,最低与最高电压值分别可达0.5 V与1.2 V,超标量最高可达67%。相比PI_PRBS电压波动情况,施加PI_Pulse激励时PI问题更严重。

为保证芯片正常工作,减小SSN效应,必须对频域PDN进行优化,以满足目标阻抗的设计要求。如PI_PRBS仿真中频域PDN阻抗如图7所示,需优化谐振点已位于500 MHz之上,结合去耦电容的作用频段,此时应选择合适的去耦电容对封装设计阻抗进行有效去耦,以降低总体电源平面阻抗谐振幅度。

去耦电容的选择应充分考虑电容特性中谐振频率、温度特性、寄生参数、额定电压等综合作用因素,同时辅助以谐振分析、电容优化等仿真指导手段。在进行大量筛选实验后,最终选定Murata电容库中0201普通电容以及低寄生电感(ESL)的0508电容作为PKG中VDDQ平面去耦电容,如图9所示。

Figure 9 Decoupling capacitor for VDDQ in package图9 封装中VDDQ平面去耦电容

如图10所示为PKG添加去耦电容后的总体VDDQ平面阻抗优化图。由图10可见PDN阻抗设计已符合设计中动态目标阻抗要求。为进一步验证PDN优化作用效果,需进行时域眼图仿真的再次迭代。图11为VDDQ_Typ电压波形。通过修改PDN后的时域仿真波形可见,电源纹波的波动范围幅度已降低到1.44~1.54 V内,波动范围小于+/-3%,符合电源设计要求。

Figure 10 Impedance of VDDQ after PI optimization图10 优化后的VDDQ阻抗

Figure 11 Simulation waveform of VDDQ after PI optimization图11 PI优化后VDDQ波形

在时序裕量计算前首先选取最差DQ信号,用以观察信号质量,如图12所示,在1 333 Mbps数据传输率下,眼图质量无明显失真扭曲现象,且信号最差眼图有效窗口仍可达551.1 ps。此时对比时序裕量可见,PDN优化后,可以满足1 333 Mbps仿真要求。

Figure 12 Eye diagram of worst DQ after PI optimization图12 PI优化后最差DQ眼图

7 结束语

考虑到芯片实际工作电流值并非恒定不变,而与实际工作状态相关,是一种动态变化的频率相关源,本文提出了一种新的基于目标阻抗与动态目标阻抗的混合仿真与设计流程,在前仿真阶段采用恒定目标阻抗,在后仿真阶段采用动态目标阻抗为设计目标,实现设计优化速度与精度的统一。仿真结果证实了方法的有效性。

[1] JEDEC DDR3 SDRAM specification [S]. JEDEC JESD79-3E, JEDEC Solid State Technology Association 2010-07-01.

[2] Brennan C,Tudor C, Schroeter E, et al. Signal integrity and PCB layout considerations for DDR2-800 Mbps and DDR3 memories[R]. Silicon Valley.CDNLive Silicon Valley, 2007.

[3] Mahajan R. Memory design consideration when migrating to DDR3 interface from DDR2[R]. MemCore Inc,2007.

[4] Chuang Hao-hsiang,Wu Shu-jung,Hong Ming-zhang,et al. Power integrity chip-package-PCB co-simulation for I/O interface of DDR3 high-speed memory[C]∥Proc of Electrical Design of Advanced Packaging and Systems Symposium,2008:31-34.

[5] Ren Ji-hong,Oh Dan, Chang S, et al. Statistical link analysis of high-speed memory I/O interfaces during simultaneous switching events[C]∥Proc of IEEE-EPEP Performance of Electronic Packaging, 2008:25-28.

[6] Swaminathan M, Engin A E.Power integrity modeling and design for semiconductors and systems[M].New Jersey: Prentice Hall, 2008.

[7] Popovich M, Friedman E G. Decoupling capacitors for multi-voltage power distribution systems[J]. IEEE Transactions on Very Large Scale Integration Systems, 2006,14(3):217-228.

[8] Pitica R F D. Pre-layout power integrity analysis in the design flow of a PCB[C]∥Proc of 2011 IEEE 17th International Symposium for Design and Technology in Electronic Packaging, 2011:77-80.

[9] Shi Lin-seng. Co-simulation and co-design of DDR3 system based on creative CPU[D].Changsha:National University of Defense Technology, 2011. (in Chinese)

[10] Song Yong-gao.System level high speed parallel bus-DDR3 co-design simulation and optimization [D].Changsha: National University of Defense Technology,2013. (in Chinese)

附中文参考文献:

[9] 史林森. 基于自主CPU的DDR3系统协同仿真与设计[D].长沙:国防科学技术大学, 2011.

[10] 宋永篙. 系统级高速并行总线—DDR3协同设计与仿真优化[D].长沙:国防科学技术大学,2013.

LI Jin-wen,born in 1975,PhD,associate research fellow,his research interest includes high speed digital design.

Simulation on power integrity of DDR3 system based on dynamic target impedance

LI Jin-wen,CAO Yue-sheng,HU Jun,XIAO Li-quan

(College of Computer,National University of Defense Technology,Changsha 410073,China)

DDR3 memory has become one of the mainstream applications in current servers and computer systems. Although many techniques such as dual reference voltage, dynamic on-die termination (ODT), fly-by topology and write-leveling, have been adopt by DDR3 in order to improve signal integrity in a certain extent, it is still difficult to design and realize high data rate. Since DDR3 is a typical parallel bus structure, the simultaneous switching noise is couped with the original power noise, affecting the quality of data signals. Taking into account that the chip current is a dynamic changing and frequency related source, the paper proposes a new mixed simulation and design procedure based on target impedance and dynamic target impedance. The constant target impedance is adopted in pre-simulation, while the dynamic target impedance is used in post-simulation. The trade-off between speed and accuracy of design optimization is realized, and simulation results prove the feasibility and efficiency of this method.

DDR3 DIMM;power integrity(PI);dynamic target impedance

2013-10-15;

2013-12-25

国家自然科学基金资助项目(60873212)

1007-130X(2014)03-0399-05

TN41

A

10.3969/j.issn.1007-130X.2014.03.004

李晋文(1975-),男,山西武乡人,博士,副研究员,研究方向为高速数字设计。E-mail:lijinwen@nudt.edu.cn

通信地址:410073 湖南省长沙市国防科学技术大学计算机学院

Address:College of Computer,National University of Defense Technology,Changsha 410073,Hunan,P.R.China