基于CPLD的正弦波/方波互换电路及实验

2014-09-11武立华赵恩铭刘志海

武立华,黄 玉,王 姣,赵恩铭,刘志海

(哈尔滨工程大学 a.理学院 理学之光科技创新中心; b.信息与通信工程学院, 黑龙江 哈尔滨 150001)

1 引 言

在驱动磁通门传感器时,经常需要将方波信号转换成正弦信号,而一般的由波形发生芯片组建的信号发生电路只能产生一些常规的信号(如正弦波、方波、脉冲波、三角波等),信号的幅值、频率等参量调节不便,需要修改电路设计[1-3]. 但相关检测法等许多应用领域,同时需要正弦波、方波等多种信号[4-5]. 磁通门传感器的激励信号峰峰值一般要求大于5 V,简单的波形发生芯片不能满足这一特定要求[6].

目前,国内生产的波形变换装置大部分是分立元件组成的,转换量程靠手动实现,不仅体积大,而且可靠性和准确度很难进一步提高. 其另一个局限性是只能就单一波形进行变换. 由于CPLD内部结构是并行结构,与单片机存在本质差别,处理速度是单片机无法比拟的[7]. 利用CPLD进行的正弦波和方波的信号转换不仅可以实现信号间的转换而且还可以实现对正弦波和方波的整形、放大,具有很高的频率稳定度和精确度,可作为磁通门传感器中的激励源和解调中的载波信号.

采用晶振产生特定频率与幅值的方波信号,并应用可编程逻辑器件CPLD进行数字量转换,使用射随放大器TLC272与CPLD进行波形整形与放大. 射随放大器件消除信号间的干扰,保证了信号的精确度,增加了装置的带载能力. 模块化的软硬件设计也非常有利于系统的检测和故障分析.

2 转换电路原理及其设计

2.1 正弦波/方波转换方案设计

对于输入为方波时(如由晶振产生峰峰值为3.3 V,频率为8 MHz的方波信号),先将该信号输入到CPLD,通过程序设计控制方波信号的占空比. 再将方波信号通过谐振电路进行波形转换,使其变成同频率同幅值的正弦波信号,然后接入放大电路,对其幅值进行放大.

当接入信号为小幅值、频率特定的正弦波信号时,先将正弦波信号接入转换电路变为峰峰值为3.3 V、频率为8 MHz的方波,再将该信号输入到CPLD,通过程序设计控制方波信号的占空比,将调节完占空比的方波信号接入放大电路,得到峰峰值大于9 V的方波信号,使其成为磁通门传感器的激励信号. 基于CPLD的方波/正弦波之间的互换电路原理图,如图1所示.

图1 方波/正弦波的互换电路原理

2.2 放大电路

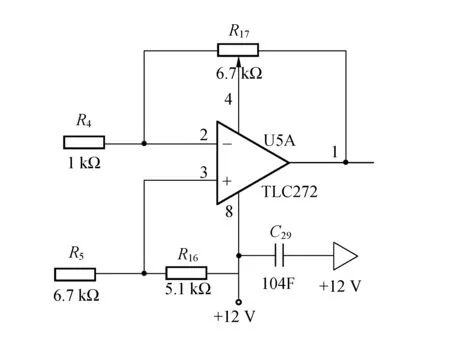

图2 TLC272放大电路图

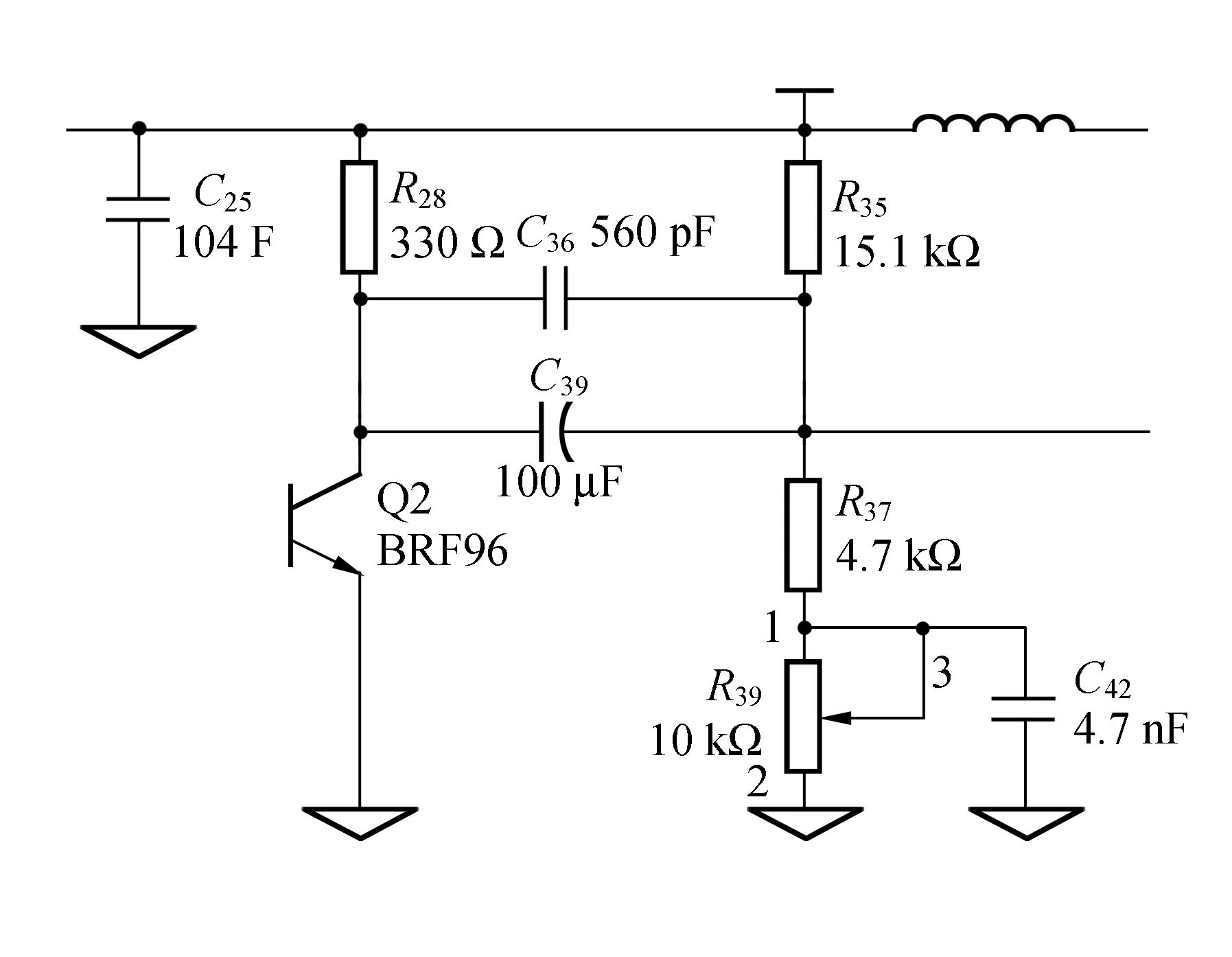

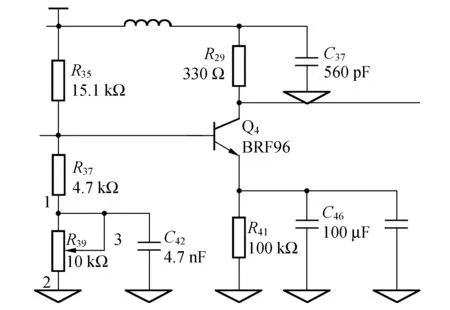

在由正弦波向方波转换过程中,需要把正弦信号进行放大,直到使放大器工作在饱和与截止状态,就变成了方波信号. 故本电路采用两级三极管放大电路,第一级前有1对二极管对放大电路进行电压保护,使输入电压稳定在0.7 V以内. 再由2个BFR96三极管组成的放大电路进行二级放大. 第一级和第二级放大电路如图3所示,在第一级放大电路中根据接入电阻控制放大倍数,放大倍数为

(a)第一级

(b)第二级图3 两级三极管放大电路图

其中rbe为三极管BFR96的电阻. 在第二级放大电路中,放大倍数为

当二级连续放大,理论上放大倍数可达到数万倍,但是由于给定的三极管饱和电压为3.3 V,利用饱和截止效应将正弦波限定为3.3 V,因此输出信号为3.3 V的8 MHz的方波信号.

3 实验结果

3.1 CPLD模块

CPLD内部采用固定长度的金属线进行各逻辑块的互连,所设计的逻辑电路具有时间可预测性,避免了分段式互连结构的时序不完全预测的缺点. CPLD主芯片采用Altera公司的MAX II器件系列的EPM240T100C5,该芯片有240个逻辑单元,等效宏单元是192个,最大引脚数为80个,可用的门电路达到2 500个,能够支持高达300 MHz的内部时钟,最大距离引脚之间的延迟时间最快达4.5 ns,最小距离管脚的延时时间达3.6 ns,内有8 kb Flash的存储空间,直流稳压电源用来给系统供电,工作电压为3.3 V.

CPLD程序采用混合编程方法,先用VHDL硬件描述语言编写各个模块,编译仿真正确后在电路图中进行连接. CPLD程序共有2个模块,一个是8位计数器模块,另一个是8位比较器模块,软件设计的电路图如图4所示. 输入的信号先由8位计数器对8 MHz的时钟信号进行计数,计数器每256个时钟周期循环1次,即分频后的信号频率为31.25 kHz. 计数器输出的值与比较器内部的8位寄存器的值比较大小,并把比较的结果输出. 通过改变寄存器内的值就可以改变输出信号的占空比.

图4 VHDL电路图

1)计数器的VHDL程序

8位计数器的实体一共有3个端口,分别是时钟信号输入端clk、计数值输出端data_out和256分频输出端div_out. 8位计数器,内部设置了8位寄存器div1,对于clk的每个上升沿,div1加1,然后把div1的值赋值给输出端口data_out.

设计的部分程序如下:

architecture behavioral of divider8 is

signal div1:std_logic_vector(7 downto 0);

begin

p1:process(clk,div1)

begin

if rising_edge(clk) then

div1<=div1+‘1’;

end if;

data_out<=div1;

div_out<=div1(7);

end process;

end behavioral;

b)比较器的VHDL程序

比较器端口输入分别为8位data_in,用于输入计数器的值;key_dre用于确定给内部寄存器进行加操作还是减操作;key_plus用于给内部寄存器进行加1或减1操作;cmp_out为占控比可调的输出端口. 8位比较器内部设置了1个8位寄存器data,1位的标志位flag,和1个8位的比较寄存器,用于与输入信号作比较.

比较器结构体中一共有4个进程. 由于VHDL程序中不可以用端口信号进行运算,所以第一个进程是把外部的数据赋值给内部的寄存器data中,用data进行后面的运算;第二、三个进程是完成按键的操作,用来对内部比较寄存器data_cmp进行加1减1操作. 第四个进程是把data寄存器与data_cmp寄存器的值进行比较,如果data内的值比data_cpm内的值大,则输出高电平,否则就输出低电平.

设计的部分程序如下:

architecture behavioral of compater8 is

signal data:std_logic_vector(7 downto 0);

signal flag:std_logic_vector(0 downto 0);

signal data_cmp:std_logic_vector(7 downto 0):="10000000";

begin

p1:process(data_in) --data

begin

data<=data_in;

end process;

p2:process(key_dre)

begin

if rising_edge(key_dre) then

flag<=flag+‘1’;

end if;

end process;

p3:process(key_plus,flag)

begin

if rising_edge(key_plus) then

if ((flag="1")and(data_cmp/="11111111")) then

data_cmp<=data_cmp+"1";

elsif (flag="0")and(data_cmp/="00000000") then

data_cmp<=data_cmp-"1";

end if;

end if;

end process;

p4:process(data,data_cmp)

begin

if(data>data_cmp) then

cam_out<=‘1’;

else

cam_out<='0';

end if;

end process;

end behavioral;

3.2 由方波转换为正弦波的输出结果

通过对CPLD编程使信号从CPLD输出频率为31.25 kHz、峰峰值为3.3 V的方波信号,通过调节由TLC272组成放大器的放大倍数,来实现信号输出幅度的可控. 通过谐振电路选择31.25 kHz的正弦波信号,滤掉其余频率信号. 实验结果如图5所示,正弦波的峰峰值接近9 V. 通过数字示波器的FFT功能,对转换为正弦的信号进行分析,用31.25 kHz的二次谐波与三次谐波的功率与总的功率相比,其失真度为1.32%,实现了不错的方波与正弦波的转换.

图5 方波转换为正弦波的实验结果

3.3 由正弦波转换为方波的输出结果

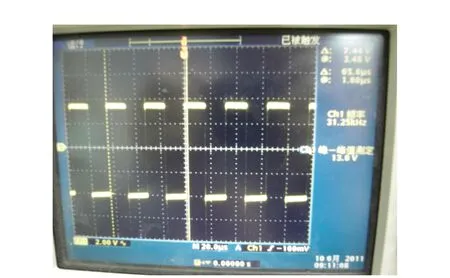

应用二级三极管放大电路,对正弦波输入信号进行大幅度放大,当正弦波放大到一定倍数时,截去正弦波波峰,正弦波波形会近似成方波. 再经过CPLD得到占空比可调的方波信号. 由峰峰值仅为118 mV的正弦波转换得到的方波信号及由TLC272放大电路放大后的方波信号分别如图6和图7所示,峰峰值达到了13 V,峰峰值大于9 V的方波信号可用作磁通门传感器的激励信号,如图8所示,从图中可看到,磁通门输出了方波整数倍频率的信号,表明磁通门传感头正常工作.

图7 经TLC272放大后的方波

图8 磁通门传感头测试结果

4 结 论

从实验结果看,采用CPLD实现的正弦波与方波互换电路可以满足应用需求,与采用分立元件或集成芯片组成的信号发生器相比,其产生的波形单一,幅值、频率等参量不易调节,信号峰峰值也受制于器件,多数信号发生芯片产生的波形峰峰值不超过5 V而不能满足特定的要求. 磁通门的激励信号峰峰值要求比5 V大很多,因此一般的信号源不能适应这种应用需求. 采用数字芯片CPLD为核心元件构建正弦波和方波互为转换电路,用于产生幅值、频率等参量可调的正弦波或方波信号. 设计了转换电路与CPLD的程序,进行了相关功能模块的仿真实验,转换电路的实验测试验证了电路设计的正确性和有效性.

参考文献:

[1] 夏光瑜. 互补正弦波电源在磁通门中应用[J]. 仪器仪表学报,2003,14(2):120-122.

[2] 王红利. 自给电正弦波方波转换器[J]. 传感技术学报,2006,18(6):1035-1038.

[3] 徐素利,赵红英. 基于OrCAD/Pspice的信号发生电路设计[J]. 现代电子技术,2008,280(17):154-156

[4] 祝荣荣,殳国华. 基于相关检测的电容传感器的研究[J]. 仪表技术与传感器,2004,(8):3-4,8.

[5] Huang Song-ming,et al. A high frequency stray-immune capacitance transducer based on the charge transfer principle [J]. IEEE Trans. Instrum. Meas.,1988,37(3):368-371.

[6] Baschiroto A, Borghettl F, Dallago E, et al. Fluxgate magnetic sensor and front-end circuitry in an integrated microsystem [J]. Sensors and Actuators A, 2006, 132: 90-97.

[7] 黎洪生. 基于CPLD的超声波水位测量系统的研究[D]. 武汉:武汉理工大学,2010.