基于FPGA的高性能数据采集和预处理系统的设计

2014-09-10徐建丽吴长瑞

徐建丽 ,吴长瑞

(1.淮安信息职业技术学院 电子工程学院,江苏 淮安 223003;2.中国科学院 声学研究所,北京 100190)

0 引言

随着数据采集和预处理系统在电子战接收机中的广泛应用,人们对其性能要求也越来越高[1-2]。而数据采集和预处理系统的关键器件之一就是模数转换器,传统的模数转换器存在采样率低、输入信号动态范围窄和信号分辨率低等缺陷,同时,传统系统后端处理模块的处理能力也无法满足目前的应用需求,高性能模数转换器的输出必须由相匹配的后端模块接收和处理,否则,数字化后的数据就会丢失。因此,设计高性能模数转换器以保证每秒千兆采样率时具有较宽的动态范围和输入带宽是发展的必然趋势。

本文就是在这种背景下利用高性能模数转换技术和FPGA技术设计一种瞬时输入带宽较大的信号采集和预处理系统。

1 系统结构

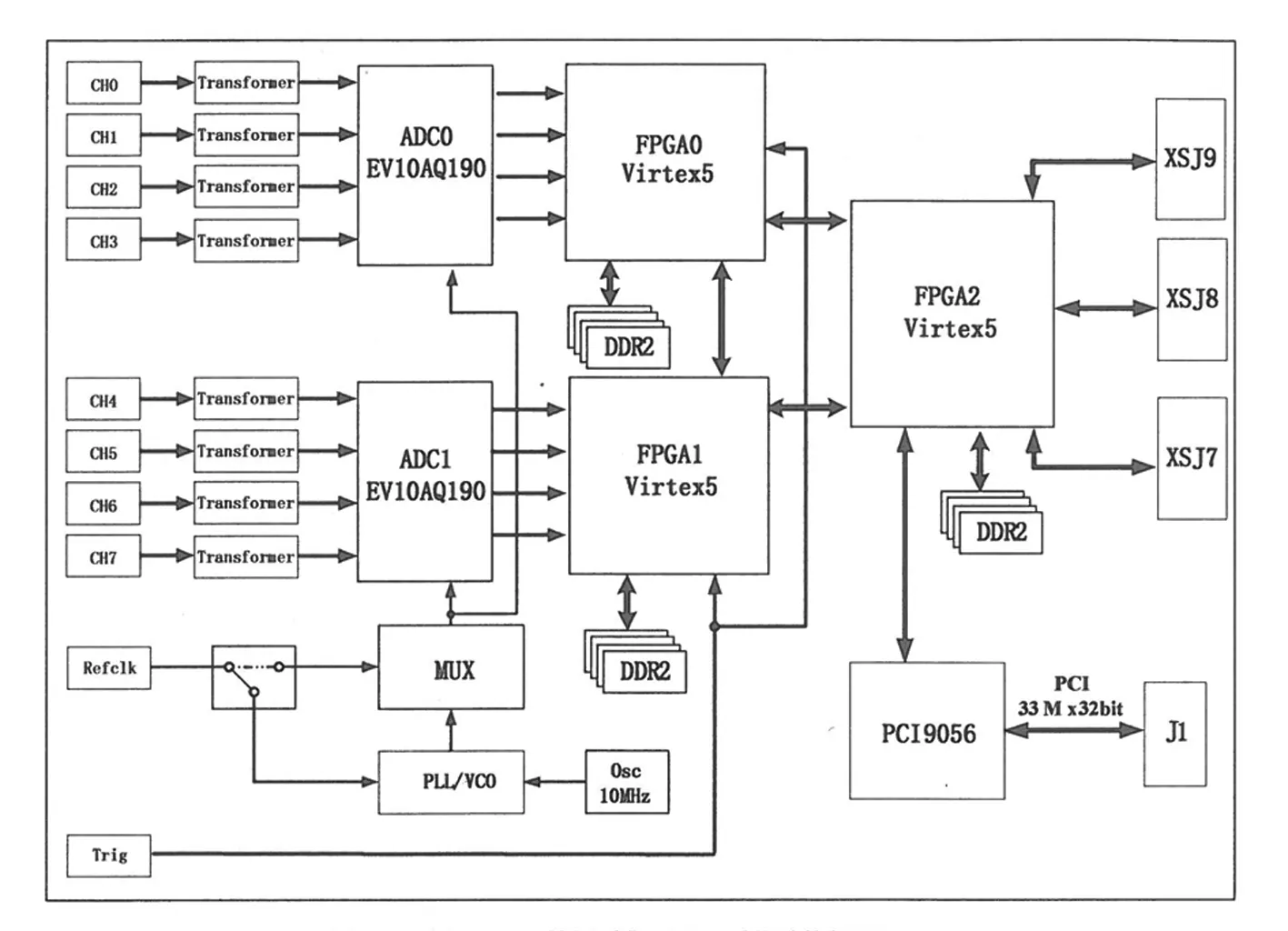

本文设计的高性能数据采集系统可以实现48Gbps数据带宽。系统由2片采样率为2.4Gsps、量化位宽为10 bit的宽带模数转换器EV10AQ190和3片高性能的FPGA XC5VSX95T组成。其结构框图如图1所示。该系统的功能是完成宽带数据采集、预处理和分发。系统按照6U CPCI 的机械尺寸和电气规范设计。

本设计模数转换器采用E2V公司生产的TG UT R EV10AQ190,处理模块采用赛灵思公司的XC5VSX95T。其中,EV10AQ190是一款单通道高达5Gsps采样率的低功耗ADC芯片,XC5VSX95T是同系列中DSP48E模块最丰富的一款FPGA。

设计采用2片EV10AQ190用于双通道数据采集,在图1中用ADC0和ADC1来表示;3片XC5VSX95T用于数据接收、预处理和分发,在图1中用FPGA0、FPGA1和FPGA2表示。

FPGA0和FPGA1分别接收ADC0和ADC1的输出数据,并对接收数据进行预处理,然后数据汇集到FPGA2中。此外,FPGA0和FPGA1还负责实现ADC0和ADC1的灵活配置。

每片EV10AQ190配置成单通道采样模式,包含有四个模拟信号输入。本设计由于工作在单通道采样模式,所以实际应用中仅需要使用其中一个模拟信号输入。系统还有一个外部触发输入信号用于实现两片EV10AQ190的同步触发。

图1 双通道2.4Gsps数据采集预处理系统结构框图

系统采用两种时钟方案,分别为外部时钟输入和内部时钟输入。设计采用模拟公司开发的时钟缓冲器ADCLK948 用于实现两种时钟方案的切换。ADCLK948是一款应用于高速低抖动应用环境下的高性能时钟缓冲器。由于两片ADC均工作在采样率为2.4Gsps的模式下,而其输入时钟只要1.2GHz,所以ADC内部采用交错采样的模式实现了2.4Gsps的采样。当采用外部时钟输入方案时,单端频率为1.2GHz、抖动小于0.35ps正弦时钟通过SMA连接器输入到图1中的Refclk端。当采用内部时钟方案时,板载10MHz的晶振通过AD9520倍频到1.2GHz[3]。

2 系统数据流设计

本设计采用3片Virtex5系列的FPGA、FPGA0和FPGA1在系统中的功能是一样的,二者采用相同的逻辑设计。基于以上原因,这里只讨论FPGA0的逻辑设计。

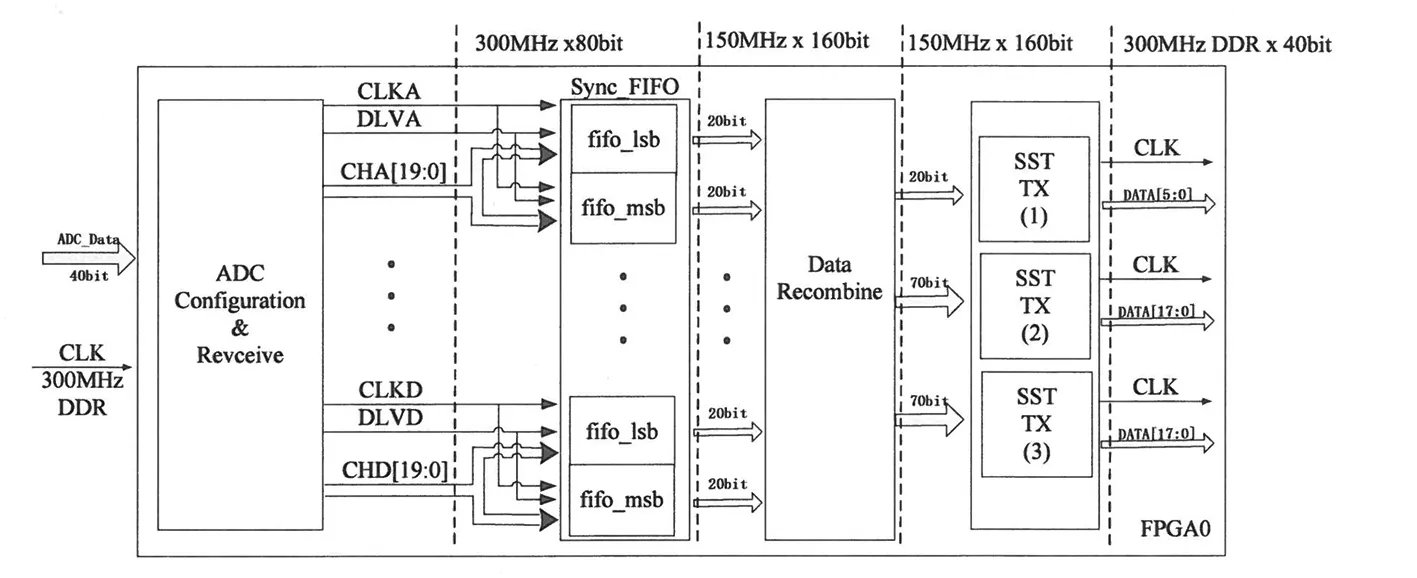

2.1 FPGA0逻辑设计

FPGA0数据流模块框图如图2所示。它主要由四个模块组成。

(1) ADC Configuration & Receive模块:负责配置ADC的寄存器,并接收ADC输出位宽40bits、时钟频率300MHz、双时钟沿采样的数据。该模块利用FPGA的原语IBUFDS 和 原语IDDR把双时钟沿、位宽40bits的采样数据转换成单时钟沿、位宽80bits的采样数据。模块的输入和输出在同一时钟域中。

(2) Sync_FIFO模块:负责同步4路ADC数据,并实现时钟降频。模块由4组FIFO模块组成,每组FIFO模块包含两个FIFO原语,另一个为fifo_lsb,一个为fifo_msb。该模块输出的数据为时钟频率150MHz、位宽160bits的同步数据。

(3) Data Recombine:实现数据整形和重组。

(4) SST TX模块,负责把重组后的数据以源同步协议的方式传输到FPGA2中。

图2 FPGA0中数据流模块框图

源同步是适用于两Xilinx FPGA之间的接口通信协议。它是一种高带宽通信协议,有发射端和接收端之分。本设计中,FPGA0、FPGA1均为发射端,FPGA2为接收端。源同步协议采用4:1 的Oserdes实现数据并串转换,并串转换的时钟频率为2:1。FPGA0和FPGA2之间物理传输的是时钟频率300MHz、双时钟沿采样、位宽40bits的数据流,二者之间的通信带宽是300MHz x2 x40bits= 24Gbps。同理,FPGA1和FPGA2之间的通信带宽也是24Gbps。FPGA2接收48Gbps的数据并重新打包发送到下一级的存储模块。

2.2 FPGA2逻辑设计

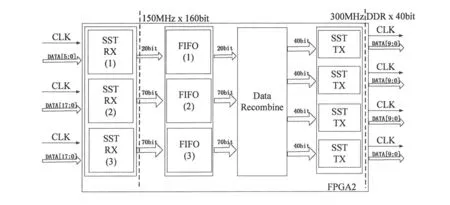

图3描述了FPGA0传输到FPGA2中的数据流模块框图。由于FPGA0与 FPGA2之间的数据流与FPGA1与FPGA2之间的数据流相同,故这里只阐述FPGA0与FPGA2之间的逻辑设计。这部分数据流主要由四个模块组成。

图3 FPGA2中部分数据流模块框图

(1) SST RX 模块:FPGA2使用3个源同步接收模块接收来自FPGA0中3个源同步发射模块的数据。

(2)同步FIFO模块:实现3个接收模块的数据在同一时钟域中。源同步通信协议中为了保证信号的完整性采用局部时钟域,在FPGA内部为了数据处理方便,采用全局时钟域。

(3)Data Recombine:实现数据整形和重组。

(4)SST TX模块:数据重新分发并通过源同步协议传输到下一级存储和处理单元中。

为了保证系统中3片FPGA时钟的同源性,两两FPGA之间通过一对全局时钟差分线相连。FPGA内部分为全局时钟和局部时钟[4]。全局时钟可以同时驱动多个bank内的资源,不足是延时较大。局部时钟仅限FPGA内部的bank内使用,具有延时小、抖动小等特点。本设计根据全局时钟和局部时钟各自的特点将其应用于不同的模块中。

3 性能分析

有效位ENOB(Effective Number of Bits) 和信噪比SNR(Signal Noise Ratio)是衡量高速信号采集系统性能的两个关键性技术指标。其中,ENOB是衡量实际ADC性能与理想ADC性能的信号对噪声加失真比SINAD (signal-to-noise and distortion ratio)的指标[5-6]。通过分析可知,ENOB可以通过计算SINAD获得,即

(1)

SINAD可以根据一组时域采样数据进行FFT计算, 得到频谱,之后从频谱中获取信号、噪声和谐波分量的相关信息。FFT输出像模拟频谱分析仪一样包含各次谐波的幅度和数字化信号的噪声成分。SINAD的计算公式如下:

(2)

为获得准确的时域采样数据,设计中使用罗德施瓦茨公司生产的型号为SMA-100A、抖动小于0.35ps的信号源作为ADC的模拟信号输入和正弦时钟输入。FPGA接收ADC的数据并使用软件工具Chipscope捕获时域采样数据。

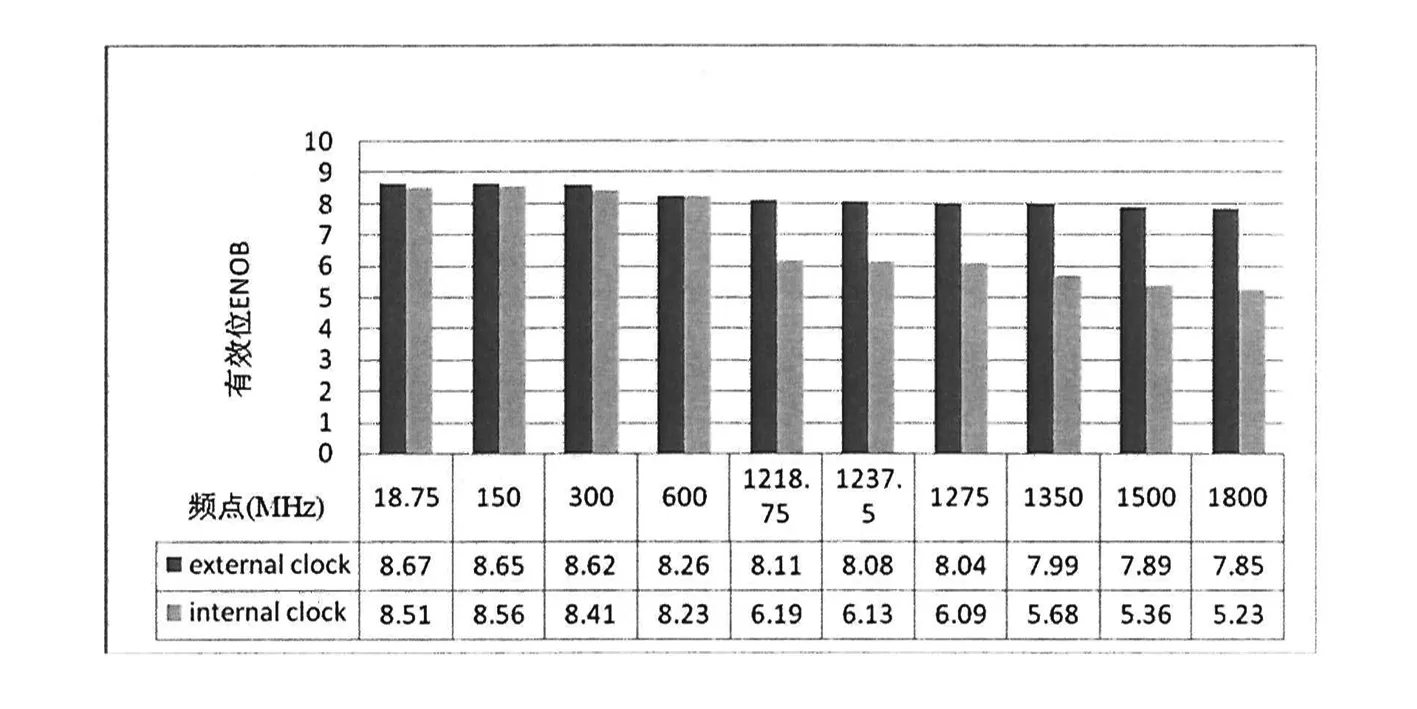

实验中对频率从18MHz到1.8GHz范围内的单频点模拟信号进行测试并计算其对应的有效位ENOB值。

实验对外部时钟输入和内部时钟输入两种方案分别进行了测试。图4描述了两种时钟方案条件下频率范围从18MHz到1.8GHz的单频点模拟信号输入时对应的系统有效位。从图4中可以看出,在同样条件下,外部时钟输入时对应的系统有效位要高于内部时钟输入时对应的系统有效位。主要原因是外部时钟比内部时钟抖动性小和稳定性强。此外,系统有效位在高频部分下降的较快一些,主要原因是高频部分孔径抖动更大[7]。

图4 两种时钟方案不同频点对应的有效位值

图5 外部时钟方案不同频点对应的信噪比

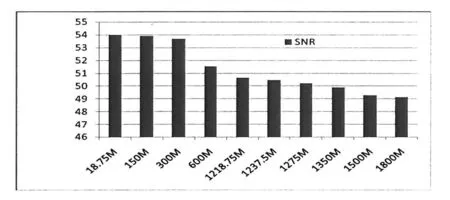

信噪比SNR与SINAD一样,也是根据FFT数据计算,不同的是计算剔除了信号谐波,仅留下噪声项。实际测试中,剔除了主要的前5次谐波。其计算公式如下:

(3)

以上面实验获得的时域数据计算系统信噪比,由于内部时钟引入的抖动太大,故只对外部时钟输入条件下频率范围从18MHz到1.8GHz的单频点模拟信号输入时对应的信噪比进行分析,如图5所示。从图中可知,SNR性能在高输入频率时会下降,但由于不包括谐波项,其下降速度一般不像SINAD那样快。在同等条件下,本文设计的系统的有效位和信噪比指标优于现存信号采集系统的相应指标。

5 结论

设计的双通道4.8Gsps高速采集和预处理系统已经成功应用于宽带接收机中,并取得了良好的效果。由于采用3片XC5VSX95T对FPGA内部采样数据协同处理的架构,设计节省了功耗和空间,并缩短了系统开发周期,系统具有很大的灵活性,该设计方案可以在电子对抗和高分辨雷达等对采样信号带宽要求很高的领域中推广应用。

参考文献:

[1] James B.Tsui.Digital Techniques for Wideband Receivers[M].Raleigh:SciTech Publishing Inc.,2004.

[2] 沈兰荪.高速数据采集系统的原理与应用[M].北京:人民邮电出版社,1995.

[3] 胡庆生,许多,苗澎.40Gbps甚短距离并行光传输技术与实现系统[J].电子学报,2011,39(5):1174-1177.

[4] 熊君君.星载SAR实时成像处理器的FPGA实现[J].电子学报,2005,33(6):1070-1072.

[5] 林茂六.高速ADC及由其构成的并行/交替式数据采集系统的非线性研究[J].电子学报,2000,28(2):72-78.

[6] 曹鹏,费元春.孔径抖动对中频采样系统信噪比影响的研究[J].电子学报,2004,32(3):381-383.

[7] 王佰玲.基于数据流的网页内容分析技术研究[J].电子学报,2013, 30(4):250-253.