宽带数字阵列数字时延技术研究及硬件实现

2014-09-08章文星

吴 卫,章文星

(中国船舶重工集团公司第七二四研究所,南京 211153)

宽带数字阵列数字时延技术研究及硬件实现

吴 卫,章文星

(中国船舶重工集团公司第七二四研究所,南京 211153)

研究了基于数字延时技术的波束合成方法,通过理论推导、仿真证明了其正确性,并给出了硬件实现方法和资源评估,表明了其硬件可行性。

宽带相控阵;波束合成;数字延迟

0 引 言

在现代战争中,为了提高雷达对目标的分辨、识别能力并解决对目标成像问题,新体制相控阵雷达通常采用大瞬时带宽信号进行收发。由于传统相控阵雷达是通过控制信号的相位来延迟信号的,在宽带信号情况下存在波束指向偏移和扫描不准的现象。这种由于孔径渡越时间带来的波束 “色散效应”使得雷达工作瞬时带宽大大受限。本文以某宽带数字阵列雷达课题为背景,分析了宽带数字波束形成和窄带数字波束形成的异同,采用基于分数时延滤波器方法实现了数字宽带波束合成,并提出了基于分数时延滤波器的数字波束形成的硬件实现方法及资源评估。

1 传统移相方式进行DBF的弊端及解决方法

数字波束形成(Digital Beam Forming,DBF)是空域滤波的主要形式。假设有N个天线阵元,θ为目标方向,θBK为第k个波束指向,d为相邻阵元间距,λ为信号波长,信号为s(t)。数字多波束形成器将数字的幅度和相位的权值在所有通道信号求和之前加到每一个输入信号中。它保留了天线阵列单元信号的全部信息,并可以构成空间受控的一个或多个定向波束从而获得优良的波束性能。

以下以图1的线阵为例来说明基于移相方式的DBF合成方法。

图1 线阵 DBF时间延迟示意图

图1中,若仅采用移相方式来实现天线波束扫描,天线波束最大值指向θB,则要求相邻单元之间相移为△φ=(2π/λ)dsinθB,从而应提供的天线两端移相的相位差φB为

或

或

φB=2πfTAsinθB

其中,L为天线孔径长度,TA=L/c为天线孔径长度对应的电波传播时间,可称孔径时间。

(1)

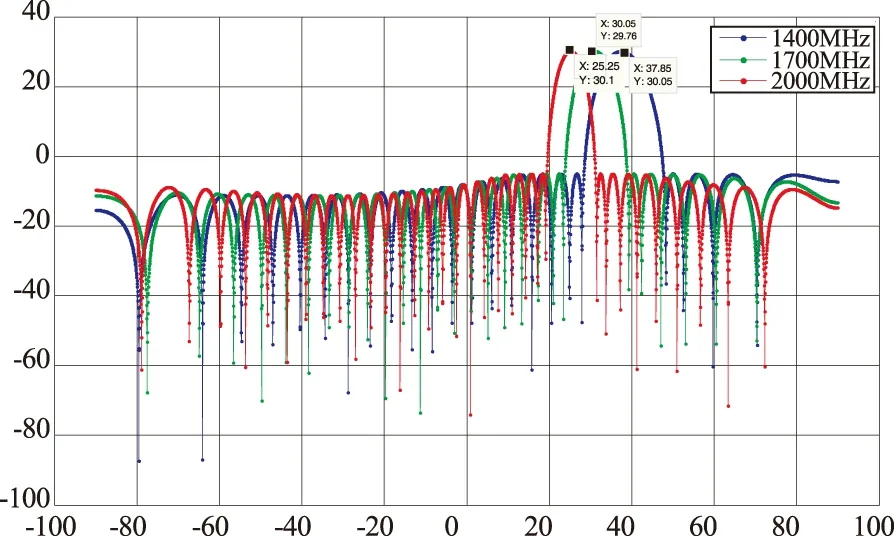

在移相值△φ保持不变的条件下,改变信号频率f,天线波束指向改变。这种由于f改变导致波束指向变化称为“色散效应”。由于课题中所处理的瞬时带宽最大为700 MHz,且宽带相控阵的孔径效应导致相控阵雷达波束的指向随频率的变化而偏移,如图2所示,中心频点在1.7 GHz,波束指向30°,而1.4 GHz和2.0 GHz则指向在37°和25°。

图2 基于移相方式得到的DBF方向图

而如果采用直接时间延时,即

△τ=LsinθB/c

(2)

那么

(3)

在式(3)中,因没有信号频率,故与信号频率无关,可保证波束指向θB保持不变。

2 分数延时数字滤波器的原理

常规宽带脉冲信号,其数学表达式可以表述为

其中,f0为信号的载波频率,T0为脉冲持续宽度,s(t)表示的是调制信号,而

为了能够进行数字信号处理,通常下变频至零中频,得到基带I/Q数据,再进行信号分析与处理后的基带宽带雷达信号可表示为

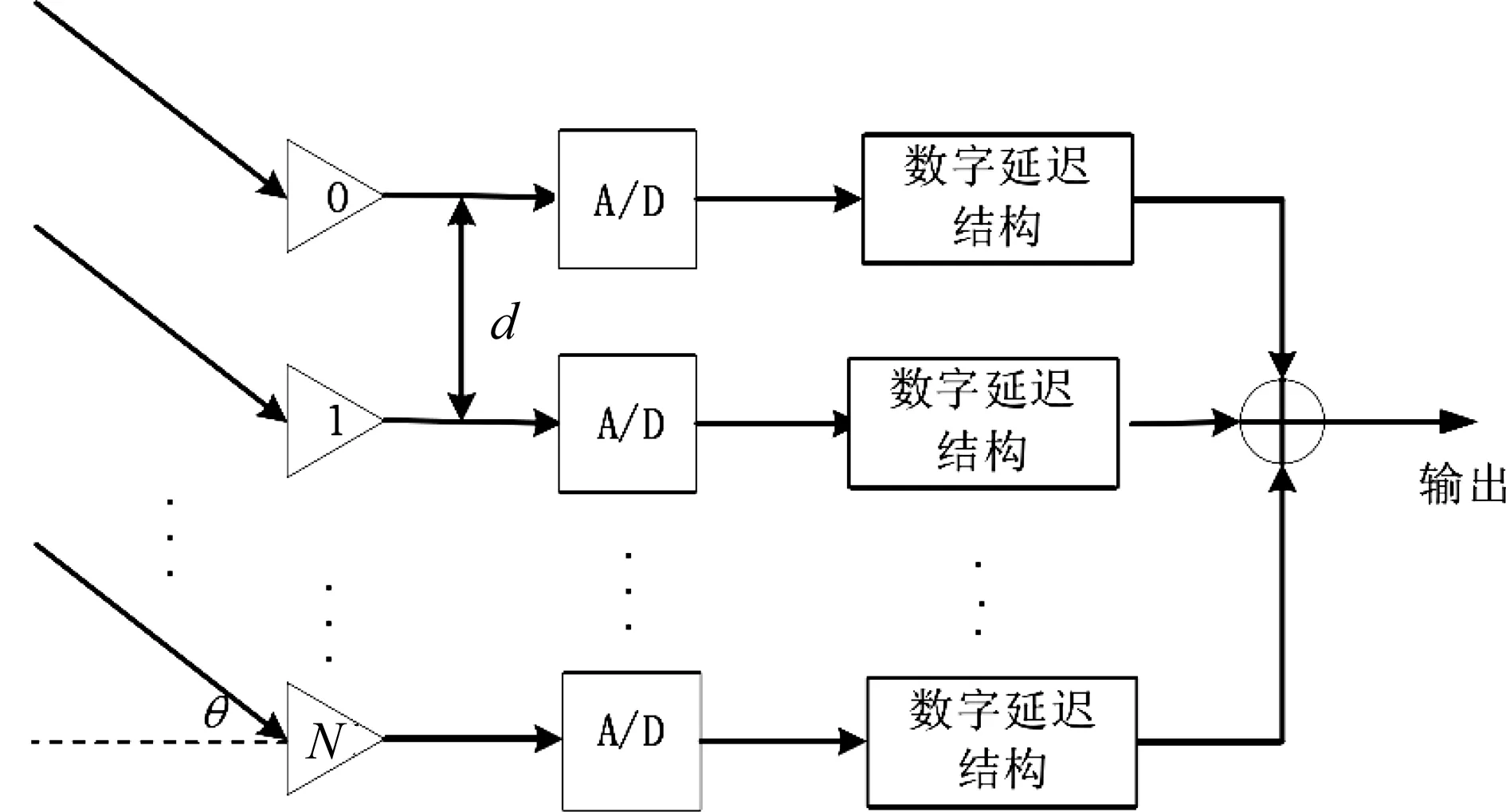

图3 基于数字延迟的宽带数字阵雷达接收机结构图

图3是基于数字延迟的宽带数字阵雷达接收机结构。在其所示的均匀线阵中,假设回波信号到达方向为偏离法线θ时,则阵列中相邻阵元接收到信号的时间差为

△τ=dsinθ/c

其中,d为阵元间距,c是光的传播速率。如果选择图 3 中线阵第0号阵元接收到的回波信号作为参考信号,则第k号阵元的接收到的回波信号形式为

把上式写成基带形式并展开可得

(4)

线阵各个阵元收到回波信号后,对式(4)的第2项进行数字移相补偿,对其第3项进行时延补偿,就可以使各个阵元接收到的信号同相叠加,进而使接收波束指向在预期方向上。图3 中第k号阵元相对参考阵元回波时延为

τk=k△τ

即

τk=kdsinθ/c

采样周期为T时,第k号阵元需要补偿的时延可表示为

τk/T=L+△

其中L表示整数倍采样周期时延:

L=round(kdsinθ/cT)

其中,round为四舍五入取整函数,△表示分数倍采样周期时延, 且有-0.5<△≤0.5:

(5)

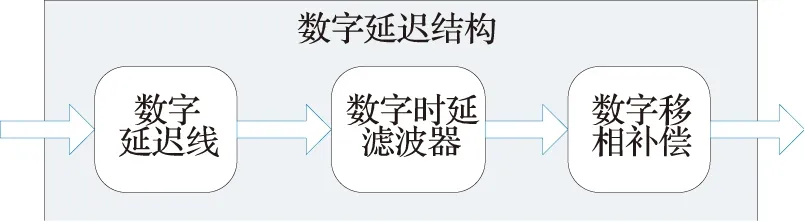

对回波信号进行离散化后,可以设计具有时延D=L+△的分数时延滤波器来补偿回波信号的时延。因此,数字延迟结构可以由图4进行表示。

图4 数字延迟结构示意图

宽带数字阵波束形成实现结构的每一个通道可变数字延迟电路由数字移相器、数字延迟线和分数时延滤波器组成,其中用数字延迟线补偿整数倍采样间隔的时间延迟,用分数时延滤波器补偿分数倍采样间隔的时间延迟,而数字移相器补偿的是载波引起的空间相位差。通过改变数字移相器的值、数字延迟线的系数和分数时延滤波器的系数就可实现对各阵元的传输时间延迟进行精确的补偿。

3 分数延时数字滤波器的设计方法及仿真

在硬件设计上数字延迟线和数字移相补偿都比较容易实现。数字延迟线可以利用FPGA中的移位寄存器实现。数字移相补偿只是简单的乘加运算,也比较易于在FPGA中的实现。下面主要介绍分数时延滤波器的实现方法。分数时延滤波器主要是由基于Farrow结构的滤波器实现的,其实现框图如图5。

图5 基于Farrow结构的滤波器实现框图

由图5可知,Farrow 结构有M组N阶FIR滤波器构成,其中虚线框图中画出了第M组N阶 FIR 滤波器的CM-1内部结构,其余M-1组N阶FIR 滤波器的实现方式与CM相同。它的优点是当时延变化时仅改变时延参数D,就可以获得不同的分数时延,不用重新加载系数,节省了存储空间,降低了硬件实现的复杂度。

时延参数取[-0.5:0.1:0.5]时获得的分数延时滤波器的幅相频率响应及群延迟特性见图6和图7。

在实际使用中,可以采用8组不同加权系数的29阶FIRCore实现CM-1,CM-2,…,C0模块,再将8路FIRCore输出结果和时延参数D的相应阶数进行乘加运算就能得到最终的结果。其中,8组FIRCore权值为预先生成而不需要改变的值,而时延参数D随着扫描方位的变化而实时改变。

下面仿真了一组信号,验证延时滤波器的实现。信号的带宽B为10 MHz,中频f0为10 MHz,采样率fs为100 MHz,采样间隔ts为0.01 μs,脉宽τ为10 μs。

首先将原始信号经过数字下变频得到I/Q数据,同时将原始信号进行理论延时进行同样的数字下变频得到I/Q数据,最后将原始信号的I/Q数据经过时延滤波器,并和理论延时信号的I/Q进行比较,观察两者重合程度。

图8和图9为将原始信号进行0.104 μs延时(即10.4个ts)得到的结果通过时延参数为10.4的时延滤波器后得到的结果。图中,蓝色表示原始信号理论延时结果的实部,红色表示原始信号通过时延滤波器后的延时结果的实部,绿色表示原始信号的实部。

(a)幅频响应 (b)相频响应

图6 分数延时滤波器的幅频响应

图7 分数延时滤波器的群延迟特性

图8 时延滤波后得到的结果

图9 时延滤波后得到的结果放大图

通过图8和图9可以看出,在Farrow滤波器在脉冲信号的起始与结束两端的输出结果和理论延迟的结果重合度有误差,分析这是由于滤波器的瞬态响应导致,而在其他时刻(即滤波器稳态响应后)都能正确重合。

下面分别仿真了采用传统相位加权和Farrow结构实现分数时间延时得到的宽带数字阵列雷达的方向图。

仿真中使用的参数如下:均匀线阵阵元数32,选择线性调频信号作宽带雷达信号,载波频率为f0=1.750 GHz,时宽Tp=10 μs,输入三组频率分别为2 GHz、1.751 GHz和1.410 GHz的单频信号,采样率为1.4 GHz,阵元间距为最大频率对应波长的一半,Farrow结构取298,波束设计指向30°,通过计算机仿真并对结果做Taylor加权,可得天线方向图如图10和图11。

图10 传统相位加权得到的DBF方向图

图11 分数时间延时得到的DBF的方向图

可以很明显看出,使用相位加权法得到的方向图出现了 “色散”,而使用Farrow结构实现分数时间延时方法得到的方向图则没有“色散”。

4 硬件实现及资源评估

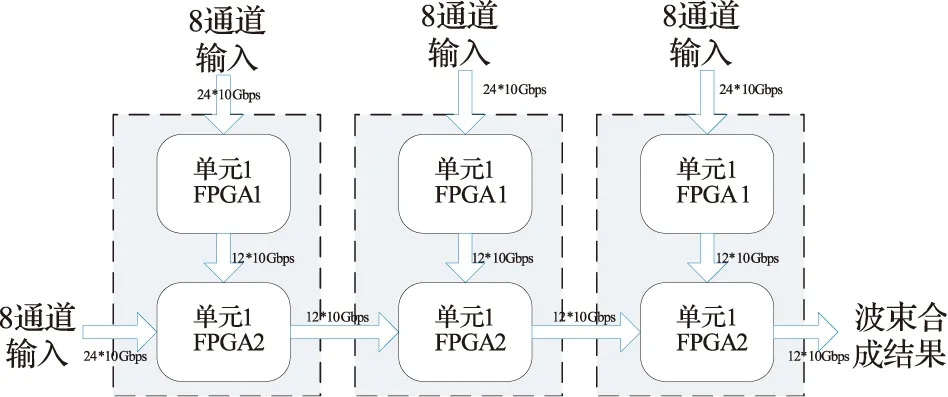

考虑到信号传输能力和FPGA处理能力,宽带数字DBF硬件将采用多板级联的方法来实现,最终实现同时二波束的处理。其实现框图如图12所示。

图12 宽带数字DBF硬件实现框图

由于本课题对宽带信号的采样率高达1.4 GHz,无法利用FPGA进行直接处理,在实际硬件实施时,采用将单路高速数据流分成多路低速数据流的方法,即Demux技术,以多个乘法器并行运算的方式来实现。

设计将每通道分成8路低速数据流。而分数滤波器需要生成8组29阶的FIRCORE,由于29阶系数是对称的,因此使用FIRCore的对称特性可以节省一半资源。所以,I/Q两路需要8×8×29×2/2=1856个DSP48E;时延参数D取0到7的阶数值,需要8个DSP48E(复数乘法器);相位补偿需要8个DSP48E(复数乘法器)。XC7V485T内部含DSP48E资源为2800个,完全可以满足要求。

5 结束语

基于Farrow结构的分数时延滤波器使得通道间信号延迟连续调整成为可能,从而为宽带数字相控阵的波束形成与扫描技术提供了基础。本文在对Farrow结构滤波器研究的基础上,进行了FPGA逻辑仿真和硬件实现资源评估,从而证明了其工程可行性。随着宽带相控阵雷达技术的日益发展,基于分数时延技术的阵列天线波束形成方法由于其能明显改善宽带大孔径阵列天线波束指向的“色散效应”这一优越特性,必将会得到越来越广泛的工程应用。

[1] 张光义.相控阵雷达原理[M].北京:国防工业出版社,2009.

[2] 王德纯.宽带相控阵雷达[M]. 北京:国防工业出版社,2010.

[3] T B Deng. Symmetry based low-complexity variable fractional-delay FIR filters//IEEE International Symposium on Communications and Information Technologies, 2004:194-199.

[4] 范占春.宽带数字阵数字时延及移相技术研究[D].电子科技大学,2008.

Digital time-delay technology of broadband digit array and its hardware implementation

WU Wei,ZHANG Wen-xing

(No.724 Research Institute of CSIC, Nanjing 211153)

The digital beam forming (DBF) method is studied based on the digital time-delay technology, and verified to be correct through the theoretical deduction and the simulation. The hardware implementation and the resource evaluation indicate the feasibility of the hardware.

broadband phased array; beam forming; digital delay

2014-04-12;

2014-05-15

吴卫(1977-),男,工程师,硕士,研究方向:雷达信号处理技术研究;章文星(1969-),男,高级工程师,研究方向:雷达结构设计。

TN958.92

A

1009-0401(2014)02-0030-05