一种多通道NAND Flash阵列的坏块管理方案*

2014-09-06崔建杰

张 雯,崔建杰,张 新

(1.西安邮电大学电子工程学院,西安 710121;2.西安奇维科技股份有限公司研发中心,西安 710077)

一种多通道NAND Flash阵列的坏块管理方案*

张雯1,2,崔建杰2,张新1*

(1.西安邮电大学电子工程学院,西安 710121;2.西安奇维科技股份有限公司研发中心,西安 710077)

摘要:针对多通道NAND Flash阵列对可靠性的要求,提出一种坏块管理方案,优化坏块信息的存储和查询方法,把坏块和替换块地址映射表存储在FRAM中。测试数据证明,方案可以实现多通道NAND Flash阵列的坏块管理,保证了存储的可靠性。优化的坏块表及查询方法缩短了坏块查询时间,FRAM节省了有效块地址映射时间,同时FRAM的铁电效应,进一步提高了数据存储的可靠性。

关键词:大容量存储;坏块管理;二分法;NAND Flash阵列;FRAM

在这个信息科学飞速发展的时代,数据存储成为通信领域中不可或缺的环节,系统对存储容量和存储带宽的需求不断增加,这就使得对海量数据存储的研究成为一种必然趋势。NAND Flash存储器成本低,容量大,数据存储速率高、非易失性好,可擦除次数多,无机械机制等优势,成为海量数据存储系统的理想器件,使海量数据存储得到迅猛发展和广泛应用[1]。由于制造工艺的关系,NAND Flash在出厂时就会存在一定量坏块[2],这些固有坏块不能进行读写或擦除等操作,经厂商检测后被标记出来,存储在NAND Flash自身的备用区。同时,因NAND Flash擦写寿命一般不超过100万次[3],使用一定时限后必然会产生使用坏块,这些坏块的存在会使系统的可靠性下降。对比几种NAND Flash坏块管理方法,提出一种针对多通道NAND Flash阵列的坏块管理方案,优化了坏块和替换块地址映射表及查表方式,使用了铁电存储器,保证数据存储可靠性的同时,明显缩短了坏块信息的读取时间,提高了系统对数据的处理速度。

1 NAND Flash的物理结构

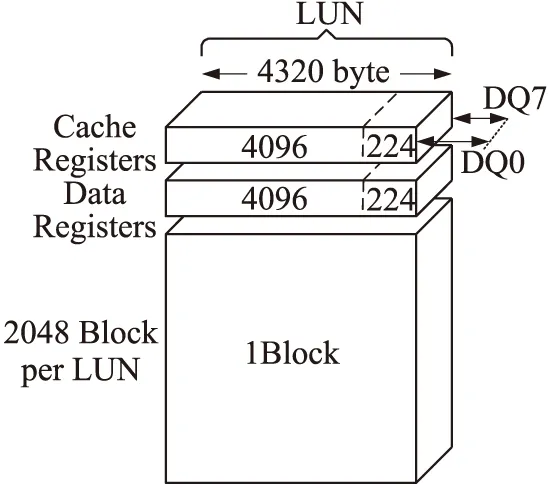

以美光公司的MT29F64G08AJABA芯片为例,一个逻辑单元LUN(Logic Unit Number)的物理结构如图1所示。MT29F64G08AJABA是由4个LUN组成,其中1 Page=4096 byte+224 byte),1 Block=128 Page=512 kbyte+28 kbyte,1 LUN=4096 Blocks=2 Gbyte+112 Mbyte,即 MT29F64G08AJABA容量为(8 Gbyte+448 Mbyte),这表示用户可以进行读写、擦除等操作的存储空间为8 Gbyte,而后的448 Mbyte空间是厂家为芯片自身预留的备用区,这部分区域,是用户不能进行操作的,只能用来存储厂家检测并标记出的固有坏块信息。[4]

图1 NAND Flash物理结构图

NAND Flash的基本操作主要有3种:读、写和擦除,读操作和写操作都是按页操作的,擦除是按块操作的,NAND Flash本身具有较快的写入与擦除速度,这是它适合大容量存储的原因之一。[5]NAND Flash存储器是一个非易失性半导体,每次进行写操作之前都需要先进行擦除操作,NAND Flash存储器的使用顺序是擦除、编程、多次读取、擦除,依次循环。

2 NAND Flash坏块管理常见方法

2.1坏块出现的原因

坏块是指一个块内含有一位或多位数据单元,无法进行读或写或擦除或纠错码ECC(Error Checking and Correction)校验等操作的块单元,一般分为固有坏块和使用坏块。由于生产工艺的限制,通常NAND Flash在出厂时允许2%数量的坏块存在,称为固有坏块。在芯片的长期使用过程中,由于存储单元错误、地址线错误等,使某些块频繁地写入或擦除,超出了NAND Flash支持的操作次数,使NAND Flash某一部分扇区损坏而出现坏块,称为使用坏块。

如果数据信息存储在NAND Flash的坏块中,会导致数据信息的错码或丢失,造成不必要的损失,同时也降低了系统的稳定性和可靠性,所以对NAND Flash的存储方式和存储区域的管理是非常有必要的。

2.2坏块管理的常见方法

坏块管理的主要思想就是坏块识别、存储、跳过和替换。目前已经有许多专家学者探索了坏块的各种处理方法,常见的有以下几种:(1)在现场可编程门阵列FPGA(Field Programmable Gate Array)内建立片上随机存储器RAM(Random Access Memory),每次操作完成后,通过状态寄存器的内容判断操作是否正确,若不正确则判定为坏块,须将整块数据搬移到有效块单元中。[6]在高速实时数据传输中,不可能花费很长时间进行数据搬移,此方法不仅对速度有限制,而且受到FPGA内部RAM资源的限制。(2)在FPGA内部生成坏区文件,将检测到的坏块信息写入FPGA的只读存储器ROM(Read Only Memory)中,将使用的Flash阵列坏块生成坏区文件,当Flash阵列中的一片遇到坏块时,则整个阵列地址同时跳过这个坏块。[7]这种设计仅仅是将坏块标记并跳过,必然损失了Flash阵列的存储空间。(3)在FPGA内部建立RAM,存储所有有效块地址,在每次写操作之前,调用检测有效块地址函数,写操作时直接提取有效块地址。[1]此方法明显需要占用足够大的RAM空间,而且给软件设计增加了难度。在常见的坏块管理方案中通常都是针对单通道或单个NAND Flash而言,本设计提出的优化方案则是针对多通道NAND Flash阵列而言。

3 多通道NAND Flash阵列的坏块管理方案

3.1多通道NAND Flash阵列

NAND Flash单片容量已经远远不能满足人们的需求,越来越多的电子领域采用多片NAND Flash级联或组成阵列使用以扩大存储空间和提高数据吞吐量。NAND Flash写入的平均时间为200 μs,最大等待时间为700 μs,[4]若按顺序依次操作数据的写入速度就会很慢,无法满足实际的使用要求。这就引入了一个新的问题,如何提高数据的读写速度,采用多通道NAND Flash阵列,可以有效的解决这一问题。

在多通道NAND Flash阵列中,每个闪存通道都有自己独立的通道缓存、时序模块、数据总线和控制总线,这样就可以使得每个通道并行工作互不影响,由硬件逻辑来实现数据到各个通道上的自动分配,大大提高了数据的传输速度。整个NAND Flash阵列由多个通道构成,每增加一个通道,理论上数据的读写速度会增加一倍,突破闪存的极限读写速度限制,在扩大存储容量的同时,也可以成倍提高数据的吞吐率。设计的NAND Flash阵列在读取数据的时候,通道仲裁和数据分配单元可以一次启动多个通道进行数据读操作,每个通道读取数据后都存放在对应的通道缓存中,由通道仲裁和数据分配单元负责把数据读出向前传递。写数据严格按照芯片手册提供的最大等待时间来操作,这样可以保证在恶劣的外部环境下,数据依然能够可靠的写入到芯片中。这种由单通道构成的多通道NAND Flash阵列,每增加一个单通道,便会使构成的多通道NAND Flash阵列的读写速度比原来的单通道NAND Flash级联读写速度增加一倍,从而大幅提高NAND Flash的读写速度。

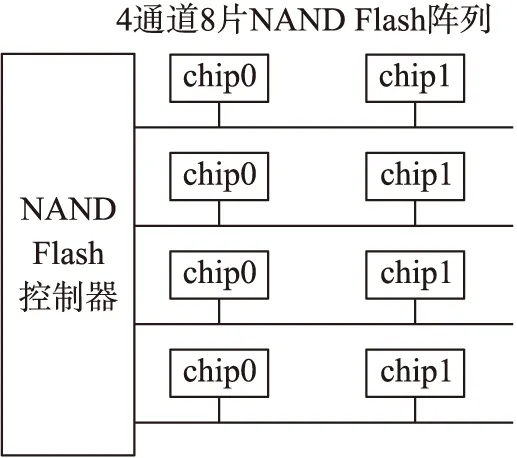

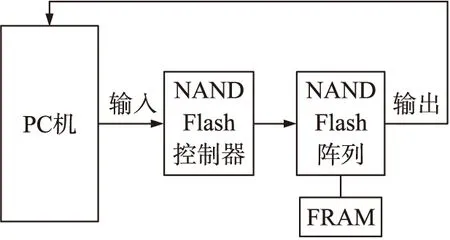

以4通道8片NAND Flash阵列为例(下文中都用此阵列为例),选用的NAND Flash控制器数据总线宽16位。如图2 NAND Flash阵列所示,将两片NAND Flash芯片构成16位数据总线,每个通道中的NAND Flash芯片通过级联共享一条数据总线、控制总线和片选信号。每个通道都有自己独立的通道缓存,独立的时序模块,独立的数据总线和控制总线,所以这4个通道可以并行工作,互不影响。当写完chip0后,让其处于写等待状态,立即转入对chip1的操作,并不因为chip0处于写等待状态而使总线空闲,以此类推,当循环操作一周后,chip0写等待状态完成,又进入下一轮操作,这就是流水线管理方法,它可以保证每个通道的数据总线总是处于繁忙状态,从而提高了每个通道的数据传输速度。

图2 NAND Flash阵列示意图

3.2铁电存储器

铁电存储器FRAM(Ferroelectric Random Access Memory)是基于铁电晶体的铁电效应进行信息存储的一种新型非易失性存储器。铁电效应是指在铁电晶体上施加一定的电场时,晶体中心原子在电场的作用下运动,并达到一种稳定状态;当电场从晶体移走后,中心原子会保持在原来的位置的特性。[8]根据这一特性将铁电薄膜与CMOS工艺集成形成一种铁电存储产品,同时还具有RAM的特性。[9]因此,FRAM既可以像RAM一样操作,读写功耗极低,又不存在如EEPROM的最大写入次数问题,同时,它还具有速度快、耐久度高、抗辐射能力强等优点[10]。最重要的是FRAM中不存在坏块,在突发掉电事故时,因为铁电效应的稳定性,数据信息并不会丢失,这就极大的提高了系统的可靠性。本设计使用FRAM来存储坏块信息,既可以解决在FPGA内部存放坏块信息带来的RAM资源紧张的问题,也可以解决在NAND Flash中存放坏块信息带来的写入速度受限制的问题,从而确保坏块信息和块映射信息可以快速保存,且不会因掉电而丢失。

3.3坏块识别

NAND Flash存储器在出厂时厂家会标记出固有坏块,通过读所有NAND Flash的备用区,可以识别并标记出固有坏块。在第1次使用NAND Flash时,创建坏块和替换块地址映射表,保存在FRAM中。在以后的使用中,由于不断地擦写等操作会出现使用坏块,坏块识别的常用方法有以下3种:(1)将NAND Flash擦除,然后写满全0,再次擦除,若出现非FFh的,则标记为坏块;(2)在写入数据时,若状态返回为写入失败,则标记为坏块;(3)在擦除数据时,若状态返回为擦除失败,再次擦除仍显示失败,标记为坏块。这3种方法都要保证足够的执行时间,否则因为时间不够系统也会报错,造成坏块的误判。

3.4坏块的存储

3.4.1坏块存储的优化方案

设计的四通道8片NAND Flash阵列,每片NAND Flash有4096个块,这就需要用12 bit表示它们的地址,而片选信号用1 bit表示,通道号用2 bit表示,这样确定一个块的具体地址,需要2 byte大小。由厂家的技术手册可知一般坏块数不会超过总块数的20%,因此NAND Flash阵列设置替换块区大小为总容量的20%。本设计总共容量64 Gbyte,按比例替换块区留12 Gbyte,即预留替换块数为12×1 024/4(每块的大小为4 Mbyte)=3 072块。这样,设计中支持建立的坏块和替换块地址映射表最大为3 072(块数)×2 byte(坏块地址大小)+3 072(块数)×2 byte(替换块地址大小)=12 kbyte,即选用16 kbyte的FRAM就可以满足系统要求。

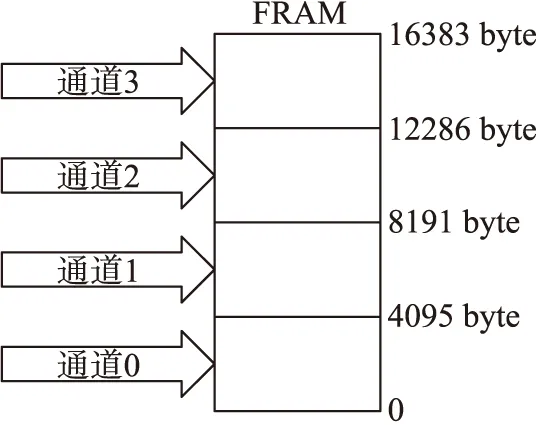

图3 通道与坏块信息存储对应关系示意图

设计的是四通道存储阵列,为了方便坏块信息的查找,将FRAM也平均划分为4个空间,即每个空间大小为4 kbyte,定义每个通道对应相应的存储空间。根据技术手册估算出每个通道的坏块数量最多不超过768块,假设768块均坏,则对应的坏块信息需要768(块数)×2 byte(坏块地址大小)+768(块数)×2 byte(替换块地址大小)=3 072 byte空间存储,故预留的4 kbyte空间足够使用。各通道与FRAM的存储关系如图3所示。这样的设计可以有效提高后续坏块查找的效率,缩短查找时间。

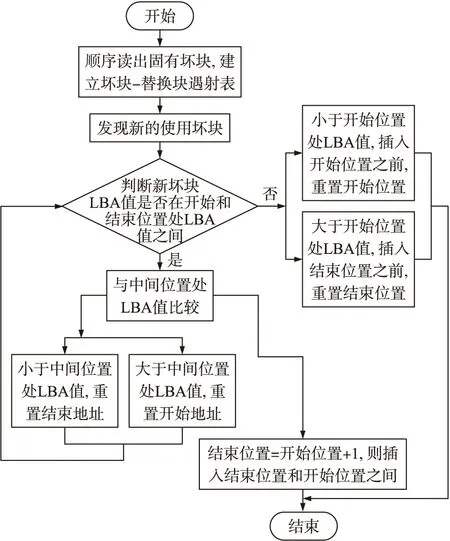

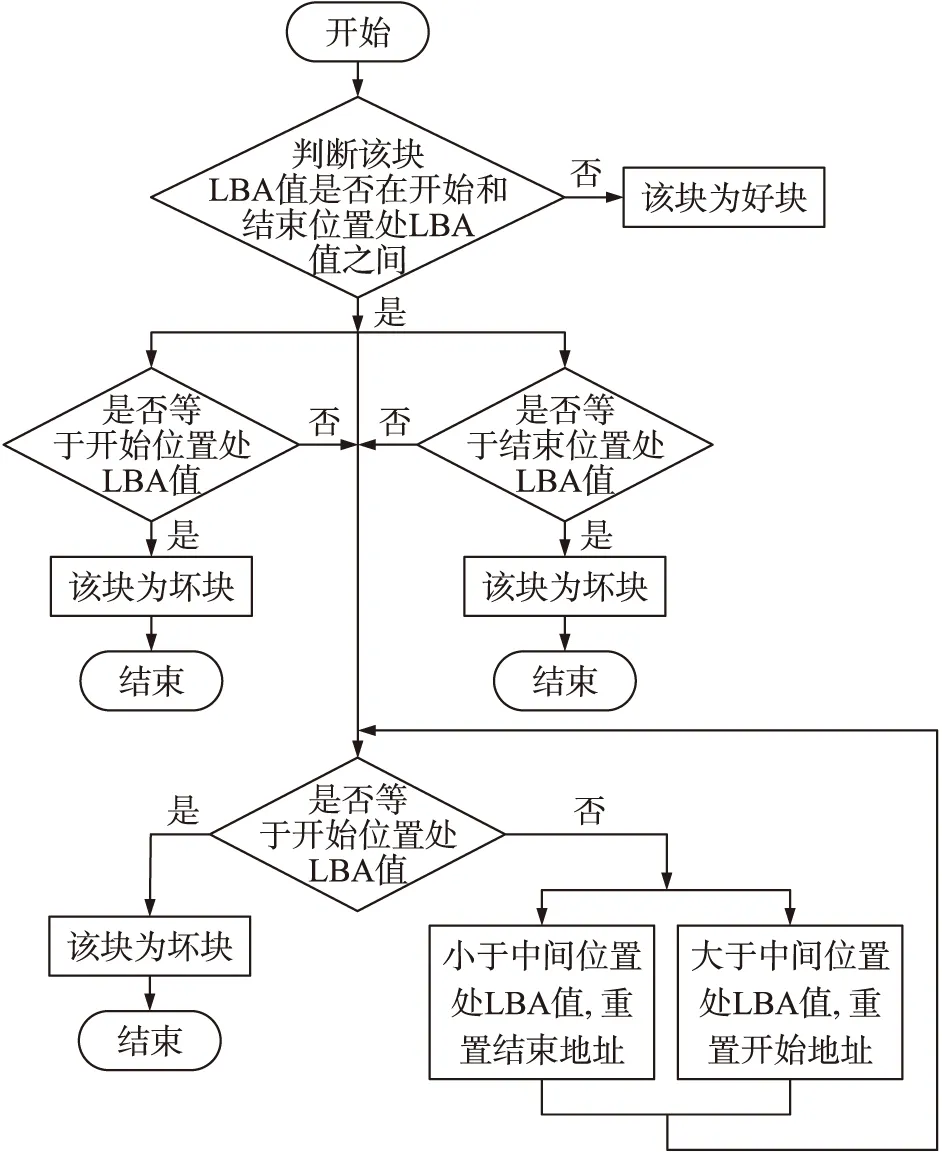

3.4.2二分法存储坏块信息

将初始化时建立在FRAM中的坏块和替换块地址映射表导入到NAND Flash控制器的内存中,再将3.3坏块识别过程中标记出来的使用坏块插入到FRAM的坏块和替换块地址映射表中。为了方便以后的坏块查找,设计采用二分法将新的坏块和替换块地址映射插入原有映射表中,流程如图4所示,流程图是针对单通道而言的,即每个通道在对应的FRAM存储空间独立实现该过程。因为初始化时,固有坏块是按序扫描的,所以最初创建的坏块和替换块地址映射表是升序排列,满足二分法的基本条件。最后将更新过的坏块和替换块地址映射表重新导入FRAM中,一直到下次发现新的坏块时,再执行上述过程。设计存储的仅为坏块信息,相比于常见的存储所有块的状态信息,初始化时并无优势,但是明显缩短了坏块信息建立的时间,加快了坏块信息建立的速度。

图4 二分法插入坏块地址和替换块地址流程图

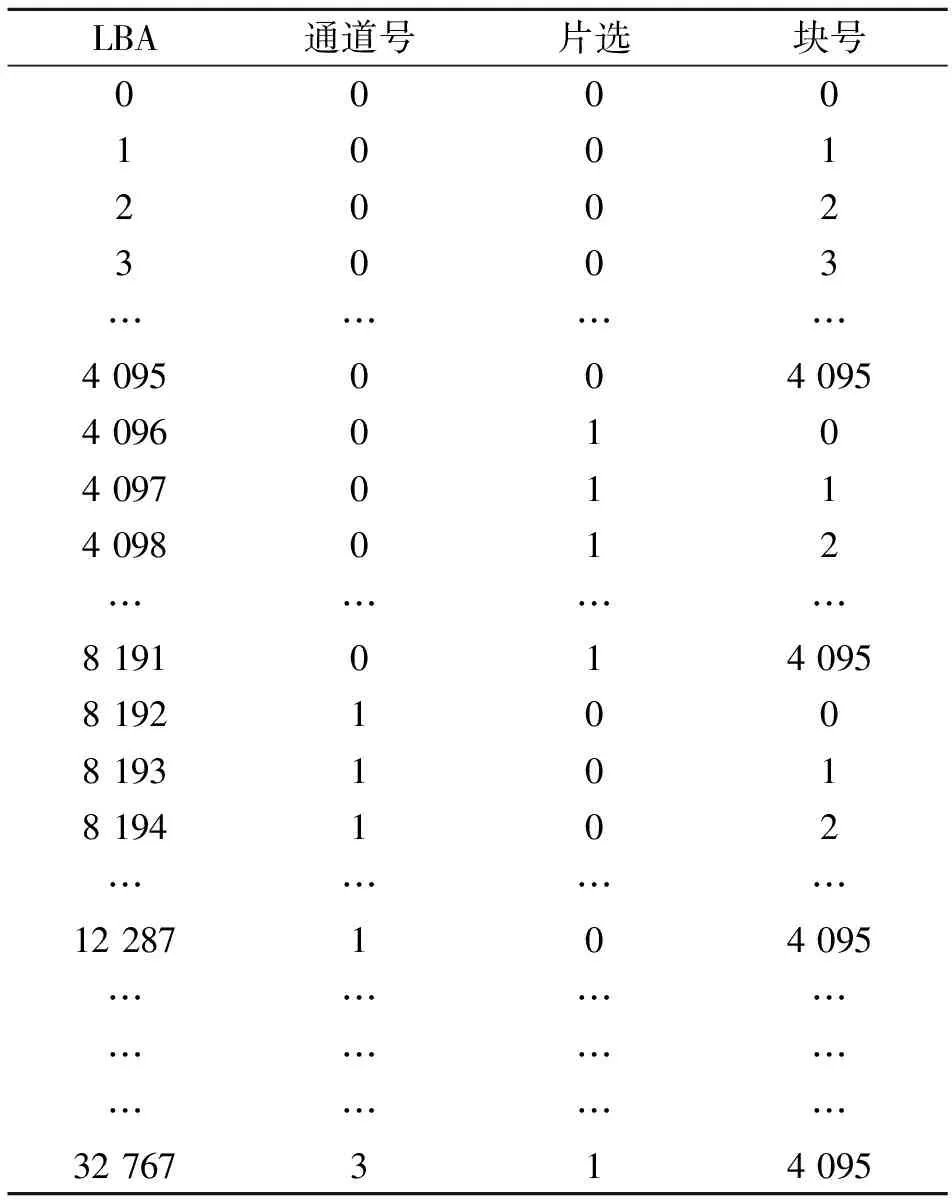

设计使用的块号信息都是用是逻辑块地址LBA(Logical Block Addressing)表示的,通过逻辑地址和物理地址的映射查出对应的物理块地址PBA(Physical Block Addressing),最终确定NAND Flash的坏块具体位置。LBA-PBA映射关系如表1所示。

归纳出逻辑地址和物理地址的对应关系公式为:LBA=通道号×8 192+片选×4 096+块号。

因为FRAM具有铁电效应的优良特性,保证了坏块和替换块地址映射表不会因掉电而丢失,有效提高了NAND Flash阵列存储的可靠性,并且FRAM最大读写时间为130 ns[11],相比较于传统方法将坏块和替换块地址映射表存放在NAND Flash阵列专门划分的坏块区中,读写速度有明显的提高,也节省了NAND Flash阵列的存储空间。

表1 LBA-PBA映射表

3.5坏块的跳过和替换

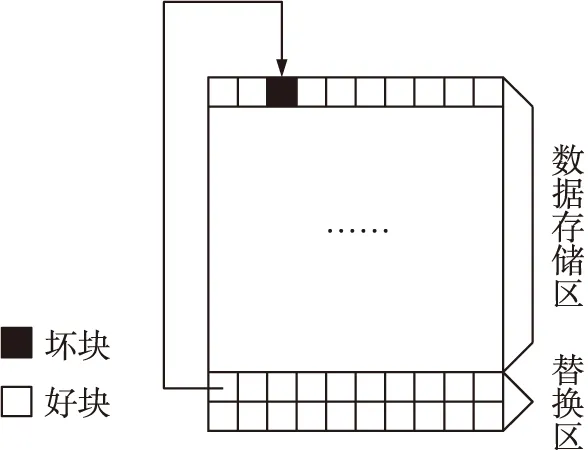

在写数据的过程中,若发现坏块,为了不影响系统的写速度,仅仅将坏块标记出来然后跳过,继续在下一个好块中进行当次写操作。设计的NAND Flash阵列通道内为流水线操作,当chip0写完进入写等待状态,利用这个空闲时期,将刚才写操作过程中标记的坏块找出来,由于在同一块中,某一页的写入操作失败,并不会影响其他页数据的正确性,因此可以重新写入无效页的正确数据,与这一块中其他页的数据一起搬移到替换区中的有效块里,并更新FRAM中坏块和替换块地址映射表,在下次使用时,就可以直接将数据写入更新的物理地址,替换过程如图5所示。这一过程的完成并不影响chip1的任何操作,所以从微观意义上讲也是时间的并行操作,给整个系统节省时间,也就是提高整个系统的存储速度。当发现坏块时,顺序从替换区取一块有效块替换,将替换区中替换块的地址指针+1,然后将更新的地址信息写入FRAM中保存。实现的数据结构如表2所示。

图5 替换过程示意图

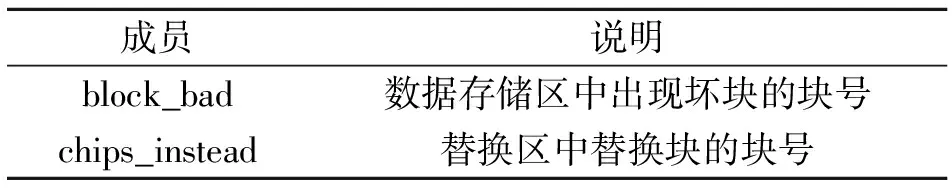

表2坏块替换实现数据结构说明

成员说明block_bad数据存储区中出现坏块的块号chips_instead替换区中替换块的块号

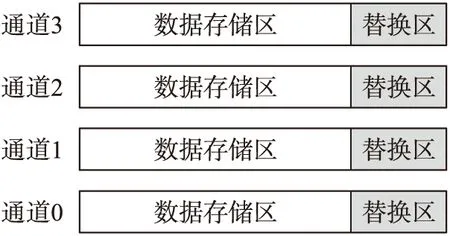

上述坏块的替换过程都是针对单通道而言的,即每个通道内部各自实现着替换过程。每片NAND Flash为8 Gbyte,依据技术手册可知坏块数最多不超过1.6 Gbyte,即每片NAND Flash预留1.6 Gbyte为替换块区,多通道存储空间分布的示意图如图6所示。

图6 通道内存储空间分布示意图

图7 二分法查找坏块信息流程图

为了方便坏块信息的查询,本设计使用二分法查找坏块信息,单通道实现的流程图如图7所示。由于创建坏块和替换块地址映射表的时候就按照升序的方式排列,所以查找坏块信息时,无需再考虑顺序问题,满足二分法的使用基本条件。使用二分法查找坏块信息相较于轮询法[12],查找更快捷,提高了存储系统的工作效率,有效节省了每次使用前格式化的时间。而每个通道对应相应的坏块信息存储空间,虽然会出现浪费空间的现象,但是相比于把整个系统的坏块信息建立一张坏块和替换块地址映射表,查找的长度大大缩短,有效减少了查询次数,进一步提高了这个系统的工作效率。

4 实验仿真

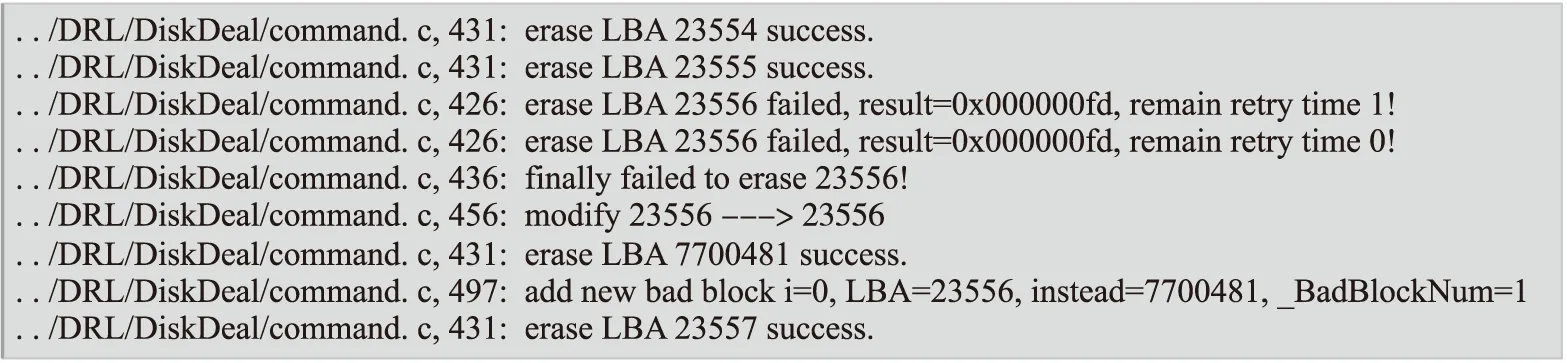

实验仿真时搭建一个简易的系统,系统框图如图8所示,实验主要是为了证明上述方法可以有效实现多通道NAND Flash阵列的坏块管理。通过PC机输入一组数据,执行连续擦写操作,通过SSCOM3.2软件监测,如图9软件监测图所示。擦除成功时显示“SUCCESS”表示该块为有效块。但是明显看到擦除块23556时,显示“failed”,表示擦除失败,重复又擦除了一次,同样显示“failed”擦除失败,确定块23556为坏块,并用替换区的块7700481替换。由此可以证明NAND Flash阵列的坏块识别、替换功能正常,可以实现设计初衷。

图8 实验系统示意图

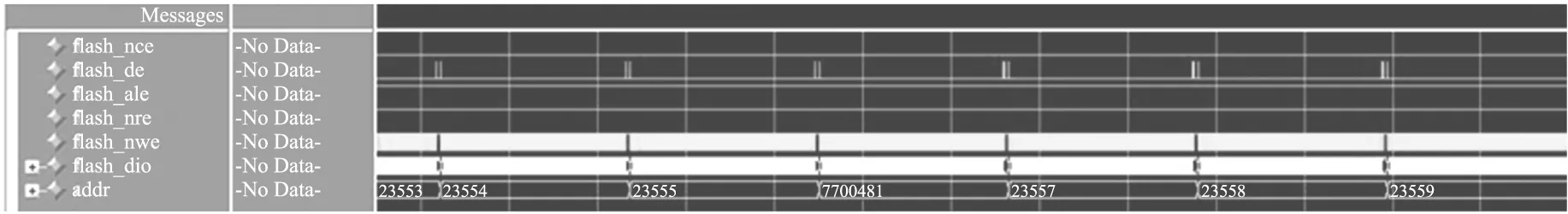

重新执行写操作时,可以由图10 Model Sim仿真图看出,块23555与块23557之间为块7700481,表示执行替换操作成功,再次证明优化的多通道NAND Flash阵列坏块管理方案可以实现有效的坏块管理。

5 结语

随着多通道NAND Flash阵列存储技术的日益完善,它的存储密度越来越大,而相应的体积、功耗和成本却越来越小,使得多通道NAND Flash阵列存储技术有广泛的市场前景。本文面向多通道NAND Flash阵列存储提出一种优化的坏块管理方案,多通道并行存储数据,通道内独立管理坏块,使用FRAM存储坏块和替换块地址映射表。通过仿真实验,证明了方案的可行性,故这一方案可以优化多通道NAND Flash阵列存储技术,进一步提高存储系统的工作效率和可靠性。

图9 软件监测图

图10 Model Sim仿真图

参考文献:

[1]舒文丽,吴云峰,赵启义,等.NAND Flash存储的坏块管理方法[J].电子器件,2011,34(5):580-583.

[2]周军.NAND Flash的坏块管理设计[J].单片机与嵌入式系统应用,2010(9):15-20.

[3]林刚.NAND Flash坏块管理算法及逻辑层驱动设计[D].西安:西安电子科技大学,2009:25-61.

[4]Micron Technology.MT29F64G08A[J/K/M]ABA NAND Flash Memory Datasheet[Z].2009.

[5]宁飞.大容量存储中NAND Flash坏块的管理方法[J].电子测试,2010(12):64-68.

[6]王珺.高速大容量固态存储系统的实现与应用[D].西安:西安电子科技大学,2006.

[7]吴萌.一种高速大容量图像存储系统设计[D].西安:中国科学院西安光学精密机械研究所,2009.

[8]百科.铁电存储器[EB/OL].(2013-04-27)[2013-07-16].http://baike.baidu.com/view/923780.htm.

[9]廖贵成,王龙,史文余.高性能Flash/FRAM混合数据存储系统的设计及应用[J].微电子学与计算机,2010,27(12):127-129.

[10]张德凯,徐建龙,任天令.1Kbit铁电存储器电路设计技术研究[J].半导体技术,2012,37(11):878-882.

[11]肖月宁.用于计算机系统的铁电随机存储器的研究进展[J].电脑编程技巧与维护,2011(2):92-92.

[12]贾源泉,肖侬,赖明澈,等.基于NAND FLASH的多路并行存储系统中坏块策略的研究[J].计算机研究与发展,2012,49(增刊):68-72.

张雯(1989-),女,汉族,陕西西安人,西安邮电大学硕士研究生,研究方向为通信电路系统,vivian890202@163.com;

崔建杰(1979-),男,汉族,湖北襄阳人,西安奇维科技股份有限公司,硬件工程师,从事固态存储产品研发设计,cuijianjie@keyway.com.cn;

张新(1968-),女,博士,汉族,甘肃敦煌人,西安邮电大学,教授,从事网络计算与网络管理研究,zhx@xupt.deu.cn。

BadBlockManagementMethodofMulti-ChannelNANDFlashArray*

ZHANGWen1,2,CUIJianjie2,ZHANGXin1*

(1.School of Electronic Engineering,Xi’an University of Posts and Telecommunications,Xi’an 710121,China;2.R&D Center,Xi’an Keyway Technology Co.,Ltd,Xi’an 710077,China)

Abstract:Aiming at the requirement about the reliability of the multi-channel NAND Flash array,a bad block management method is proposed.The method optimizes the bad block information storage and query methods.A FRAM stores the LBA-PBA address mapping table.The data of tests shows that the method can achieve multi-channel NAND Flash array of bad block management to ensure the reliability of storage.Optimized bad block creation method reduces the bad block query time.The FRAM saves the time of the valid block address mapping.And with the ferroelectric the reliability of data storage is further improved.

Key words:large capacity storage;bad block management;dichotomy;NAND Flash array;FRAM

doi:EEACC:014010.3969/j.issn.1005-9490.2014.05.004

中图分类号:TP333

文献标识码:A

文章编号:1005-9490(2014)05-0816-06

收稿日期:2013-09-11修改日期:2013-09-25

项目来源:西安市科技计划基金项目(CXY1117[5])