一种高CMRR和PSRR的共源共栅放大器

2014-09-03李新,黄璜,王龙

李 新,黄 璜,王 龙

(沈阳工业大学 信息科学与工程学院,辽宁 沈阳 110870)

一种高CMRR和PSRR的共源共栅放大器

李 新,黄 璜,王 龙

(沈阳工业大学 信息科学与工程学院,辽宁 沈阳 110870)

针对传统运算放大器共模抑制比和电源抑制比低的问题,设计了一种差分输入结构的折叠式共源共栅放大器。本设计采用两级结构,第一级为差分结构的折叠式共源共柵放大器,并采用MOS管作为电阻,进一步提高增益、共模抑制比和电源电压抑制比;第二级采用以NMOS为负载的共源放大器结构,提高增益和输出摆幅。基于LITE-ON40V 1.0 μm工艺,采用Spectre对电路进行仿真。仿真结果表明,电路交流增益为125.8 dB,相位裕度为62.8°,共模抑制比140.9 dB,电源电压抑制比125.5 dB。

折叠式共源共栅放大器;高增益;共模抑制比;电源抑制比

当今,模拟集成电路的发展日新月异,作为模拟系统的核心模块,运放的放大倍数、电源抑制比和共模抑制比直接影响整个系统性能的好坏。设计者们需要不断完善运算放大器的设计来适应模拟集成电路的发展要求。

高性能运放的设计通常需要考虑电源电压、工艺限制和温度等因素,并兼顾运放性能的要求,如高的放大倍数、电源抑制比、共模抑制比等方面。套筒式共源共栅运放放大倍数大,但其输出摆幅小,增加极点,很难以输入与输出短路的方式实现单位增益缓冲级。为了克服套筒式放大器缺点采用一种折叠式共源共栅运算放大器,折叠式共源共栅运算放大器增益高、摆幅大,增大了输出电阻,但会导致驱动能力、速度和输出极点频率的下降,为了避免这些问题,采用两级运算放大器。第一级为折叠式共源共栅放大器,第二级为共源放大器,采用两级运算放大器级联增大输出增益和摆幅[1],同时速度也比单极速度快。

1 放大器结构

放大器的输入级是差分结构的折叠式共源共柵放大器,有较高的增益、共模抑制比,具有很强的抗干扰能力,采用MOS管做电阻,能提高电源电压抑制比;输出级采用以N管为负载的共源放大器,在提高增益的前提下能增大输出摆幅[2];偏置电路为镜像电流源结构,为运放晶体管提供合适的工作电压。运算放大器保证了直流工作点,增大了第二级放大器输入管的跨导,提高了增益和次级点的频率;从而提高相位裕度,增强稳定性。

1.1 高CMRR和PSRR电路

本设计电路结构输入级采用差分折叠式共源共柵电路结构。差分结构能提高电路的共模抑制比,同时抑制环境噪声和抗干扰能力强;折叠式共源共柵输入、输出摆幅和增益相对较高,并且适用于单位增益缓冲级。综合以上优点输入级采用差分折叠式共源共柵电路。

折叠式共源共栅运算放大器电路图如图1所示,输出短路电流约等于P12的漏电流,因此从N10的源端往里看,所得的阻抗即:(gmn10+ gmbn10)-1|| ron10通常远低于rop12||ron8。由输出电阻公式可得Rout= {[(gmn10+gmbn10)ron10(rop12+ron6)]||[(gmp9+gmbp9)rop9rop17]}[3],由式(1)可得折叠式共源共栅运算放大器电路增益为:

图1 运算放大器Fig.1 Operational amplifier

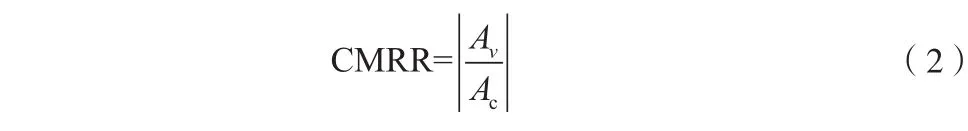

采用折叠式共源共栅运算放大器有一个重要的特点就是对共模扰动影响的抑制能力,由于运放采用两级结构,第一级为双端输入单端输出对共模抑制比影响较大,第二级为单端输入、单端输出不会影响运算放大器共模抑制比。图1中所示运算放大器,共模抑制比公式为:

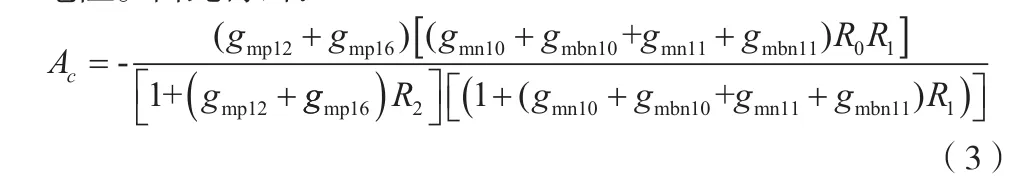

CMRR是由共模输入电压的单位变化引起的输入失调电压[4],上式中Av为运算放大器增益,Ac为运放共模增益,在实际电路中,运算放大器不能达到完全对称,电流源的输出阻抗也不可能无穷大,因此共模输入电压的变化会影响输出电压的变化。为了计算图1电路共模增益Ac可以将其电路转化为图2输出开路等效电路。

其中R0是P19、P17、P9、P13的等效电阻,阻值为[(gmp13+gbp13)ro13ro19]||[(gmp9+gbp9)ro9ro17];R1是P12、P16、N6、N9并联等效电阻,R1阻值为 ron6||ron9|| rop12||rop16,R2为尾电流P11电阻。由此得出:

图2 等效电路Fig.2 Equivalent circuit

由式(2)、(3)、(4)可得出:

从上式可以看出,使用共源共栅结构能提高差分放大器的共模抑制比,在保证运放放大倍数的前提下通过调整运放参数能提高共模抑制比。

实际电路中电源也存在这噪声,在设计运放时要考虑电源噪声对输出信号的影响,电源抑制比表达公式:

由式(5)可以看出,通过调整Av和ADD能改变电源电压抑制比。在图1运算放大器中,电源电压波动时,通过P19、P13管电压会有变化,从而影响输出电压变化。传统折叠式共源共栅放大器P19、P13的栅极电压是由P9和N10之间串联电阻分压所提供,制造电阻过程中会浪费版图资源,同时走线比较长会影响P19、P13的栅极电压,从而影响电源电压抑制比。而本设计P19、P13的栅极电压是由P10、P21、P14、P15、P22、P18管串联且栅端和N10漏断相连提供,其中P18晶体管的漏端和栅端电压相等,VDS电压等于VGS,P18晶体管工作在饱和区,也由此可知各晶体管工作在饱和区,采用这种结构可以减小版图面积,并且器件之间的匹配性良好,也减小了走线的长度,抗干扰能力强,有效提高电源抑制比,当电源电压波动时会改变P10、P21、P14、P15、P22、P18串联电阻,影响P13管的栅极电压,从而控制电源电压波动通过P13管对输出电压的影响,进而有效的提高电源电压抑制比。

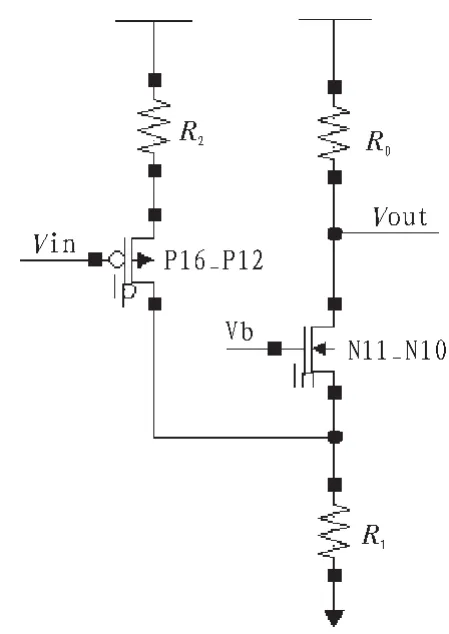

1.2 第二级电路结构

第二级电路如图3所示,为了考虑输出摆幅大和增益高,采用NMOS做负载的共源放大器作为输出级。其中N4管作为恒流源负载,输入级的折叠式共源共栅运算放大器输出接到输出级P4管的栅极,这样能很好的满足输出摆幅要求。

图3 第二级电路Fig.3 The second stage circuit

在图3中,在输入级和输出级端之间添加密勒补偿电容和补偿电阻。运用密勒补偿技术[5],可以设计出具有良好频率特性的高性能运放。通过密勒补偿电容Cp2p3,使主极点向原点移动,输出极点向非原点方向移动,当其非主要极点重合时可以达到很好的补偿效果。采用密勒补偿电阻Rm,可以使零点移动到左半平面,消除第一个非主极点,保证系统的稳定性[6]。通过设计密勒补偿电阻来调节系统零极点。将零点移动到左半平面,并且和输出极点相抵消,那么要求满足一下关系:

由(6)式可以计算出米勒补偿电阻Rm和电容Cp2p3,其参数如表1所示。采用MOS管做电容好处是,极大地节省了芯片面积,降低了芯片的制造成本,抗干扰能力强,由于电容版图面积大且浪费版图资源可以采用P2、P3管并联,这样相当于电容的串联。相位裕度在电路设计中很重要,用来衡量系统的稳定性。运算放大器增益的相位在增益交点频率时[7],与-180度相位的差值。运算放大器[8]常常被用于带负反馈的系统中,可用在单位缓冲器中,起到阻抗变换作用。根据线性系统理论,一个负反馈系统要稳定,相位裕度要大于60°。

表1 器件参数Tab.1 Device paramerers

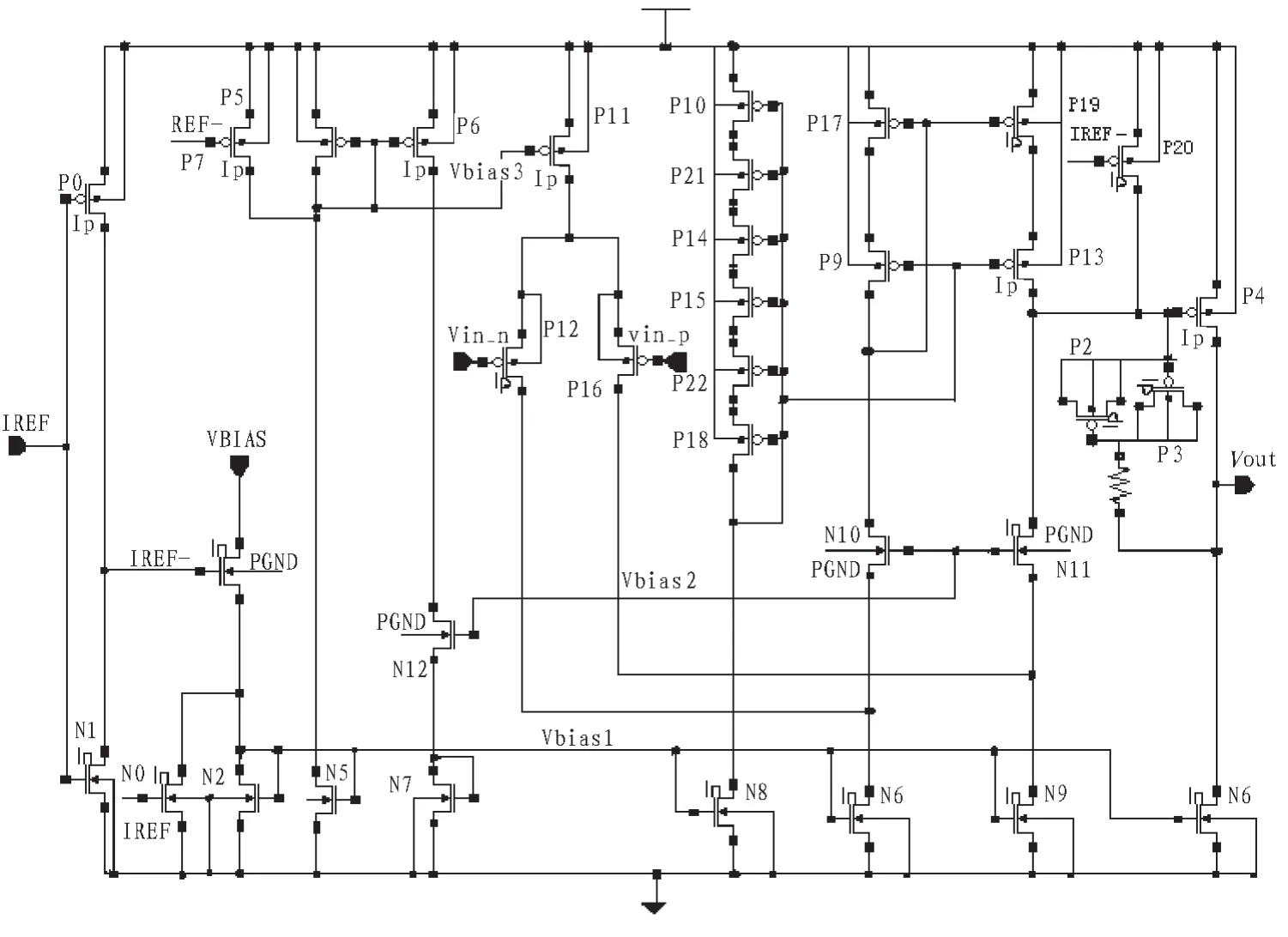

1.3 整体电路结构

运算放大器的整体电路结构如图4所示,其中输入端口为:IREF、VBIAS、Vin_n、Vin_p,输出端口为:Vout,电源电压VDD和GND。其中IREF为控制信号当为低电平时电路正常工作,当为高电平时通过控制N3、P5和P20晶体管工作,有效控制其它晶体管工作,这样可以减少运算放大器静态时的功耗,使运算放大器的功耗有效的降低。

2 仿真结果及其版图

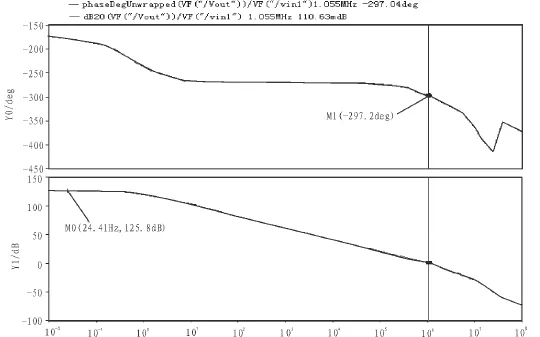

基于LITE-ON 40V的1.0μm CMOS的BCD工艺,使用Cadence公司的模拟仿真工具Spectre对电路进行仿真,增益达到125.8 dB,相位裕度62.8°,增益及其相位仿真结构如图5所示。

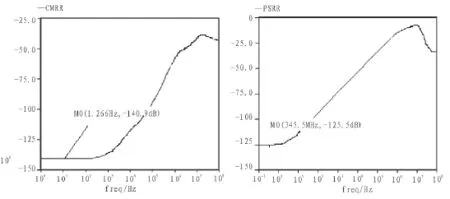

采用折叠式共源共栅放大器,共模抑制比达到140.9dB,电源抑制比达到125.5dB,仿真结果如图6所示。

基于LITE-ON 40V的1.0um CMOS的BCD工艺进行版图设计,放大器版图如图7所示。由于电路没有进行单独流片,而是应用于电源管理芯片内部,流片后对电源管理芯片进行测试性能稳定,可知本设计运放满足性能要求。

图4 运算放大器整体电路图Fig.4 Complete circuit of the operational amplifier

图5 增益和相位曲线Fig.5 Amplitude and phase curves

3 结束语

设计一种高共模抑制比和电源抑制比的折叠式共源共栅运算放大器,在较高的增益前提下,大大提高了电源电压抑制比和共模抑制比;折叠式共源共栅放大器结构简单,提高了输出摆幅s。采用Cadence公司的模拟仿真工具Spectre对电路进行仿真。该电路结果表明,电路交流增益达到了125.8 dB,相位裕度为62.8°,共模抑制比140.9 dB,电源电压抑制125.5 dB,本设计折叠式共源共栅运算放大器满足设计要求。

[1] Arora N,Singh S M P,Singh N B.High gain and phase margin cmos operational amplifier designs[J].International Journal,2013(8):10-12.

[2] 马琳,杨志飞,黄武康,等.一种降低高频噪声的前置全差分运算放大器[J].微电子学与计算机,2012,29(8):102-106.

MA Lin,YANG Zhi-fei,HUANG Wu-kang,et al.A kind of to reduce the high frequency noise front fully differential operational amplifier[J].Microelectronics and Computer,2012,29(8):102-106.

[3] 拉扎维.模拟CMOS集成电路设计[M].陈贵灿,程军,等,译.西安:西安交通大学出版社,2002.

[4] 何乐年,王忆.模拟集成电路设计与仿真[M].北京:电子工业出版社,2008.

[5] Wilson W,Chen T,Selby R.A current-starved inverter-based differential amplifier design for ultra-low power applications[C]//Circuits and Systems(LASCAS),2013 IEEE Fourth Latin American Symposium on.IEEE,2013:1-4.

[6] 朱治鼎,彭晓宏,吕本强,等.高性能折叠式共源共柵远算放大器的设计[J].微电子学,2012,40(2):146-149.ZHU Zhi-ding,PENG Xiao-hong,LV Ben-qiang,et al.Sharing of high-performance folding source gate far amplifier design[J].Microelectronics,2012,40(2):146-149.

[7] Gray P R,Hurst P J,Lewis S H,等.模拟集成电路的分析与设计[M].张晓林,等译.高等教育出版社,2005.

[8] 杜继业,宋岩,罗通顶.像增强器高速选通脉冲发生器[J].现代应用物理,2013(3):299-302.LIN Ji-ye,SONG Yan,LUO Tong-ding.As intensifier high-speed strobe pulse generator[J].Modern Applied Physics,2013(3):299-302.

The high CMRR and PSRR folded-cascode operational ampli fi er

LI Xin,HUANG Huang,WANG Long

(Information Science and Engineering,Shenyang University of Technology,Shenyang 110870,China)

According to the fact that common mode rejection ratio and power supply rejection ratio are usually low in traditional operational amplifier,a differential input structure of folded-cascode operational amplifier was designed.Two stages of structure was adopted in the design of the whole circuit.The first stage is a differential structure folded cascode amplifier using MOS transistors as the resistors,further increasing the gain ,CMRR,and PSRR of the circuit;The structure of common source amplifier using NMOS as load can dramatically increase the gain and output swing..Based on LITE-ON40V 1.0μm process,the Folded-cascode operational amplifier was designed and simulated by the use of Spectre.The simulation results indicate that the whole circuit can achieve up to 125.8dB gain and 62.8°phase margin .Moreover,the common mode reject ration and power supply rejection ratio are 140.9dB and 25.5dB respectively.

folded-cascode;high-gain;CMRR;PSRR

TN98

A

1674-6236(2014)11-0079-05

2013-09-16 稿件编号:201309114

李 新(1974—),男,辽宁昌图人,博士,副教授。研究方向:数模混合集成电路设计。

图6 共模抑制比和电源抑制比Fig.6 Common mode reject ratio and power supply rejection ratio

图7 版图Fig.7 Layout