基于FPGA的点阵显示电子计时器设计

2014-08-23汪小会

汪小会

(解放军电子工程学院401教研室,安徽合肥 230037)

为了使学生了解可编程逻辑器件FPGA这项新技术,解决数字电子技术实验系统性内容受实验单元教学课时制约以及设计性内容受实验室元器件储备条件限制的问题。我们尝试将数字电子技术实验与可编程器件应用相结合,在保留并规范传统内容的基础上,联系工程应用背景知识,对数字电路实验的内容进行整合,结合门电路、译码器/数据分配器、数据选择器、计数器和存储器等应用,设计了基于FPGA的点阵显示电子计时器[1]。该设计方案以“数字电子技术”和“可编程逻辑器件应用”课程相关知识为切入点,贯穿了数字逻辑功能器件的基本原理和应用方法。设计方案在FPGA器件上实现,采用图形输入方式,由“数字电子技术”课程介绍的基本模块构成。

1 设计任务要求

电子计时器是一个以8×16的LED显示屏显示24小时制模式的时、分装置,其要求如下:

(1)每个数字显示采用7×3形式,小时、分钟十位与个位数字之间空一列;

(2)小时与分钟之间分隔用上下两个点且每秒闪动(亮、暗各一次);

(3)时间调整时,调整由左至右(小时十位、小时个位、分钟十位及分钟个位)数码循环进行,待调的数字闪动。

所需的时钟信号电2MHz晶体振荡器产生,“校准/计时”选择由逻辑开关控制,“调整移位”和“校准脉冲”由按键控制。

本课题在FPGA的开发环境QuartusⅡ中进行,采用学生熟悉的逻辑符号设计方式。在QuartusⅡ图形文件编辑过程中,输入器件型号即可调出所需器件。对学过“数字电子技术”课程的学生而言使用非常方便。由于QuartusⅡ的基本元件库囊括了所有中规模集成器件,具有兆功能函数库中的参数化模块,含有所有数字逻辑功能器件[2]。这些参数化功能模块的输入、输出以及各种控制方式都可由用户设定,比如存储器的字长和字数等。学生的设计基本不受器件资源的限制,能够实现真正意义上的自主设计。

2 系统电路设计方案

2.1 电路实现方案

本系统是一个用八个行控制信号和十六个列控制信号来控制LED点阵的显示装置。系统组成的模块电路有:①八路序列信号产生器;②测量小时状态的24进制加法计数器;③测量分钟状态的60进制加法计数器;④校时/计时控制电路;⑤每位数字所需的列控信号,以ROM来实现;⑥晶体振荡器产生的信号经分频形成秒信号、分钟信号和序列信号产生器的时钟信号;⑦小时与分钟之间的分隔点(两个点每秒闪动一次)电路。

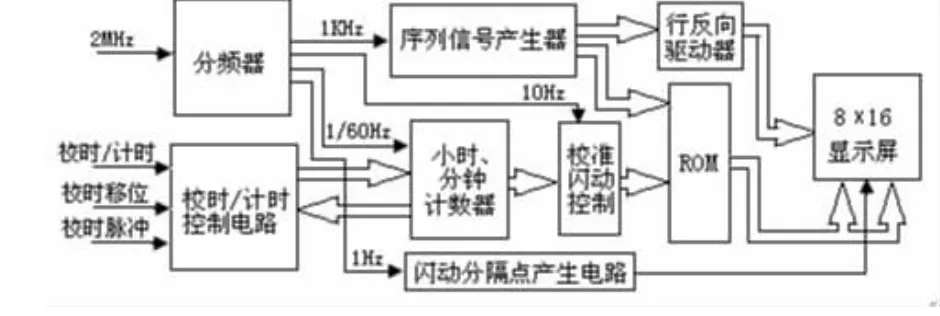

图1是系统总体框图,序列信号产生器至点阵显示屏的信号是行扫描信号,ROM和闪动分隔点产生电路信号是点阵显示屏的列控制信号。系统工作时在行扫描信号为高电平(每个时刻只有一行为高电平)时,各列根据对应点的亮与暗情况给出低电平和高电平。

图1 系统总体框图

2.2 序列信号产生电路

点阵显示屏是由8×16只LED组成,每列十六只LED,设置成八行,每行LED阳级相连接、每列LED阴级相连接,显示屏由八个行控制信号、十六个列制控信号控制工作[3]。某个LED点亮需在该管子相连的阳级那行提供高电平,与其相连的阴级那列提供低电平,序列信号由74161和74138及反向驱动器(在外围电路中)产生,电路如图2所示。时钟脉冲由2MHz连续脉冲分频产生1kHz信号。

图2 序列信号产生器电路图

2.3 列控制信号产生电路

列控制信号要根据行扫描信号为高电平时设定,需要点亮的点所对应的那列信号为低电平,否则为高电平。对于不同的数字,点亮的点是不一样的。这里用ROM来实现列信号,ROM的地址信号是小时/分钟计数器BCD码和图3序列信号产生器中计数器74161输出A2,A1和A0,输出数据作列控制信号。如数字“0”从上至下的列控信号设定为111,000,010,010,000,010,010 及 000,其它数字类似处理。ROM地址位七位,输出数据三位。系统用四个ROM模块分别作小时十位、小时个位、分钟十位及分钟个位显示的列控制信号。ROM电路从略。

小时与分钟之间分隔点那列从上至下用第四和第六个点显示且每秒内有一次亮、一次暗过程,可用第四行扫描信号X3和第六行扫描信号X5作与非运算后再与1Hz信号作与非运算。这样处理后此列由上至下第四和第六个点闪动,其它点处于熄灭状态,不亮的列控制信号设置为高电平。电路如图3所示。

图3 小时与分钟之间分隔点控制电路图

2.4 各位校准脉冲及校准位闪动控制电路

显示屏显示小时的十位、小时的个位、分钟的十位以及分钟的个位数字。“校准/计时”状态为1进行校准,此时调整位的数字以10Hz频率闪动,首先闪动的是小时十位,这时按一次校准脉冲键,显示数字递增1,达到最大数字后回0,达到需要的数字时进行下一位调整;下一位调整仍然先按校准移位键,再进行类似调整。

各位校准脉冲是通过数据分配器产生控制脉冲。图4所示的双路2-4译码/数据分配器采用74156。第一路输出用来控制调整的数字闪动控制信号,第二路是用来校准脉冲分配。图4中Y0,Y1,Y2和Y3是用来控制调整显示数字位闪动,P0,P1,P2和P3是作为显示四位数字状态校准脉冲。

图4 校准位闪动和各位校准脉冲控制信号产生电路图

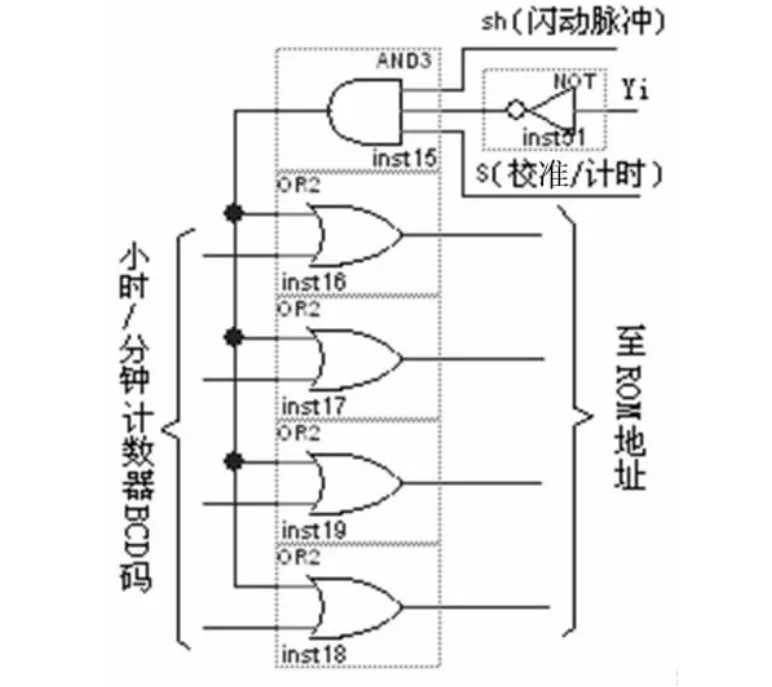

为了在进行调整某位能使数字闪动,可将小时和分钟计数器输出每位与s(校准/计时)、Yi(i=0,1,2,3)和sh(闪动脉冲)三信号与运算后相或。这样在调整某位时,显示数字状态有短时间全1,闪动脉冲频率为10Hz。在 ROM编码时数字状态为1111,列信号设定为111(所有点全暗)。电路如图5所示。

图5 调整位数字闪动电路图

2.5 校准/计时控制电路

每位校准由2-1数据选择器控制,校准/计时作控制端,状态为1时进行校准,以校准脉冲作计数器时钟信号;状态为0时进行计时,以下级进位脉冲作计数器时钟信号。

校准/计时为低电平时正常计时,Y0是低电平,校准/计时一旦变为高电平时校准脉冲分配至P0,小时十位数字以10Hz频率闪动,这时按校准脉冲键,这位数码递增,达到设定状态后按校准移位键,小时个位数字闪动,进行相应操作至设定状态,分钟十位、个位调整类似进行。

2.6 分频器和计数器电路

系统由2MHz晶体振荡器产生连续信号,本系统需要1/60Hz的分钟信号、1Hz的秒信号、10Hz的调整数字闪动信号sh、1kHz的序列信号产生器时钟信号,在QuartusII中做一个功能模块调用。

小时和分钟计数器用四个7490模块构成24进制计数器和60进制计数器,每个7490的时钟信号是用21MUX根据校准/计时状态选用校准脉冲还是低位进位脉冲。

3 结语

本设计是笔者多年从事“数字逻辑电路”和“可编程器件应用”课程教学多个课题中一个典型代表。其综合知识范围广,设计思想新颖,作为教学实验课题非常现实。本课题设计是采用原理图输入法完成,部分模块还可采用硬件描述语言法[4]完成。如果这样,就可大大地提高学生对知识的综合运用能力。

[1] 黄正瑾.CPLD系统技术设计入门与应用[M].北京:电子工业出版社,2002

[2] 李辉.PLD与数字系统设计[M].西安:西安电子科技大学出版社,2005

[3] 赵曙光.可编程逻辑器件原理、开发与应用[M].西安:西安电子科技大学出版社,2006

[4] 王今明.数字系统设计与Verilog HDL[M].北京:电子工业出版社2005