闪存高压电路的总剂量辐射效应研究

2014-08-07杨大为刘利芳谯凤英潘立阳

杨大为,刘利芳,谯凤英,陆 虹,潘立阳

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.清华大学微电子学研究所,北京110084)

·大规模集成电路设计、制造与应用·

闪存高压电路的总剂量辐射效应研究

杨大为1,刘利芳2,谯凤英2,陆 虹1,潘立阳2

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.清华大学微电子学研究所,北京110084)

研究了闪存电路系统中高压电路的总剂量辐射效应(TID)。通过对内部高压电荷泵电路和高压负载电路的TID辐射效应测试研究,表明辐照后高压通路相关的存储阵列及高压晶体管漏电将造成电荷泵电路的负载电流过载失效,最终导致闪存电路编程或擦除操作失效。

闪存;高压电路;电荷泵;总剂量辐射

1 背景介绍

随着空间技术的发展,越来越多的电子产品被应用到空间辐射环境中,如宇宙飞船、导航卫星等。在航空系统中需要使用电子器件实现对航空系统的控制,尤其需要通过非挥发闪存芯片实现程序和数据的存储。闪存芯片具有高密度以及非挥发的特点,被大量应用到航空系统中[1]。除空间应用外,闪存芯片还应用到其它的高剂量辐射环境中,如军事应用、高空飞机、医疗、高能物理、工艺和核电站等。然而随着器件尺寸的缩小,发生辐射寄生效应所需要的辐射剂量越小,因此需要研究非挥发存储器的辐射特性和加固设计方法。

闪存芯片包含存储阵列及各个电路模块,其中高压电荷泵和相关的外围高压电路主要用于产生和传输对存储阵列编程和擦除操作时所需要的不同高电压[2]。辐射对每个模块电路的影响不一样,而高压电路关系到整个存储器芯片的操作,是闪存系统中对辐射非常敏感的电路模块。相关研究表明,在20~60krad(Si)的辐照下闪存器件就会产生编程错误[3]。所以,探索电荷泵及其相关高压电路在辐照情况下的退化机制具有十分重要的研究价值和实际意义。然而,目前的相关研究都集中在完整商业存储芯片的抗辐照特性和单个高压晶体管的抗辐照特性方面,并没有对辐照后高压产生和管理电路对整个系统的影响单独进行分析[4-5]。

论文研究了NOR闪存系统中高压电荷泵及其相关管理电路的抗总剂量辐射特性。通过检测在不同辐照剂量下该电荷泵的输出和相关管理电路的退化特性,分析了导致高压操作失效的主要机制。

2 测试器件及实验设计

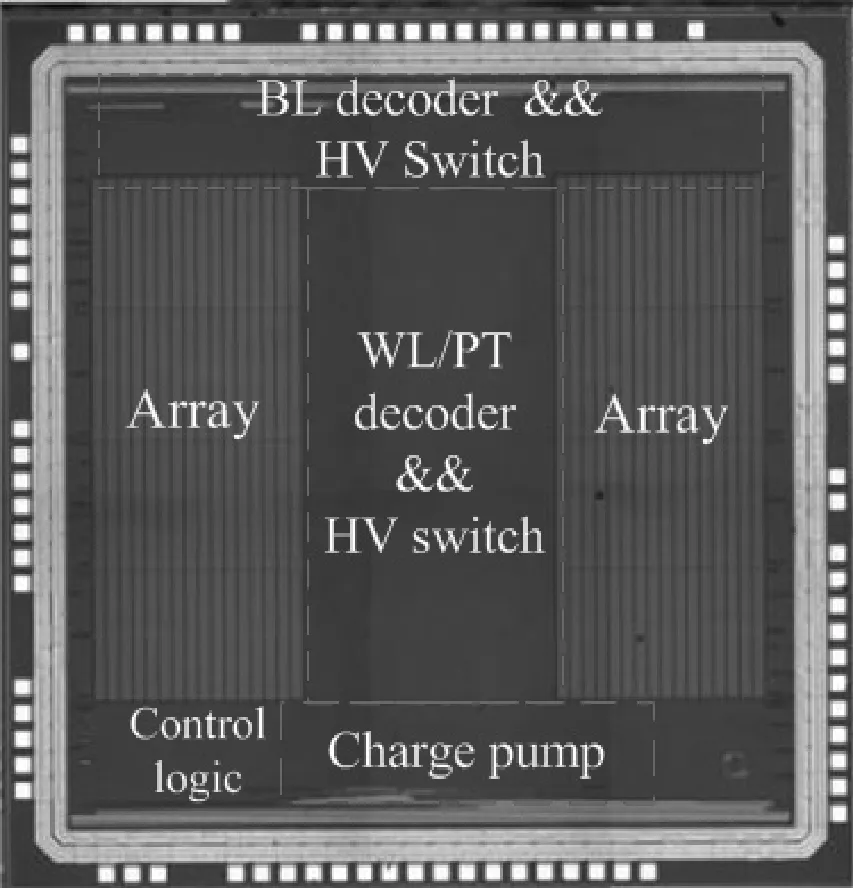

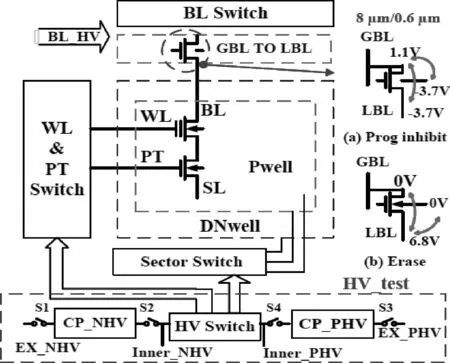

采用基于130nm工艺制造的NOR闪存芯片(如图1[6]),对该芯片内部与存储单元高压操作相关的两个-3.7V和+6.8V电荷泵进行了辐照实验。电荷泵电路结构如图2所示,包括Dickson电荷泵(即电容二极管结构[2]),电压驱动(Clk)和带有1V基准的输出采样电路(regulator)。

图1 NOR闪存芯片照片

图2 电荷泵结构示意

为了监测高压电路在辐射中的退化,芯片可以在两种工作模式下测试高压:①高压测试模式,即芯片仅启动电荷泵电路时测试电荷泵输出高压;②芯片写模式,即芯片进行编程擦除操作,测试电荷泵带负载工作情况下的内部高压。图3给出了芯片的高压切换结构示意。在操作模式1中,高压测试使能信号为1,开关S1/S3打开,S2/S4关闭,电荷泵电路开始工作,将产生的正高压和负高压输出到测试端口。在操作模式2中,芯片工作在写模式,开关S1/S3关闭,S2/S4打开,测试编程擦除操作的内部高压。在整个芯片接受辐照之前,整个芯片的功能和相关电荷泵的测试模式已经经过电学测试。

图3 芯片高压可测性设计结构示意

该芯片采用gamma射线辐射,辐射剂量率为50rad(Si)/s。在整个辐射过程中,芯片被偏置在读取模式,电荷泵电路处于关断状态。我们对芯片进行了不同总剂量的辐射,包括50,80,100,200krad(Si)。为避免退火效应的影响,辐照后的电学性能测试在半个小时以内进行。在本实验中,同时测试了几个芯片,不同芯片的性能基本一致。

3 结果与讨论

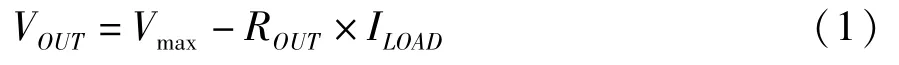

电荷泵电路的输出高压可以通过式(1)计算[7]:

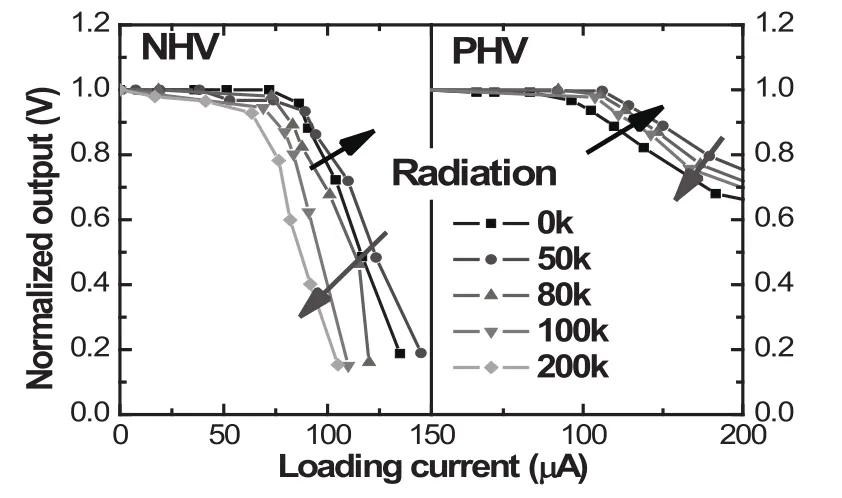

其中VOUT为电荷泵实际输出高压,Vmax为负载为0时电荷泵的输出电压,ROUT为电荷泵输出电阻,ILOAD为电荷泵负载电流。闪存芯片的电荷泵负载电流包括电荷泵本身晶体管的漏电流、高压电路以及存储阵列的漏电流等。如图4显示,在正负压电荷泵的输出电压分别为6.8V和-3.7V时,其辐照前的电流负载驱动能力约为80μA到100μA。当负载电流超过80μA时,随着负载电流的增加,输出电压开始降低。此处的负载电流包括S2/S4打开时存储阵列和高压晶体管的漏电。

图4 正负压电荷泵的驱动能力测试结果

当芯片进行辐照实验后,测试结果显示,当辐射剂量低于50krad(Si)时芯片可以正常编程擦除;辐射剂量到80krad(Si)时芯片能正常擦除、但无法编程;辐射剂量到100krad(Si)时芯片编程和擦除都已经失效。为了分析芯片的操作失效机制,测试了芯片写模式下的输出高压,测试结果如图5所示。编程操作时(红色曲线),芯片的负压随着TID的增加而下降:TID为80krad(Si)时负压下降到-2V以下,编程操作失效。但此时正高压没有出现退化,一直为6.8V。擦除操作时与之相反(蓝色曲线):芯片的负压没有退化,但正压出现了退化。TID为80krad(Si)时正高压下降到6V;TID为100krad(Si)时正压下降到4V,芯片擦除操作失效。

由图5可见编程时正高压没有退化,擦除时负高压没有退化。对比表1中存储单元操作时的端口偏置电压,分析可知未退化的高压均只加到存储单元的栅极(WL)上。与此同时,存储阵列位线(BL)上的结端口电压(源端、漏端以及Pwell)均出现退化。这表明辐射下的高压退化可能是由电路列方向的阵列或者高压传输管漏电流增加,超过了电路的负载能力所导致。

图5 芯片不同TID下编程与擦除模式的高压

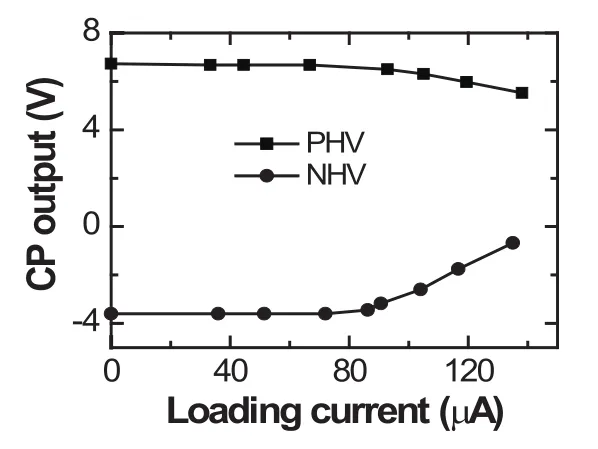

表1 存储单元操作关键端口电压

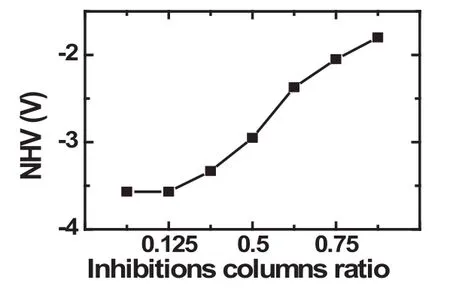

闪存电路列方向的主要可能漏电路径为存储阵列以及全局位线(GBL)的高压传输管,如图6所示。在闪存芯片中,每个Sector有2k列存储单元,同时也有2k个传输管。从图6(a-c)可以看到,选中区块内编程的列,在传输管的漏端有一个-3.7V的电压偏置,而擦除操作时有一个6.8V的电压加到该高压管的源端。同时编程禁止的存储单元所在的列,由于Pwell电位为-3.7V,BL电位为1.1V,也存在一个4.8V的结高压。TID辐射后,改变同一页编程禁止单元的比例(数据“0”的字节数),监测到负高压的退化特性不一样。如图7所示,随着编程禁止列数的增加,负压的退化更严重。因为改变编程禁止单元的数目即改变负压电荷泵驱动的负载,这表明高压的退化与列方向的存储管或者传输管在高压偏置(如编程禁止)下的漏电流相关。

图6 闪存芯片高压通道结构示意图

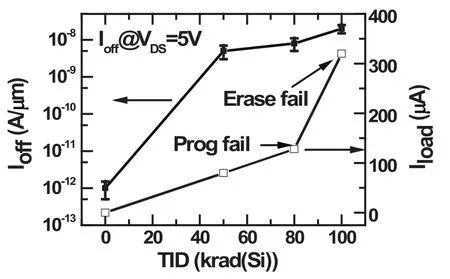

高压MOS受TID辐射的影响较低压MOS更为严重,其中一个显著退化效应是泄漏电流增加。图6中的高压传输管操作时施加高的漏结偏置电压,会导致更大的泄漏电流,即辐射导致漏端势垒降低效应(DIBL)[5,8]。如图8所示,在80krad(Si)辐照条件下,单个高压MOS在5V漏端偏置下的泄漏电流超过5nA;芯片中2k个晶体管的漏电流则达到了100μA。除此之外,存储阵列以及其它高压管的漏电流也会导致整体负载电流的增加,使得负载电流超过100μA,最终使电荷泵负载过载。因此,高压传输晶体管与存储阵列漏电流的增加,超过电荷泵的电流负载驱动能力,是辐射下闪存芯片操作功能失效的主要原因。

图7 TID辐射一页中不同编程禁止列比例负高压的退化

图8 高压管在5V偏置条件下TID诱生漏电

另外,我们还测试了正负高压电荷泵在辐照后的电流负载能力,如图9所示。50krad(Si)后,两个电荷泵的电路负载能力出现轻微上升,可能是由于NMOS晶体管的VTH降低所导致。随着TID的升高,电荷泵的驱动能力首先出现轻微上升然后开始下降。这是因为在辐射初期NMOS晶体管的VTH下降占主导因素,随着TID的增加,高压晶体管本身的漏电流增加占主导,使得负载驱动能力轻微下降。单独的电荷泵电路在100krad(Si)之后仍能正常工作:负压的驱动能力约为60μA,正压的驱动能力约为100μA,且空载时的电压值均没有发生退化。因此,电荷泵电路本身在辐射下的退化可以忽略。这表明辐射下操作失效不是由电荷泵的驱动能力下降导致的。

综上所述,闪存芯片在TID辐射下操作失效不是电荷泵本身的退化导致的。结合辐射前后电荷泵驱动能力的变化、编程擦除操作高压的退化及高压晶体管的辐射退化特性,表明TID辐射后芯片列方向的漏电流增加,包括高压传输管和存储阵列的漏电流增加,是写操作失效的根本原因。

图9 正负电荷泵辐射下的负载能力

4 结束语

详细讨论了闪存中高压电路的总剂量辐照退化特性。研究发现单独的电荷泵电路可以承受大于100krad(Si)的总辐照剂量。但是,一定量的辐照会导致高压通道上列方向晶体管漏电增大,从而增加电荷泵电路的电流负载,最终引起编程和擦除操作失效。相关研究可为后续的抗加电路设计提供借鉴。

[1]Gasperin A.Advanced Non-Volatile Memories:Reliability and ionizing radiation Effects[PhD thesis][C].Universitàdegli Studi di Padova,Italy,2008:19.

[2]G Compardo,M Scotti,SScommegna,SPollara,A Silvagni.An overview of flash architectural developments[J].in Proc.IEEE,2003(91):523-536.

[3]M Bagatin,G Cellere,S Gerardin,A Paccagnella,A Visconti,S Beltrami.TID sensitivity of NAND flash memory building blocks[J].IEEE Trans.Nucl.Sci.,2009(56):1909-1913.

[4]S Gerardin,M Bagatin,A Paccagnella,K Grürmann,F Gliem,T R Oldham,F Irom,D N Nguyen.Radiation effects in flash memories[J].IEEE Trans.Nucl.Sci.,2013(60):1953-1969.

[5]Z L Liu,Z Y Hu,Z H Zhang,H Shao,M Chen M,D W Bi,B Ning,RWang R,S Zou.Total ionizing dose effects in high voltage devices for flash memory[J].Nuclear Instruments and Methods in Physics Research Section B,2010(268):3498-3503.

[6]F Y Qiao,X Yu X,L Y Pan,H Z Ma,D Wu,JXu.TID characterization of 0.13μm SONOS cell in 4Mb NOR flash memory[C].in Proc.Int.Symp.Phys.Failure Anal.Integr.Circuits,2012:1-4.

[7]Z Y Hu,Z L Liu,H Shao,Z X Zhang,Z X,B X Ning,M Chen,D W Bi,S Zhou.Total ionizing dose effects in elementary devices for 180-nm flash technologies[J].Microelectron Reliab,2011(51):1295-1301.

[8]JR Schwank,M R Shaneyfelt,D M Fleetwood,JA Felix,PEDodd,SMember,PPaillet,V Ferlet-Cavrois.Radiation effects in MOS oxides[J].IEEE Trans.Nucl.Sci.,2008(55):1833-1853.

Investigation of Total Ionizing Dose(TID)Effect on High-Voltage Circuits in Flash Memory

YANG Da-wei1,LIU Li-fang2,QIAO Feng-ying2,LU Hong1,PAN Li-yang2

(1.The47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China;2.Institute of Microelectronics,Tsinghua University,Beijing 1100084,China)

The TID radiation degradation of high-voltage circuits in the flashmemory circuit system is studied.We evaluates the effect of TID radiation to the internal high-voltage charge pumpings and their periphery circuits.The results show that the functional failures of charge pumping circuits are induced by the increasing leakage ofmemory array and high-voltage transistors after radiation,and leads to operation failure from the programming.

Flash memory;High-voltage circuits;Charge pumping;Total Ionizing Dose(TID)

10.3969/j.issn.1002-2279.2014.06.002

TN47

:A

:1002-2279(2014)06-0004-04

杨大为(1977-),辽宁沈阳人,硕士,高级工程师,主研方向:集成电路设计。

2014-10-08