采用SRIO协议实现多DSP实时系统图像数据传输

2014-08-04宁赛男朱明孙宏海张叶

宁赛男,朱明,孙宏海,张叶

1.中国科学院航空光学成像与测量重点实验室,长春 130033

2.中国科学院大学,北京 100039

3.中国科学院长春光学精密机械与物理研究所图像室,长春 130033

采用SRIO协议实现多DSP实时系统图像数据传输

宁赛男1,2,3,朱明3,孙宏海3,张叶3

1.中国科学院航空光学成像与测量重点实验室,长春 130033

2.中国科学院大学,北京 100039

3.中国科学院长春光学精密机械与物理研究所图像室,长春 130033

1 引言

实时图像处理技术在目标跟踪、机器视觉等领域得到越来越多的应用。高分辨率高速图像实时处理系统,具有数据量大、算法复杂度高等特点,设计实时处理系统时对图像数据的采集能力、处理能力、外部缓存性能容量以及系统内数据传输能力等提出了非常高的要求[1-3]。如何完成海量数据的实时传输和处理是实时图像处理系统设计的难点。随着高性能DSP以及FPGA等处理器的发展,采用多个处理器并行处理是提高系统处理能力的有效途径,因此系统中大量数据高速实时传输成为一个关键技术[4-7]。

传统的并行总线以增加总线的位宽和总线频率来提高传输速度,这样就造成了总线连线过多系统布局布线困难、时钟与数据信号的信号完整性要求较高、对多处理器互联困难等问题。传统并行总线越来越难以适应嵌入式系统的发展,基于差分、源同步、时钟数据恢复等先进技术的串行互连方式是总线发展的必然趋势。SRIO作为一种开放式的嵌入式系统互连技术,已广泛受到业界认同[8]。本文提出了基于FPGA+4DSP架构的高速实时图像处理系统设计,采用SRIO互连技术实现DSP间、DSP与FPGA间的高速数据传输。

2 RapidIO协议简介

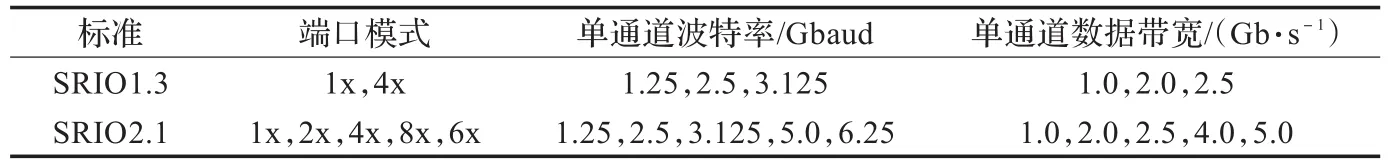

2.1 RapidIO协议概述准研制。2.1标准具有比1.3标准更多的端口模式选择和更高的波特率[11-12],表1是两个标准间的比较。SRIO利用8b/10b编码策略将时钟信号嵌入到数据信号中,所以实际的数据带宽是传输速度的0.8倍。而随着SRIO发展,2012年SRIO提出了频率更高的第三代标准,在新的标准中,单通道数据带宽可以达到10 Gb/s。SRIO将多个端口配置多通道模式(如2x、4x),从而得到比1x模式更快的速度。SRIO支持全双工传输,单通道由两组差分信号4根信号线组成,分别用于数据的发送和接收,二者互不影响。

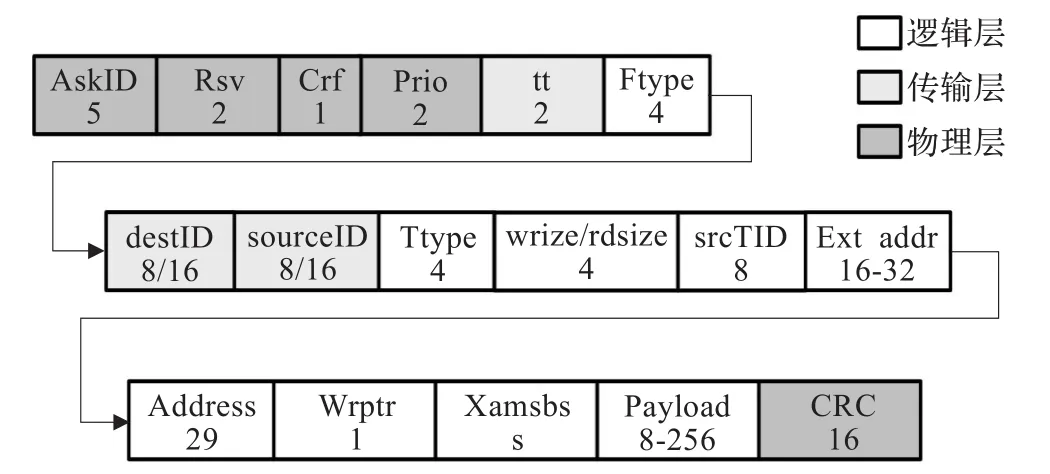

图1 常见包格式

RapidIO最初是由Freescale和Mercury共同研发的,采用包含源同步时钟的差分串行总线,具有带宽高、延迟低、引脚少、易扩展等优点。RapidIO的提出解决了传统总线技术造成的嵌入式系统设计的瓶颈,解放了传统总线对时钟和处理器数目的限制。经过十多年的发展,RapidIO相继推出了三代协议标准,获得了几乎所有的嵌入式系统芯片及设备供应商的认可和支持,并已经广泛地应用于电信、通讯以及嵌入式系统内的芯片与芯片之间、板与板之间的互连。

RapidIO协议采用三层分级体系结构,分别为逻辑层:定义了端口的全部协议、包的格式;传输层:定义了RapidIO地址空间和在端点器件间传输包所需要的路由信息;物理层:描述了器件级端口信息,如包传输机制、流量控制、电气特性和低级错误管理等[9-10]。

根据物理层的端口配置可以将RapidIO分为两类技术:并行RapidIO和串行RapidIO(Serial RapidIO,SRIO)。随着技术的发展,并行RapidIO已逐渐被串行RapidIO所取代。SRIO作为一种开放式协议标准,被广泛应用于系统内芯片间互连以及背板间的互连。

目前,SRIO实现多是基于RapidIO1.3标准和2.1标

2.2 SRIO数据包

SRIO数据传输由包和控制符合组成,包是系统中短端点器件间的通行单元,提供终端节点设备间进行逻辑事务处理的端口;控制符号用于管理RapidIO物理层互连的事务流,也用于包确认、流量控制和维护等功能。图1是常见的包的格式。

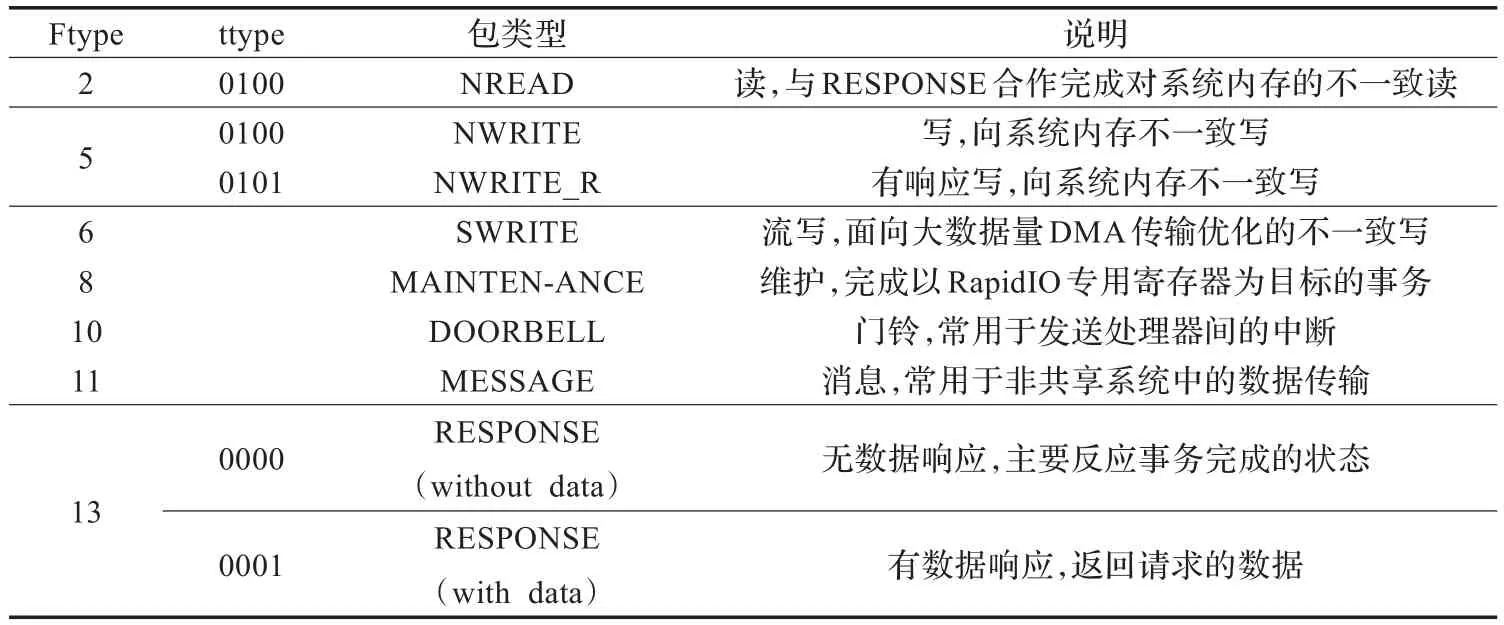

destID和sourceID用来区分系统中的器件prio是包的优先级,address、wrptr和xamsbs共同构成了访问所需的地址信息,ext_addr是地址的扩展段,使系统能够访问更大的地址空间,CRC是包的校验段,Payload为有效数据载荷,最多为256字节,SRIO包开销少,数据有效率可以到达92%~94%。Ftype指示包的格式类型,Ttype字段表明事务的具体类型,两者共同决定了包的类型,表2是对SRIO常用的包及操作的说明。SRIO操作是由请求和响应事务组成的,事务则是由包组成的,常见的操作有:读操作、写操作、维护、消息、门铃等。SRIO系统传送事务的过程为:发起者产生一个传输请求,请求包传输到目标方,目标方根据请求完成响应的操作后,发送相应的响应包传回到发起方。发起者和目标方可以是点对点的直接互连也可以使用一个交换结构进行互连,使用交换结构可以使系统中容纳更多的端点器件,而不受其SRIO接口数量的影响。

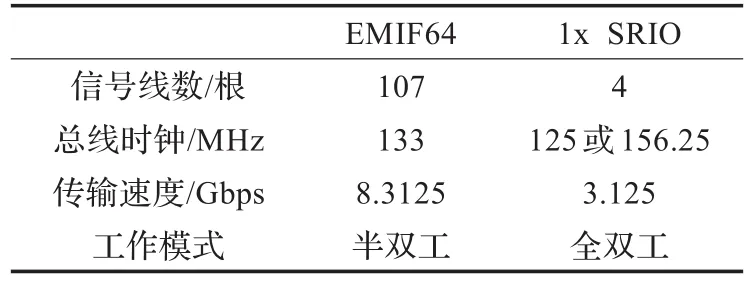

表1 SRIO 1.3标准和2.1标准比较

表2 常见包的类型

3 系统介绍

3.1 系统组成

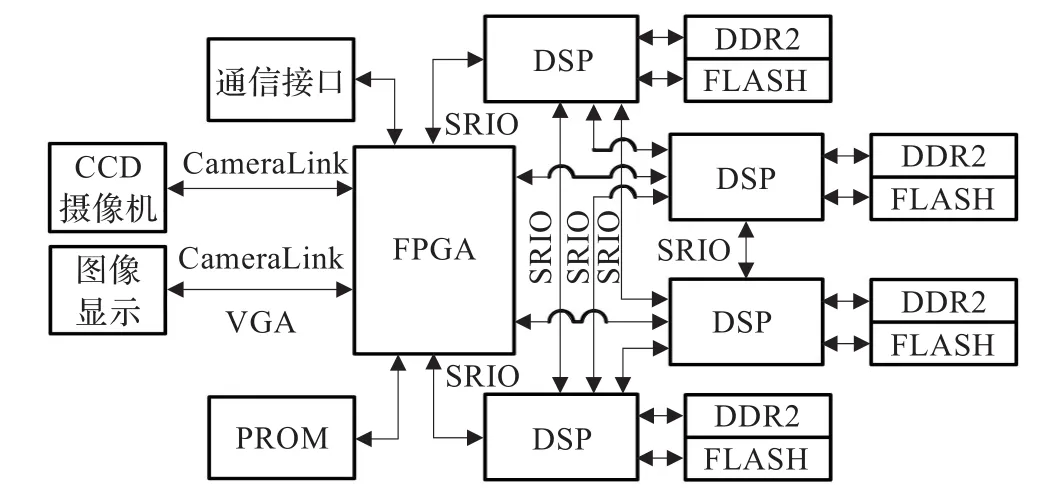

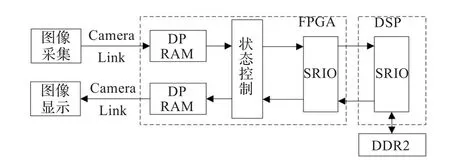

本系统设计的目标是能够完成1k×1k@100 f/s 12 bit灰度图像采集、传输,并要求系统能够运行复杂图像处理算法。这样高的要求就必须在系统设计时对系统的处理性能、缓存容量、传输带宽等全面分析考虑。单个处理器的处理性能有限,采用多处理器并行处理是数字处理系统发展趋势。本文为此设计了基于FPGA+多DSP的通用图像处理系统,使用4片高性能定点DSP TMS320C6455(简称C6455)和一块XC5VSX50T FPGA(简称v5),图2是系统的结构图。四片DSP协同处理对16位数据的处理能力为38400M MAC/s,可以满足大部分算法的计算要求,并且每个DSP都外接有1片DDR2 SDRAM,用来缓存图像数据。

图2 系统框图

图像采集由高性能的CCD摄像机完成,然后经过Camera Link接口输入到系统中。Camera Link信号分为串行通信信号、相机控制信号、视频信号三部分,使用LVDS信号格式传输,需要专用芯片将其进行转换,转换后输出28位数据和1路时钟信号。由于C6455中没有专用的视频输入输出接口,Camera Link输入的图像数据需要经过格式转换和传输控制,将其转换成C6455可接受的信号后输入到DSP。这一过程则由FPGA完成,此外FPGA还可以对图像进行预处理、实现外部设备的通信以及对图像显示时的控制。

在解决了系统的计算能力和大容量图像数据的缓存问题后,如何实现DSP之间、DSP与FPGA之间的高速数据传输成为了一个关键问题。传统的解决方案是通过EMIF进行连接,但并不适合多处理器系统,这是由于实现EMIF需要数据总线、地址总线、时钟、读写使能、片选等控制信号,过多的信号线将造成布局布线上的困难,不利于系统实现。以本系统为例,实现一片DSP和FPGA间EMIF互连就至少需要107根信号线(包括64位数据总线、25根地址总线、8根字节使能信号、4根片选信号以及其他控制信号新),实现4片DSP间以及DSP和FPGA间互连就需要更多信号线,这是对系统布局布线的一大挑战。系统摒弃传统的EMIF而采用了SRIO以直接的点对点互连方式实现DSP之间、DSP与FPGA之间的数据传输。表3是单通道模式下SRIO与64位数据位宽的EMIF的比较,与EMIF相比SRIO的信号线数量少(仅需要4根)并且采用全双工工作模式传输的效率更高。

表3 单通道SRIO与64位EMIF比较

3.2 C6455 中SRIO实现

C6455是一款处理能力很高的新型高性能定点DSP,最高主频可达到1.2 GHz,16位定点处理能力为9 600 M·MAC/s。C6455不仅是内核的增强和运算速度的提升,相比于之前的芯片,集成了丰富的外设,如PCI总线端口、千兆以太网端口、64 bit无缝外部存储器端口、DDR2 SDRAM端口等,最重要的是增加了对SRIO支持的模块。

3.2.1 SRIO模块简介

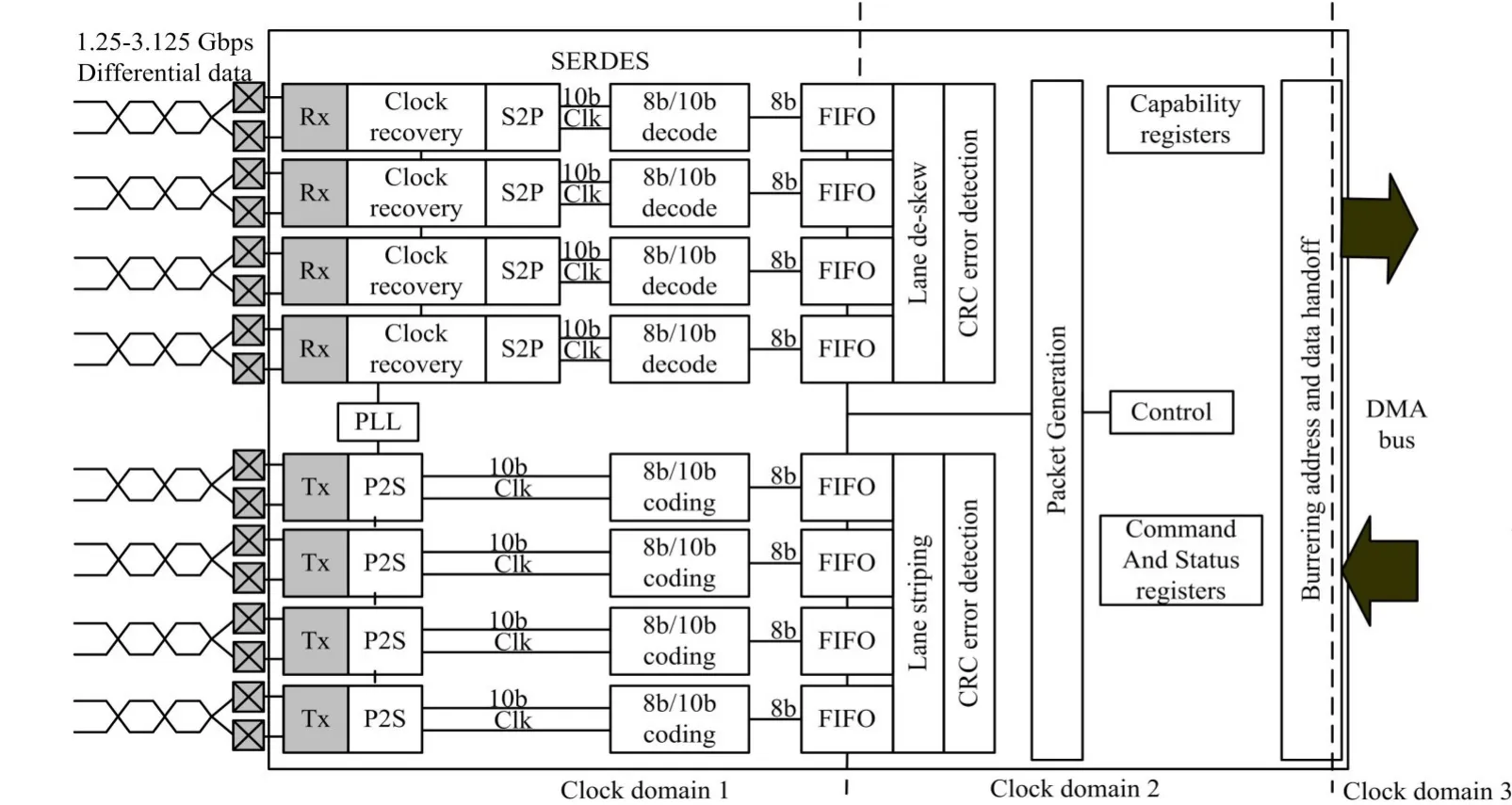

C6455内嵌了SRIO模块,支持SRIO1.3标准,向下兼容1.2标准,拥有4个全双工SRIO端口,支持1x/4x工作模式。SRIO数据传输与DMA传输结合,当SRIO工作时,DMA以自动方式启动,SRIO可以通过DMA方式直接对L2存储器进行读写,而不需要向CPU产生中断。这样就减少了中断的数目,也减少了延时。图3中(a)是C6455中SRIO的功能模块的结构图。SRIO模块主要由差分接收器(Rx)、差分发送器、8b/10b编解码器、串行器、解串器、8位FIFO、通道对齐模块、CRC校验模块等组成[13]。

3.2.2 SRIO操作实现

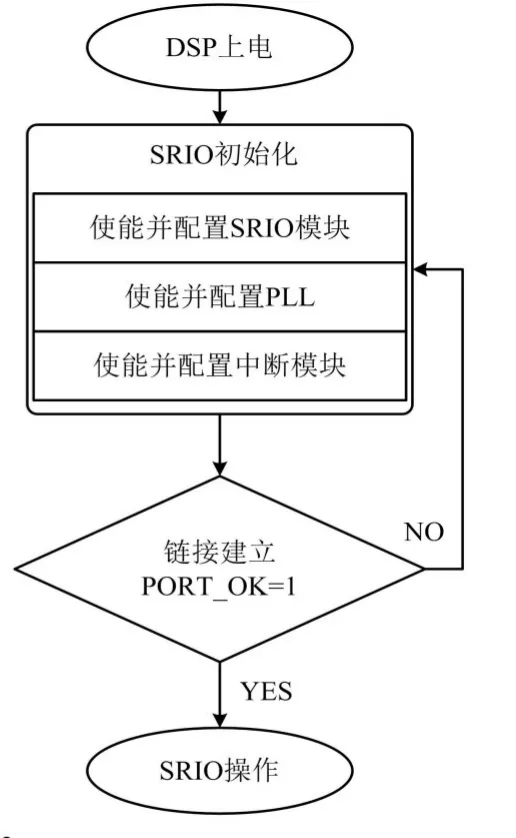

在RapidIO简介中,SRIO操作是通过包的传输完成的。C6455中SRIO支持两种数据传输机制:DirectIO和Message,这两种传输机制可以通过配置相应的控制寄存器实现。DirectIO是较为常用的传输方式,在DirectIO传输中,源器件对目标器件的地址空间是可见的,可以支持事务操作包括:NREAD、NWRITE、NWRITE_R、SWRITE、ATOMIC、MAINTENANCE、DOORBELL。与之传输相关的寄存器有7个,为LSU_Reg0~LSU_Reg6。其中LSU_Reg0~LSU_Reg5六个寄存器的状态直接与SRIO包中数据段关联,LSU_Reg6用来判断事务是否完成,当一个事务完成时,LSU_Reg6最低位为0。在进行SRIO操作之前,用户必须对SRIO进行初始化,SRIO的初始化要完成相关模块使能和配置,如SRIO模块使能、PLL模块使能、端口模式和速度设置、相关中断的使能和设置等。图3中(b)是C6455 SRIO初始化的流程图。SRIO初始化可以通过设置相关寄存器完成,当初始化完成并且SRIO链路建立时,端口错位和状态寄存器SPn_ERR_STATE中的PORT_OK字段有效[14]。链路建立后,用户就可以根据需要实现各类SRIO操作。

3.3 基于FPGA的SRIO实现

系统中使用到了Xilinx生产的Virtex-5系列FPGA,该系列FPGA具有更低的功耗、更快的速度、更丰富的逻辑单元和片内存储、更灵活的时钟管理通道等优点。Virtex-5内嵌了24个低功耗的的收发器,可以实现100 Mb/s~3.75 Gb/s高速串行接口,为SRIO的实现提供了硬件支持。

Xilinx提出的SRIO解决方案是基于RocketIO实现的,RocketIO是Xilinx FPGA内嵌的可编程高速串行收发器,是SRIO实现高速传输的关键,在Virtex5中称为GTP或GTX。RocketIO包括PMA(Physical Media Attachment,物理媒介适配层)和PCS(Physical Coding Sublayer,物理编码子层)[15]。PMA中集成了SERDES、发送接收缓冲、时钟发生器和时钟恢复电路,主要用于串行化和解串。PSC子层负责8b/10b编解码和CRC校验,并集成了负责通道绑定和时钟修正的弹性缓冲。图4中(a)是RocketIO的结构图。

Xilinx SRIO解决方案以RapidIO2.1标准为依据,向下兼容1.3标准,可支持1x/4x工作模式,单通道最高频率可达到3.125 Gb/s。结构如图4(b)所示,它由物理层核(Serial RapidIO Physical Layer Core,PHY)、逻辑传输层核(RapidIO Logical(I/O)and Transport Layer Core,LOGIO)、缓冲器核(Serial RapidIO Buffer Core,Buffer)和参考设计4个部分组成。物理层核负责实现物理层功能包括包的控制符传送、流量控制、错误管理等;逻辑传输层核用于实现逻辑层和传输层功能包括事务组包、拆包等;缓冲器核缓冲数据,以便更有效地实现核的功能;参考设计包括时钟控制(Clocks)、复位设计(Resets)和配置空间的存取(Register Manager),参考设计控制了整个核的工作和属性设置。这些设计实现了SRIO协议内容,而具体的数据的收发则是由RocketIO硬件结构完成。

图3 (a)SRIO模块结构图

图3 (b)SRIO初始化流程图

图4 (b)SRIO IP结构图

Xilinx SRIO解决方案中,直接与用户相关的是逻辑传输层接口。用户接口包含4类端口:发起请求端口(Initiator Request Port),发起响应端口(Initiator Response Port),目标请求端口(Target Request Port),目标响应接口(Target Response Port),这些端口上的信号直接与各种SRIO操作相关,通过对这些端口进行合理的配置就可以实现数据的传输。

4 基于SRIO的图像高速传输实现

4.1 实现原理

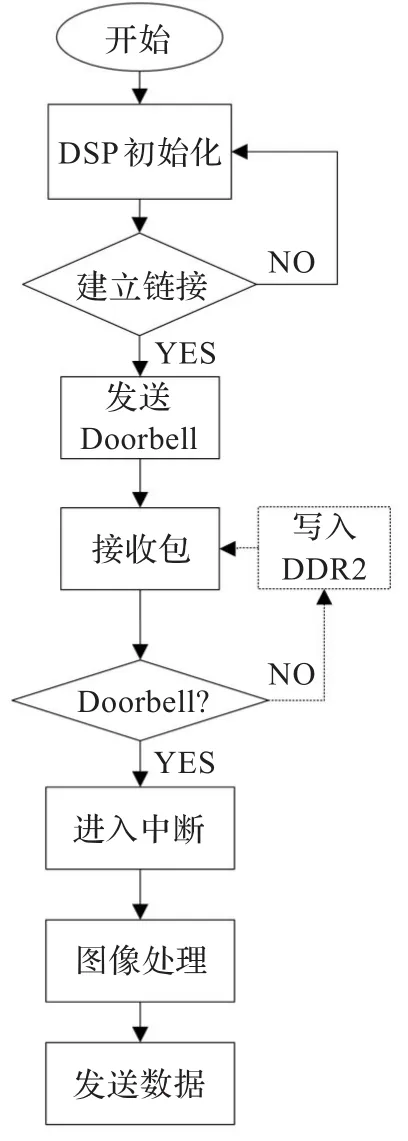

本文主要设计了FPGA和DSP中间的SRIO传输实验来验证SRIO功能。图5(a)是实验的原理图。SRIO主要支持两种数据传输的机制:一是直接存储器访问,可以通过读写操作完成;另一种是消息,可以使用消息操作实现。由于读写操作易实现,本系统中主要使用写操作(NWRITE)进行数据传输,并且使用门铃操作完成系统内包括中断控制等在内的控制工作。

图5中(b)和(c)分别是DSP和FPGA数据交换的具体流程。首先DSP向FPGA发送一个DOORBELL,FPGA接收到DOORBELL后开始进行图像采集,然后再将图像数据通过NWRITE操作发送给DSP。在图像采集时,为了避免采集过快而造成的图像丢失情况,使用两个双口RAM(DPRAM)以乒乓操作的方式对图像数据进行缓存和输出。FPGA每发送完一帧图像,就向DSP发送一个DOORBELL,从而使DSP进入中断。在中断服务程序中,可以对图像进行处理,也可以根据需要将图像通过SRIO发送给其他的DSP或者FPGA。FPGA接受到处理后的图像与外部通信,实现显示、存储等功能。在前面的介绍中可知,DSP的SRIO操作是直接与DMA相关的,所以当FPGA向DSP发送图像时,可以直接将发送的目标地址映射为DSP中DDR2 SDRAM的地址区域,DSP在接收到NWRITE包时会以DMA的方式自动将图像存入DDR2 SDRAM的相应区域,无需经过CPU处理。所以,DSP在初始化时不仅仅需要对SRIO进行初始化,还要对DDR2 SDRAM进行配置。

图5 (a)实验原理图

图5 (c)DSP流程图

图5 (b)FPGA流程图

图6 系统实验平台

4.2 实验结果和分析

本次实验中CCD相机采集的图像为分辨率为1 280× 1 024的8位灰度图像,帧频为74帧/s,时钟为50 MHz;SRIO设置为单通道模式、传输速度为3.125 Gb/s。FPGA和DSP按照图5中的流程工作,用ChipScope抓取FPGA内部部分信号,结果如图7所示。

图7 (a)两块DPRAM上的波形

图7 (b)发送图像波形

图7 (c)接收图像波形

图(a)反映了图像数据在两个DPRAM中缓存的过程,ChipScope采样频率为50 MHz,clka是写时钟为25 MHz,clkb是读时钟为39.062 5 MHz。由于相机像素宽度为8位而SRIO的数据对齐方式为64位,为了方便数据的传输,将DPRAM设置为32位输入64位输出模式。每个DPRAM缓冲一行图像即1 280B,使用两块DPRAM以兵乓操作的形式对图像采集和传输进行控制,wr_en_0和wr_en_1分别控制两块DPRAM的写使能。从图中可以看出SRIO传输一行数据所需的时间要小于每行图像采样的时间,这就保证了图像在采集不丢失,也为图像的传输和处理提供了操作时间。

图(b)是在FPGA发送图像时抓取SRIO IP发起请求端口的信号图,ChipScope采样频率为39.062 5 MHz。FPGA使用NWRITE操作发送数据(ftype=5,ttypt=4),ireq_data为发送的64 bit宽的数据,ireq_sof_n低有效,标记了每个包的开始,ireq_eof_n低有效,标记了每个包的结束。在图中所示的时间内FPGA共发送了6行图像,即6.25 KB数据,总的处理时间约为22 μs,图像传输的实际带宽约为284 MB/s。

图(c)是FPGA接收图像时抓取的图像,ChipScope采样频率为39.062 5 MHz。DSP通过向FPGA发送NWRITE包发送数据,treq_data为接收到的64 bit位宽的数据,NWRITE最大的有效数据载荷为256B,发送一行图像数据需要5个NWRITE包,由于FPGA内用作图像缓存的RAM很少,因此DSP每发送一行图像数据时发送一个DOORBELL,为了将该DOORBELL与之前DSP发送给FPGA的采样控制DOORBELL区分开,可以给DOORBELL的信息字段赋予不同的值。

5 结束语

本文结合实际工程中对图像处理的高速实时要求,设计了基于FPGA+4DSP的硬件处理系统平台,4片高性能DSP C6455的使用能够满足系统对处理速度的要求。系统设计时,考虑到传统的通过EMIF实现处理器间连接会造成制版时布局布线困难,使用了SRIO互连技术实现处理器件图像实时传输。SRIO具有引脚少、开销低、速度快的特点,并且C6455和v5都对SRIO有很好的支持。实验证明系统中SRIO能够快速稳定地传输数据,可以满足1k×1k@100 f/s 12 bit灰度图像采集实时传输的要求。

[1]孙科林,周维超,吴钦章.高速实时光纤图像传输系统的实现[J].光学精密工程,2011,19(9):2228-2235.

[2]冉峰,杨辉,黄舒平.面阵CCD彩色视频图像实时采集系统的设计[J].光学精密工程,2010,18(1):273-280.

[3]孙春凤,袁峰,丁振良.基于FPGA的多通道高速CMOS图像采集系统[J].计算机工程与应用,2008,44(21):46-48.

[4]须文波,陈玉萍,孙俊.基于DSP的图像压缩系统设计与算法研究[J].计算机工程与应用,2007,43(24):88-90.

[5]苏宛新,程灵燕,程飞燕.基于DSP+FPGA的实时视频信处理系统设计[J].液晶与显示,2010,25(1):145-148.

[6]吕耀文,王建立,曹景太,等.移动便携存储系统的设计[J].液晶与显示,2012,27(5):697-702.

[7]王晓东,刘文耀,金月寒,等.基于DSP和CPLD的激光雷达图像采集和显示集成系统[J].光学精密工程,2004,12(2):190-194.

[8]马春江,牛文生,孙靖国.几种串行总线互连技术分析[J].航空计算技术,2007,37(5):127-130.

[9]Sam Fuller.RapidIO:The embedded system interconnect[M]. [S.l.]:John Wiley&Sons,Inc,2005.

[10]梁基,金亨科,徐炜民,等.基于RapidIO的高性能接口的设计与实现[J].计算机应用与软件,2009,26(7):43-45.

[11]RapidIO Trade Association.RapidIO Specification 1.3[EB/OL]. [2005-06].http://www.rapidio.org/specs/current.

[12]RapidIO Trade Association.RapidIO Specification 2.1[EB/OL]. [2009-08].http://www.rapidio.org/specs/current.

[13]黄克武,吴海洲.基于TMS320C6455的高速SRIO接口设计[J].电子测量技术,2008,31(9):143-146.

[14]黄先春,黄登山,骆艳卜.RapidIO链的设计方案与应用[J].计算机工程与应用,2009,45(32):63-64.

[15]何玉红,赵琨.基于FPGA的RapidIO总线接口设计与实现技术[J].计算机与网络,2012,38(13):57-59.

NING Sainan1,2,3,ZHU Ming3,SUN Honghai3,ZHANG Ye3

1.Key Laboratory of Airborne Optical Imaging and Measurement,Chinese Academy of Sciences,Changchun 130033,China

2.Graduate University of Chinese Academy of Sciences,Beijing 100039,China

3.Image Lab,Changchun Institute of Optics,Fine Mechanics and Physics,Academy of Sciences,Changchun 130033,China

The high-speed real-time usually has a huge number of data with intricate algorithms;therefore it is difficult to transmit the image data real-timely in the real-system.It is that acquisition speed and transmission speed and memory capability must be considered.In the traditional method,the image data is usually capture and transport through parallel interfaces,which possess lager areas and pins in the resource limited embedded system.A new platform of image processing system is advanced based on the Serial RapidIO(SRIO)interface with one Xilinx’s FPGA chip XC5VSX50T and four TI’s DSP chip TMS320C6455.The system can real-timely transmit the image data at a high very speed of 3.125 MB/s. Since its stability,portability and feasibility has been tested,the system can service as a reference model for such a real-time image processing system designs.

image processing;multi-DSP;Field Programmable Gate Array(FPGA);Serial RapidIO(SRIO)

针对高速实时图像处理系统数据量大、算法复杂度高等特点,从系统的处理性能、缓存容量、传输带宽三个要点考虑,设计了一种基于FPGA+4DSP架构的实时图像并行处理系统,使用SRIO互连技术取代传统EMIF方式实现DSP间、DSP与FPGA中间的数据传输。实验结果表明,系统传输带宽峰值为312.5 MB/s,这种新的嵌入式实时图像处理平台能够实时采集传输处理1k∗1k@100 f/s高分辨率图像数据,并且具有可靠性高、通用性强、灵活性好的优点。

图像处理;多数字信号处理器;现场可编程门阵列;串行高速输入输出

A

TP752;TN911.73

10.3778/j.issn.1002-8331.1301-0146

NING Sainan,ZHU Ming,SUN Honghai,et al.Implementation of image data transmission in multi-DSP real-time system based on SRIO.Computer Engineering and Applications,2014,50(22):73-78.

国家自然科学基金青年基金(No.60902067);吉林省重大科技攻关项目(No.11ZDGG001)。

宁赛男(1990—),女,硕士研究生,研究领域为图像处理;朱明(1964—),男,博士研究生,研究员,研究领域为图像处理、光电成像测量技术、电视跟踪;孙宏海(1980—),男,博士研究生,助理研究员,研究领域为高帧频数字相机和实时数字图像处理;张叶(1981—),女,博士研究生,助理研究员,研究领域为图像处理。E-mail:nsn@mail.ustc.edu.cn

2013-01-14

2013-04-02

1002-8331(2014)22-0073-06

CNKI网络优先出版:2013-04-09,http://www.cnki.net/kcms/detail/11.2127.TP.20130409.1522.004.html