双极型步进电机的斩波驱动电路设计

2014-07-25韩俊奇徐建华张明星王良坤

韩俊奇,徐建华,张明星,王良坤

(1.中国科学院大学,北京 100049;2.中国科学院微电子研究所,北京 100029;3.杭州中科微电子有限公司,浙江 杭州 310053)

0 引言

步进电机作为控制执行元件,它的无累积误差[1]等特点使其在数字控制系统、工业控制等领域得到了广泛应用,它的性能主要取决于驱动器的设计。驱动器中多采用斩波驱动技术以提高步进电机输出转矩和电源利用效率,其电路设计的好坏决定着角度细分中微步步距角的精度。在传统的斩波驱动器设计中,电路结构复杂,精度不高。本文设计了一款基于0.35 μm BCD工艺实现的斩波驱动电路,精确度高、功耗低且可直接由数字控制实现角度细分。

1 斩波驱动系统设计

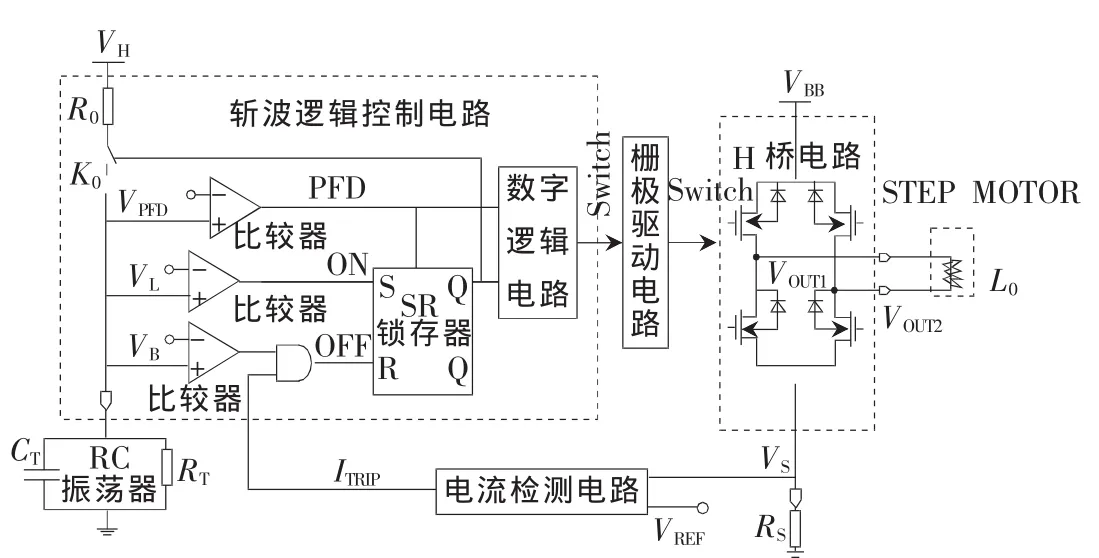

斩波驱动电路系统构架如图1所示,包括电流检测电路、斩波逻辑控制电路、功率放大电路,其中功率放大电路由栅极驱动级电路和H桥电路组成。当电流检测电路检测到电机线圈电流达到额定值后复位SR锁存器,使线圈电流进入衰减状态,开关K0打开,外接RC振荡器衰减到VL电压后置位SR锁存器,线圈电流重新进入充电状态。上述过程不断重复,使线圈电流在斩波意义上逼近恒定值。

图1 斩波横流驱动系统电路

对于斩波驱动电路来说,斩波电流精度和功耗是两个重要指标,斩波电流精度主要受电流检测电路精度影响,功耗主要由功率放大电路设计的好坏决定。因此电流检测电路和功率放大电路的设计是整个系统设计的关键。

2 电流检测电路设计

电流检测有多种实现方式[2],如图1所示,该结构采用串联电阻法,结构简单稳定、精度高且无带宽限制。由于电机相电流会达到安培量级,出于对功耗和功能的考虑,串联电阻RS阻值较小,采样电压VS限制在很小的范围内。

微步细分[3]的传统设计常采用DAC将量化的正弦波数据转化为模拟参考电压VREF,再通过比较器比较VREF与VS的相对大小,进而控制相电流形成按正余弦规律变化的阶梯波,由于采样电压Vs值很小,对比较器精度有很高要求。

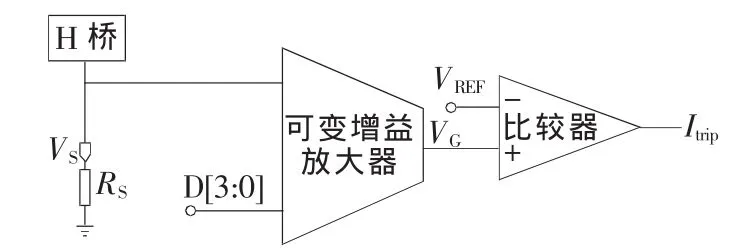

针对上述问题,本文提出了一种改进型的电流检测电路。如图2所示,将采样电压VS经非线性可变增益放大器放大,然后与固定的参考电压VREF比较,这样大大精简了电路结构,减小了电路输入失调对检测误差的影响。

图2 改进型检测电路

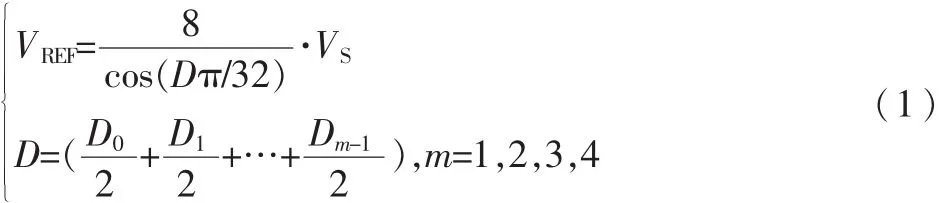

通过选取合适的可变增益放大器的增益,如式(1)所示,其中数字量D0,D1,…,Dm-1的二进制权重可通过数字信号D[3:0]控制相电流幅度形成按正余弦规律变化的阶梯波,进而实现最高1/16步进的角度细分。

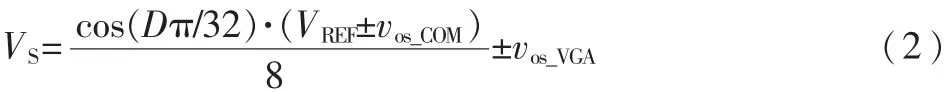

电路中各模块输入失调的影响如式(2)所示,其中vos_VGA和vos_COM分别表示可变增益放大器和比较器的输入失调电压,由此可知上述失调电压仅仅在相电流较小时对精度有影响,而此时D取较大二进制数,vos_COM对精度影响可忽略不计。

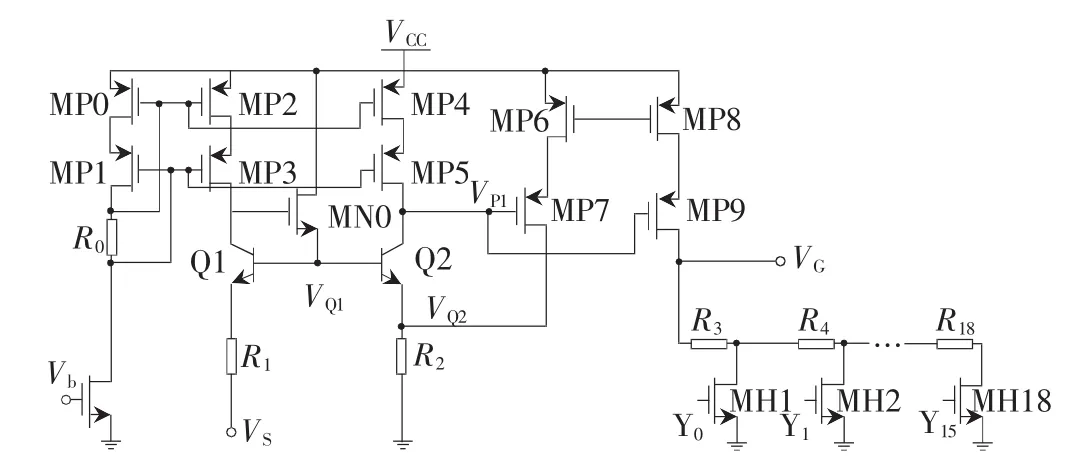

此结构中可变增益放大器的设计是重点,它要求能放大接近地电平的正电压小信号、精确度高并且输入失调电压小,本文通过改变输出电阻实现增益改变[4],具体电路如图3所示,图中省去了控制信号D[2:0]到Y0,Y1,…,Y7的译码电路。

图3中MP4、MP5、Q2、MP6、MP7、R2构成一个反馈系统;MP4、MP5、Q2构成前置放大器,Q2工作在放大区,VQ1与VQ2为输入信号;MP6、MP7、R2构成反馈网络。由于MP4、MP5构成共源共栅结构,VP1处输出电阻很高,可以认为工作过程中VQ1与VQ2差值恒定,那么流过MP7的电流变化量 ΔiMP7如式(3)所示,其中 ΔVQ1、ΔVQ2表示VQ1、VQ2的电压变化量。

图3 可变增益放大器

图3中MP2、MP3、Q1、R1构成升压电路,并与MP4、MP5、Q2、R2结构对称且对应器件参数相同,MN0为二极管Q1、Q2提供基极电流。同样地,有 ΔVQ1=ΔVS,并且当输入电压VS为零电平时,忽略输入失调电压,流过MP7的电流为零,满足了放大接近地电平正电压小信号的目的。此外MP2、MP3构成的电流镜结构,使得升压电路受电源VCC的波动影响很小,避免了传统检测电路中上拉电阻结构受电源电压波动影响的弊端。

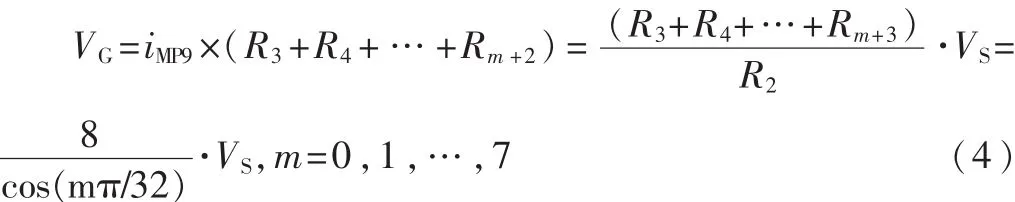

MP6、MP7与MP8、MP9构成共源共栅电流镜且对应器件参数相同,有iMP7=iMP8;输出电压VG与输入电压VS的关系如式(4)所示,其中R3,R4,…,Rm+3表示串联进MP8、MP9支路的电阻:

3 低功耗功率放大电路设计

本设计的功率放大电路中采用H桥结构,H桥桥臂上下管都采用N型电力MOSFET[5],并通过并联尽量多的电力MOSFET来获得较低的导通电阻。

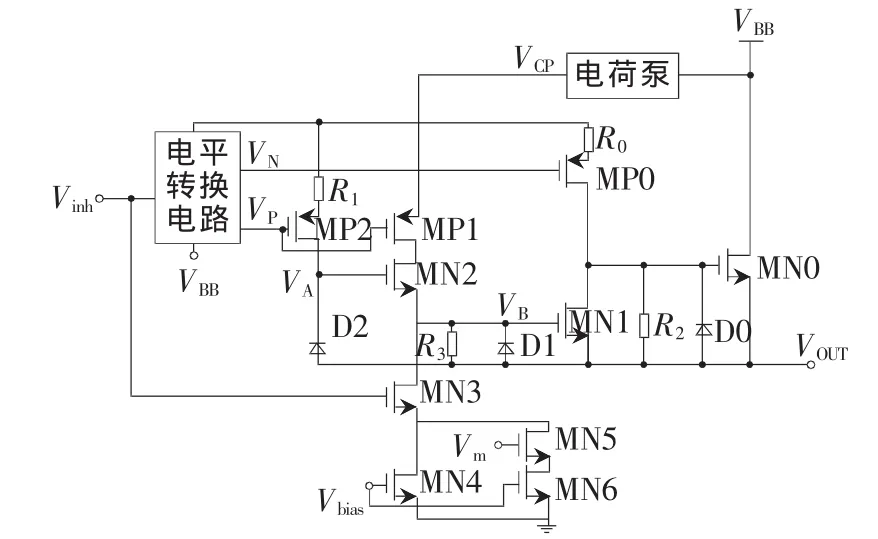

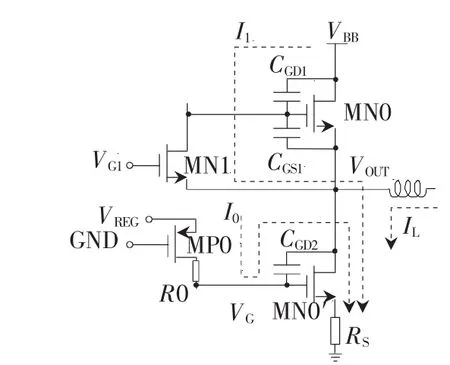

上管作为高压侧开关管,其栅极驱动电路如图4所示,其中MN0表示上管,为保证其较低的导通电阻,通过电荷泵得到高于负载电源电压VBB大约5 V的栅极驱动电压VCP[6]。

图4 上管栅极驱动电路

图4中,VP和VN是数字开关信号Vinh经电平转换电路产生的模拟开关信号,高低电平分别为VCP和VBB,VP与Vinh同相,VN与Vinh反相。

当Vinh为高电平MN3管打开,VOUT端通过D1、MN3、MN4形成对地的电流通路,VB拉低到VOUT电压以下,以保证MN1处于关闭状态;同时打开MP0管,从而对MN0管栅极迅速充电并打开,其中R0为限流电阻。在上管打开期间,VOUT保持高电压,D1、MN3、MN4通路会有持续漏电流,因此MN7选用较小尺寸同时增加MN5、MN6管,在Vinh变为高电平瞬间产生一个高电平脉冲Vm打开MN5管,为MN1栅极电荷提供额外的泄放通路,降低静态电流,减小导通时间。

当Vinh为低电平时,MN3、MP0管关闭,MP1、MP2管打开,VCP端通过R1、MP2、D2形成到VOUT的通路,VA拉高并保持高于VOUT电压6 V左右,VB通过MN2跟随VD升高打开MN1管,从而使MN0栅极电容迅速放电并关断;同样地,由于在上管关闭期间R1、MP2、D2通路存在持续漏电流,因此R1选择大阻值以降低静态电流,MP1、MN2为MN1提供低阻抗充电通路,大大降低关闭时间。

上述设计中较小的静态电流和开关时间保证了较低的静态功耗和开关功耗。

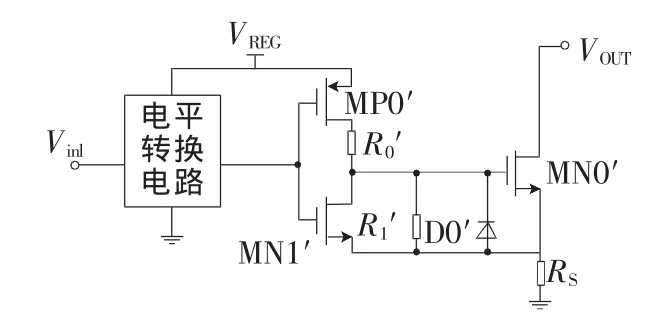

下管栅极驱动电路如图5所示,数字控制信号Vinl通过电平转换电路MP0′、MN1′对下管MN0′充放电,从而 实现功率管 的打开和关 闭。R0′、R1′、D0′与 上 管驱动中R0、R1、D0作用一致。

图5 下管栅极驱动电路

为了避免桥臂直通,本电路在栅极控制信号Vinh和Vinl之间了设置合理的死区时间,使两者同时为零。

在栅极驱动电路中,限流电阻的选择对于开关功耗至关重要。减小限流电阻阻值能减小开关时间及开关功耗,但若过小,开关功耗有可能不会降低反而急剧升高。

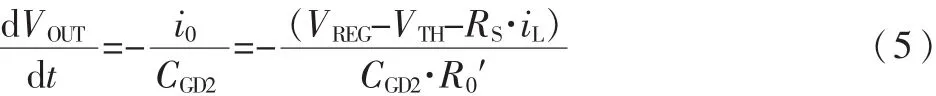

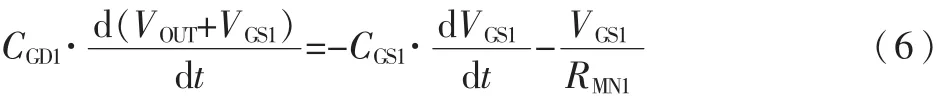

考虑到功率管的极间电容,栅极驱动电路如图6所示。该图表示上管MN0关闭,下管MN0′打开瞬间的情况。下管MN0′打开,VOUT电压下降,下管栅极驱动仅对米勒电容CGD2充电,充电电流为i0,此时MN0′的栅源电压恒定且近似为功率管阈值电压VTH。VOUT下降速率如式(5)所示,为定值。因为MP0′的导通电阻相比限流电阻R0′较小,式中忽略了它的影响。

图6 考虑极间电容的驱动极模型

上管MN0的栅源电压VGS1由式(6)给出,其中RMN1表示MN1的导通电阻。

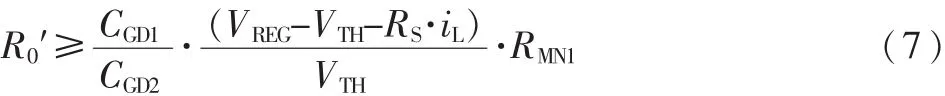

通过式(6)并且考虑电力MOSFET的特点,VGS1的最大值VGS1_MAX简化表达式为:

由式(7)可以得出,若要减小关闭时间,需减小限流电阻R0′,同时要增加MN1管面积来减小RMN1,因此存在性能与面积间的折中关系。同样,对于上管驱动中限流电阻R0有同样关系式。

另外过高的dVout/dt会引起晶体管反向恢复电流增加,导致功率管源-漏极电压超过干线电压VBB造成晶体管击穿,上述情况需要同时加以考虑,选取最合适的限流电阻R0′值。

4 仿真与测试结果

图7给出了带载步进电机正常工作时VS电压所反映的斩波过程,VS经历正电压、负电压和零电压分别代表电机线圈充电、快衰减和满衰减。

图7 斩波过程中VS电压瞬间波形

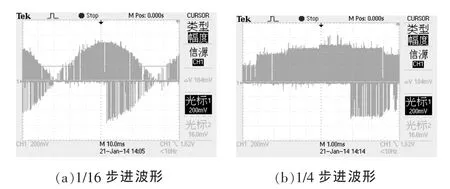

图8给出了角度细分下带载步进电机正常工作时VS电压,图8(a)是1/16步进时的整体正弦波形,图8(b)是1/4步进时的局部台阶。波形的毛刺是正常工作过程中续流体二极管的反向恢复电流引起的。

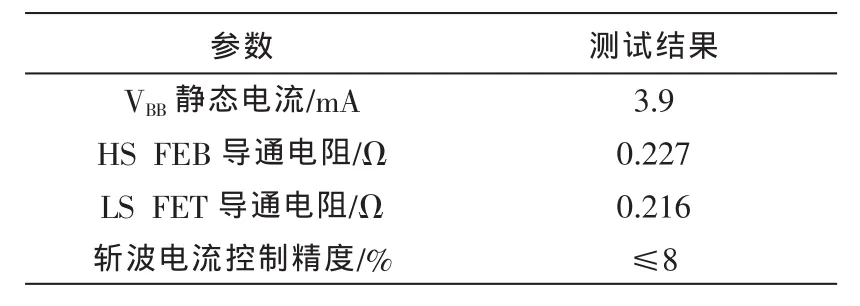

其他主要参数的详细测试结果以及目标值如表1所示。测试结果显示了该电路具有较低的功耗和较高的斩波电流控制精度,很好地实现了设计目标。

图8 角度细分时VS电压波形

表1 其他主要测试参数

5 结论

本文完成了应用于两相双极性步进电机的斩波横流驱动电路设计,测试结果表明满足驱动能力要求,具有较高的精度较低的静态功耗以及动态功耗,并且易集成角度细分控制。同样的结构也可以应用于三相及以上的步进电机驱动芯片或者直流电机中,因此具有广泛用途。

[1]仝建,龙伟,李蒙,等.高精度高可靠步进电机控制系统的设计及应用[J].电子技术应用,2013,39(12):41-44.

[2]Hassan Pooya Forghani-zadeh,Gabriel A.Rincon-Mora.Current-sensing techniques for DC-DC converters[J].IEEE Circuits and Systems,2002(2):577-580.

[3]Erisson.Industrial circuits application note-microsteppong[Z].2003,4,4.

[4]MOSTAFA,EMBABI,ELMALA.A60 dB,246 MHz CMOS variable gain amplifier for Sub-sampling GSM receivers[A].I SLPED[C].Califormia,USA,2001:117-122.

[5]BALLAN H,DECLERCQ M.High voltage devices and circuit in standard CMOStechnologies[M].Netherland,Kluwer Academic Publisher,1999:52-75

[6]WUCM,LAUWinghong,ChungHS.Analytical techique for calculating the output harmonice of an H-bridge inverter with dead time[J].IEEE Transactions on Circuit and System-I:Fundamental Theory and Applications,1999,46(5):617-627.