基于总线及BST的弹载计算机可测试性设计*

2014-07-05李自国杨智勇陆巍巍

李自国 杨智勇 陆巍巍

(1.91515部队 三亚 572016)(2.海军航空工程学院研究生管理大队 烟台 264001) (3.海军航空工程学院七系 烟台 264001)

基于总线及BST的弹载计算机可测试性设计*

李自国1,2杨智勇3陆巍巍3

(1.91515部队 三亚 572016)(2.海军航空工程学院研究生管理大队 烟台 264001) (3.海军航空工程学院七系 烟台 264001)

为了提高弹载计算机的可测试性,采用MTM测试总线及BST技术对其PCB板进行重新设计,经重新设计后的弹载计算机系统具有良好的可测试性,可以及时、快速、准确地检测与隔离故障,缩短故障检测与隔离时间,进而减少维修时间,降低系统维护成本,提高可靠性。

弹载计算机; 可测试性; 边界扫描; MTM测试总线

Class Number TP271+.5

1 引言

国内现用的弹载计算机大多由多块印刷电路板(PCB)构成。随着PCB板上所采用的高集成度、高封装、尺寸小的集成电路越来越多,测试越来越困难,传统的测试方法已无法对其进行高覆盖率的测试。为了便于测试,通常采用可测试性设计。对整个计算机的设计也应当这样,才可能使测试问题简化,这一点对于弹载计算机设计尤为重要[1]。

2 测试性设计技术概述

2.1 测试性设计

测试性设计是指在系统、分系统、设备、组件和部件的设计过程中,通过综合考虑并实现测试的可控性和可观测性、初始化与可达性、嵌入式测试(BIT)以及和外部测试设备兼容等,达到测试性要求的设计过程[2]。常用的测试性设计技术主要有内建自测试(BIST)、边界扫描测试、随机扫描测试、测试总线技术。前三种测试技术提供了测试的方法,测试总线技术提高了测试的效率。

2.2 边界扫描测试技术

随着微电子技术、微封装技术和印制板制造技术的不断发展,印制电路板变得越来越小,密度越来越大,复杂程度越来越高,使用万用表、示波器测试芯片的传统“探针”方法已不能满足要求。20世纪80年代,联合测试行动组(Joint Test Action Group,JTAG)起草了边界扫描测试(Boundary Scan Testing,BST)技术规范,并在1990年被批准为IEEE标准1149.1-1990规定,简称JTAG标准[3]。该规范提供了有效测试引线间隔致密的电路板上元器件的能力。

边界扫描技术中的“边界”是指测试电路被设置在集成电路器件功能逻辑电路的四周,位于靠近器件输入、输出引脚的边界处。所谓“扫描”是指连接器件各输入、输出引脚的测试电路实际上是一个串行移位寄存器,这种串行移位寄存器被称为“扫描路径”,沿着这条路径可输入由“1”和“0”组成的各种编码,对电路进行“扫描”式检测,从输出结果判断其是否正确[4~5]。边界扫描测试结构如图1所示。

图1 边界扫描结构

其中:TCK为测试时钟输入、TMS为测试模式选择、TDI为测试数据输入、TDO为测试数据输出、TRST为测试复位

边界扫描测试有两大优点:一个是方便芯片的故障定位,迅速准确地测试两个芯片管脚的连接是否可靠,提高测试检验效率;另一个是,具有JTAG接口的芯片,内置一些预先定义好的功能模式,通过边界扫描通道使芯片处于某个特定的功能模式,以提高系统控制的灵活性和方便系统设计。

2.3 MTM测试总线技术

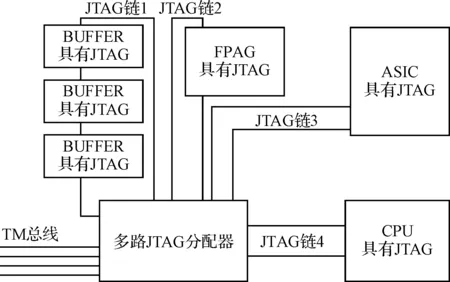

MTM总线是具有多站点拓扑结构的同步串行背板总线。MTM总线由四根必需的和一根可选的信号线组成,采用主从通信规约,如图2所示。总线设计时只允许有一个主模块,不过对于配置为容错工作方式的总线,总线控制权可以移交给备份主模块。在这种总线体系中,存在三种类型模块:主模块、备份主模块(具有主模块功能的从模块)、从模块。不论哪种类型模块,模块地址都由8位二进制数表示,可以分为250个普通模块地址和一个广播地址、四个分组广播地址、一个记忆缺失地址,允许最多250个从模块同时挂在该总线上[6~7]。

图2 MTM总线结构示意图

其中:MMD为模块数据信号线、MSD为从模块数据信号线、MCTL为主模块控制信号线、MPR为暂停请求信号线、MCLK为时钟信号线

MTM总线是主从分布式通信系统,主模块通过发送头包,启动与从模块进行信息交换。主从模块间的信息传递由各自的链路层状态机控制。

3 弹载计算机的可测试性设计分析

3.1 单链板级测试

在进行弹载计算机设计时,可以尽可能地运用边界扫描测试技术进行可测试性设计。最理想的情况是待设计电路板上用到的器件都具有边界扫描结构,都是边界扫描器件,只需将它们的TDI和TDO首尾相接构成菊花链,然后共用TMS和TCK信号,该连接方法被称作单链板级测试。单链板级测试可实现在电路板上串行互连多个具有JTAG功能的IC(集成电路Integrated Circuit),形成一个多IC的边界扫描链,TDI和TDO串行连接,板上IC共同组成一个JTAG链;亦可用于对单个IC、板上IC、IC间通路、板与板间通路进行测试。现阶段,并不是所有的芯片都具有边界扫描结构体系,某些非边界扫描结构芯片在电路板设计时必须采用,这就为电路板的可测试性设计带来了挑战。目前由于扫描器件和非边界扫描器件混合组装的电路板测试问题仍是板级可测试性设计研究的关键问题[8~9]。针对上述情况,可将非边界扫描电路用扫描电路完全包围,利用边界扫描器件的扫描结构实现一个和多个的扫描链路,使板中每一内部点都具有可控制性和可观察性,从而实现完全的扫描链路测试。这些附加扫描结构主要通过以下两种方法获得:

1) 边界扫描器件法:在进行电路板的可测性设计时,尽可能选用同功能的带有边界扫描结构体系的器件置换原非边界扫描器件,从而使其所在电路板包含边界扫描结构,实现电路板内部所有结点的可控和可观测。

2) 边界扫描结构置入法:利用扫描器件的边界扫描单元实现对非边界扫描电路的可控又可测的方法。通过待测非边界扫描器件周围的边界扫描器件提供的测试通道,实现测试矢量加载和测试响应数据的读取。如图3所示,如果不考虑此PCB设计的可测性问题,图中的3#器件(具有边界扫描结构体系的线驱动芯片)是不存在的,同时6#,8#器件是同功能的非边界扫描芯片。因此,该PCB上面就有2#,4#,6#,7#,8#器件是不具有边界扫描体系结构的芯片,那么此PCB上的一些网络节点就不具有可控性和可观测性。这势必为板级测试、故障诊断带来相当大的困难。

图3 单链板级可测试设计

为了PCB测试方便,节约测试成本,在设计满足要求功能的PCB的时候就应该考虑设计的可测性。第一,在不具有边界扫描结构体系的2#,4#之间增加一具有边界扫描结构体系的驱动芯片(3#器件);第二,将6#,8#用相同功能且具有边界扫描结构体系的器件替换,使用带有边界扫描结构体系的器件包围非边界扫描器件。这样既不改变原有电路的功能,又能很好地解决了电路板原先一些节点的可测性问题,使板上所有节点网络都能通过边界扫描通道而变得可控和可观测。

3.2 多链板级测试

单链板级测试要求板上扫描链路覆盖所有JTAG的IC,适用板上IC数量不多时的情况。当板上IC数量多,扫描链路很长时会带来扫描时间长,因此多IC电路板多用多链路测试,如图4所示。

图4 具有多个边界扫描链的板级测试

多链路边界扫描,通过地址扫描端口和多端口分配器共享板上MTM总线接口,可根据电路板上功能和IC不同划分多个边界扫描链路,对每个链路分配不同的扫描码,针对性强,单个链路中编码设计简单。但链路与链路间通路测试结构复杂,多链路协同测试的设计要求不低于板级与板级间通路测试要求。

4 弹载计算机可测试性设计

4.1 采用单链板级测试技术的弹载计算机设计

根据单链板级测试可测试性设计思想,使用IEEE 1149.1总线将弹上计算机所有模块/电路板的扫描链首尾连接成菊状链,整个系统对外只呈现一个测试接口;将IEEE1149.1总线的四条信号线——TDI、TDO、TCK、TMS分布在底板上;将前一个电路板的TDO与下一个电路板的TDI相连,如图5所示。

图5 采用单链板级测试技术的弹载计算机设计

依据此构成方案进行系统测试时候,需要底板上的每个插槽中都要有电路板,如果某处有一个槽是空的,那么菊状链路断开,弹载计算机将是不可测的。并且,长的扫描链路需要长的边界扫描测试向量,这样的测试向量不仅难以产生,而且使用这些测试向量进行测试时也需要较长的时间。

4.2 采用MTM测试总线结合边界扫描技术的弹载计算机设计

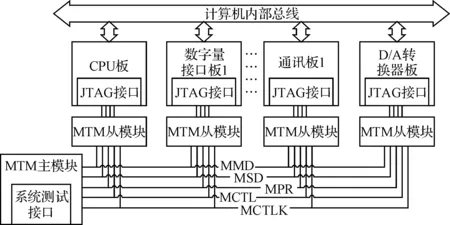

使用MTM测试总线结合边界扫描技术则可以实现层次化测试结构,该结构采用多级测试维护总线,构成了芯片级、板级、子系统级、系统级的层次化测试结构,整个系统对外只呈现一个测试接口[10],如图6所示。

图6 采用MTM测试总线结合边界扫描技术的弹载计算机设计

图6中主、从模块以及底板上的MTM测试总线都是在不破坏该系统原有逻辑功能的基础上为了解决系统的可测性问题而引入的。在设计过程中,只需要在系统底板上设计额外的MTM测试总线以及插槽,然后嵌入现成的封装好的主、从模块即可。MTM主模块控制器主要作用是链路层协议解析和微控制器接口,从控制器的作用主要是从模块接口和控制边界扫描链路。整个弹上计算机系统对外只呈现一个用于测试的接口,进行系统测试的时候,此接口通过USB、RS232、1553B或其它总线接口与测试设备通信,测试设备上运行与各主从模块配套的系统测试软件。

5 结语

对弹载计算机利用MTM测试总线结合边界扫描技术进行设计后,具有以下优点:

1) 可扩展性好

分布式测试采用开放式总线结构,具有良好的可扩展性。若增加系统模块,仅需对主控软件进行简单的修改或调整,而不需要改变测试系统的其他硬件结构。此外,将某个单元模块从系统中移出也不会影响系统的整体测试。

2) 简化测试向量

由于采用寻址的方式,要对某个从模块进行测试,只需发送地址命令选中该从模块,再送测试向量。并不需要为了测试某一模块,而扫描所有模块。所以可以大大简化用于测试的向量。

3) 加快测试速度

采用分布式测试策略,各模块可以并行地进行测试,从而可以大大减少整个系统的测试时间。

4) 提高维修性

由于各模块的功能相对独立,在维修过程中可以利用备办模块直接替代相同功能的故障模块,从而加快了系统的维修。

经此设计的弹载计算机系统具有良好的可测试性。可以及时、快速、准确地检测与隔离故障,缩短故障检测与隔离时间,进而减少维修时间,降低系统维护成本,提高可靠性。

[1] 沈绪榜.弹(箭)载计算机[M].北京:宇航出版社,32-33.

[2] 韩国泰.改进目前测试性设计的若干建议[J].测控技术,2003,22(11).

[3] 潘小龙.基于边界扫描技术的测试系统的研究与应用[D].南京:南京航空航天大学,2008.

[4] 刘九洲,王健.边界扫描技术发展综述[J].电光与控制,2013,2(20).

[5] 赵红军,杨日杰,崔坤林,等.边界扫描测试技术的原理及其应用[J].测控技术,2005(11):20-24.

[6] IEEE Std 1149.4-1999: IEEE Standard for Mixed_signal Test Bus[S]. IEEE Computer Society,1999,6.

[7] IEEE Std 1149.6 TM: IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks[S]. IEEE Computer Society,2003,7.

[8] 张乐.基于边界扫描的板级测试方法研究与应用[D].南京:南京理工大学,2012.

[9] 代桃.多板卡电子系统的可测试性设计与实现[D].长沙:电子科技大学,2011.

[10] 王帅.通用型MTM总线主模块控制器的设计与实现[J].测控技术,2012,31(8):63-67.

Testability Design of Missile Onboard Computer Based on Bus and BST

LI Zifuo1,2YANG Zhiyong3LU Weiwei3

(1. No. 91515 Troops of PLA, Sanya 572016) (2. Postgraduate Team Brigade, Naval Aeronautical Engineering Institute, Yantai 264001) (3. Department 7, Naval Aeronautical Engineering Institute, Yantai 264001)

In order to raise the testability of missile onboard computer, MTM test bus and BST technology is used to redesign it PCB board. The redesigned computer system has a good testability, and can accomplish fault detection and isolation timely, fast and accurately, shortening the time of fault detection and isolation, and reducing the maintenance time and cost of the system, and improving the reliability of the system.

missile onboard computer, testability, boundary scan, MTM test bus

2014年6月6日,

2014年7月23日

李自国,男,工程师,研究方向:控制工程。杨智勇,男,博士,讲师,研究方向:控制与测试。陆巍巍,男,讲师,研究方向:电子测试。

TP271+.5

10.3969/j.issn1672-9730.2014.12.045