桥接故障的物理提取和高效测试

2014-07-02韦素芬

韦素芬

(集美大学信息工程学院,福建 厦门 361021))

0 引言

当今,对于多数集成电路设计公司来说,桥接故障的测试仍旧是一个较新的领域,甚至桥接故障测试覆盖率仍未被纳入产品测试的要求中.但是,由于工艺尺寸减小和密集度增大,势必引入更多的桥接故障,这种趋势会使得桥接故障测试日益重要,尤其对于那些应用于医疗电子和汽车电子领域的、要求零缺陷的集成电路芯片.

作为传统固定型故障模型,N重固定测试的测试对象是芯片中所有的固定故障候选点,其测试结果可以覆盖一部分桥接故障.大量的研究结果[1-3]表明:随着N的增大,桥接故障测试覆盖率会有小幅提高,但提高幅度与N的增大远不成比例,并且N增大的代价是需要大量测试图形,经济性差.内置多重固定测试与N重固定测试原理基本相同,是N重固定测试的一种替代型测试,但是桥接故障测试覆盖率仍旧不高,测试的有效性改善不明显[4].深亚微米工艺下桥接故障的发生与版图情境密切相关.但传统N重固定测试和内置多重固定测试与版图物理位置无关,且对于桥接故障测试是非针对性的.

确定性桥接故障测试法的研究对象是芯片中容易发生桥接故障的所有候选点,是否为候选点应基于器件的版图信息[5]来判断.相比N重固定测试和内置多重固定测试来说,桥接故障测试的针对性强、测试覆盖率相对高[6].但是该方法在业界仍未被广泛采用的原因是:自动测试向量生成 (Automatic Test Pattern Generation,ATPG)时间非常长,测试图形数量巨大,在整体产品测试时,不得不去除大量的测试图形,测试覆盖率较高的优点有可能随之丧失了[7-10].本文基于版图信息,提出7种桥接故障候选点的物理模型,并给出候选点提取的方法.同时提出以确定性桥接故障测试为主体的测试方法,在流程上先采用内置多重固定测试,可覆盖到一定数量的确定性桥接故障候选点.

1 桥接故障候选点的物理模型

深亚微米工艺的复杂性,使得桥接缺陷不仅发生于信号线之间边对边紧密相邻的这一种情境[3].本文充分考虑工艺步骤造成缺陷的可能性,提出了7种桥接故障的物理模型:边对边;角对角;线端;通孔对通孔;宽线上的边对边;通孔的角对角;最小线宽的边对边.

1.1 边对边

如图1a所示,同层的两根并行相邻金属线,间距为设计规则要求的最小间距“d”,当其平行长度大于等于“l”时,可能发生桥接故障.

1.2 角对角

如图1b所示,同层两根金属线的角和角相邻,则当角和角之间的间距等于“d1”时有可能发生桥接故障.以曼哈顿 (Manhattan)形式绕线的两条最小距离为“d”(最小间距)的金属线,其角和角之间的距离

1.3 线端

如图1c所示,位于同层同绕线通道的两根金属线,当同时满足下面3个条件时有可能发生桥接故障:线的终端相对的两个平行截面之间的间距等于最小间距“d”;最宽线的宽度大于等于“w”;最短线的长度大于等于“l”.

1.4 通孔对通孔

如图1d所示,同层正对相邻的两个通孔,其正对两平行截面的间距等于最小间距“d”时有可能发生桥接故障.

1.5 宽线上层的边对边

如图1e所示,宽金属线 (通常为电源线),其上层有两根平行金属线,其间距“d2”大于最小间距“d”.但由于芯片制造过程中,生成宽金属线的化学机械抛光 (CMP)步骤会使得宽线的凹陷效应更显著,宽线水平面的变形,也会影响其上层的两平行线之间容易发生桥接故障.

1.6 通孔的角对角

如图1f所示,同层非正对的两个通孔,只要它们之间有角和角相邻,则当角和角之间的间距等于“d1”时有可能发生桥接故障.通孔边延长线之间平行线间距为最小间距“d”,通孔角和角之间的距离

1.7 最小线宽的边对边

如图1g所示,同层的两根相邻金属线,且至少其中一根是设计规则规定的最小宽度的线,当其间距等于最小间距“d”,且正对平行长度大于等于“l”时,可能发生桥接故障.

图1 桥接故障候选点的物理模型Fig.1 Physical models of bridging fault candidates

2 提取桥接故障候选点

7种桥接故障模型均与“线对”和“通孔对”有关,其间距“d”为设计规则的最小间距 (宽线上层的边对边的间距“d2”除外).平行长度“l”越长,发生故障可能性越大.“l”提取阈值设置是否合理决定了故障候选点的准确性和数量,以及之后的ATPG时间和测试时间.这个阈值与工艺密切相关.本研究基于TSMC 90 nm工艺经验值,以及测试中易发生桥接故障的经验值,最终确定最小平行长度“l”的阈值为1 μm:平行长度大于等于1 μm即为桥接故障候选点.

2.1 提取桥接故障候选点的设计规则

候选点的提取方法:基于7种物理模型,在提取阈值限制下,编写专门提取桥接故障候选点的设计规则.利用Mentor Graphics的Calibre DRC工具将“线对”和“通孔对”提取出[11].本研究的提取规则按照TSMC DRC规则的命名要求,具体如下.

2.1.1 边对边的提取规则

采用线最小间距规则Mx.S.1,提取所有最小间距“线对”,再用平行长度阈值“l”过滤.

2.1.2 角对角的提取规则

采用线最小间距规则Mx.S.1和拐角线最小间距规则Mx.S.5,提取所有间距为“d1”的“线对”.

2.1.3 线端的提取规则

提取3个参数,之间为“与”的关系,提取满足条件的“线对”,如图1c,1)两线正对截面间最小间距为“d”:提取规则为Mx.S.1;2)两线之最宽线的宽度为“w”:提取规则为Mx.W.1;3)两线之最短线的长度为“l”:用最小面积 (提取规则为 Mx.A.1)除以最小宽度 (提取规则为Mx.W.1)来提取.

2.1.4 通孔对通孔的提取规则

采用通孔最小间距规则VIAx.S.1,提取所有最小间距“通孔对”.

2.1.5 宽线上层的边对边的提取规则

提取2个参数,之间为“与”的关系,如图1e,1)上层两平行线的间距为“d2”:提取规则为Mx.S.1,设置此间距为最小间距的1.5倍:d2=1.5×d;2)其下层的宽金属线面积大于等于2.25,用最小面积 (提取规则为Mx.A.1)提出.

2.1.6 通孔的角对角的提取规则

采用通孔最小间距规则VIAx.S.1和拐角通孔最小间规则VIAx.S.5,提取所有间距为“d1”的“通孔对”.

2.1.7 最小线宽的边对边的提取规则

采用最小宽度线的最小间距规则M1.S.2,提取所有“线对”;再用平行长度阈值“l”过滤.

2.2 提取出的故障候选点的示意

图2是Calibre DRV工具显示出测试芯片1局部的版图.在这部分电路版图中包含3种物理模型所表征的若干个桥接故障候选点 (边对边、线端、角对角).在图2中,绿色为第一层金属线 (M1),红色为有源区,蓝色为“线对”之间故障候选点.

图2 提取出的桥接故障候选点Fig.2 Extracted bridging fault candidates

3 综合型测试流程

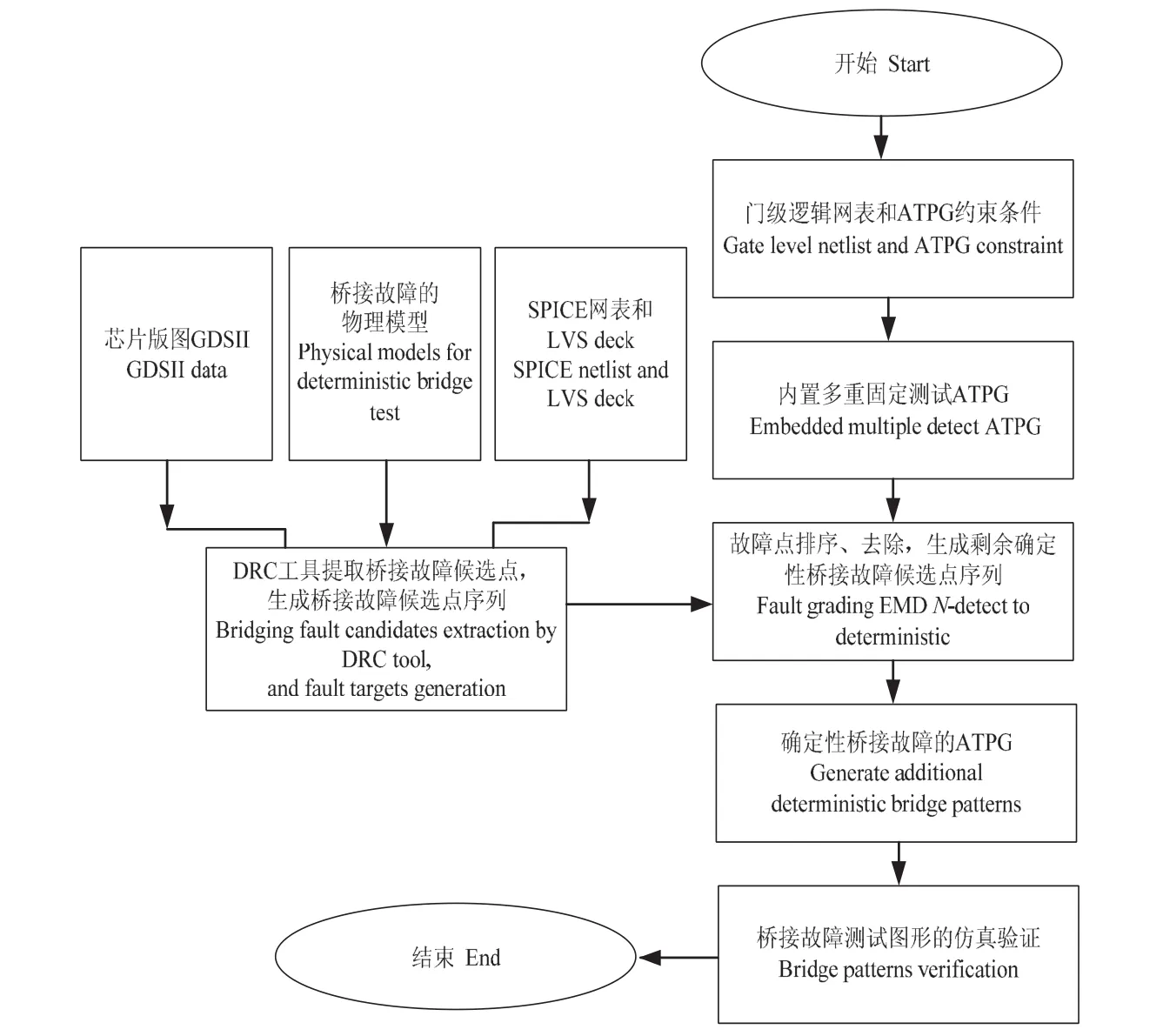

本文提出的以确定性桥接故障测试作为主体的综合型测试方法,其桥接故障候选点是提取出的“线对”和“通孔对”,以4点主控型行为模型[5]对它们进行ATPG.具体流程如图3所示.

图3 桥接故障的综合型测试方法流程图Fig.3 The integrated bridging fault test flow

该流程的核心思想是要进行针对固定故障进行的ATPG和测试.那么首先需生成固定测试所用的内置多重固定测试 (或N重固定测试)图形,再作故障排序 (fault grading)分析.由于固定测试势必覆盖到部分桥接故障点,那么在总的桥接故障候选点中先去除掉这些已覆盖到的桥接故障点,再对剩下的故障候选点采用确定性桥接故障测试法生成测试图形.

该流程的优点:确定性桥接故障测试基于物理信息,必须在整个芯片版图设计完成后才能提取候选点、进行ATPG,浪费设计周期.而传统内置多重固定测试 (或N重固定测试)只需门级逻辑网表,在版图开始前就可以进行ATPG.将两者结合的综合型测试可有效利用设计周期,用数量较少测试图形即可实现高测试覆盖率.

对流程图的两点说明:1)采用本研究提出的7种物理模型和提取方法来生成总桥接故障候选点序列;2)在固定测试阶段采用N重固定测试或内置多重固定测试,最终得到桥接故障测试覆盖率几乎无差异;以内置多重固定测试取代N重固定测试,可大幅度地减少测试图形数量、节约测试时间.

4 ATPG结果与分析

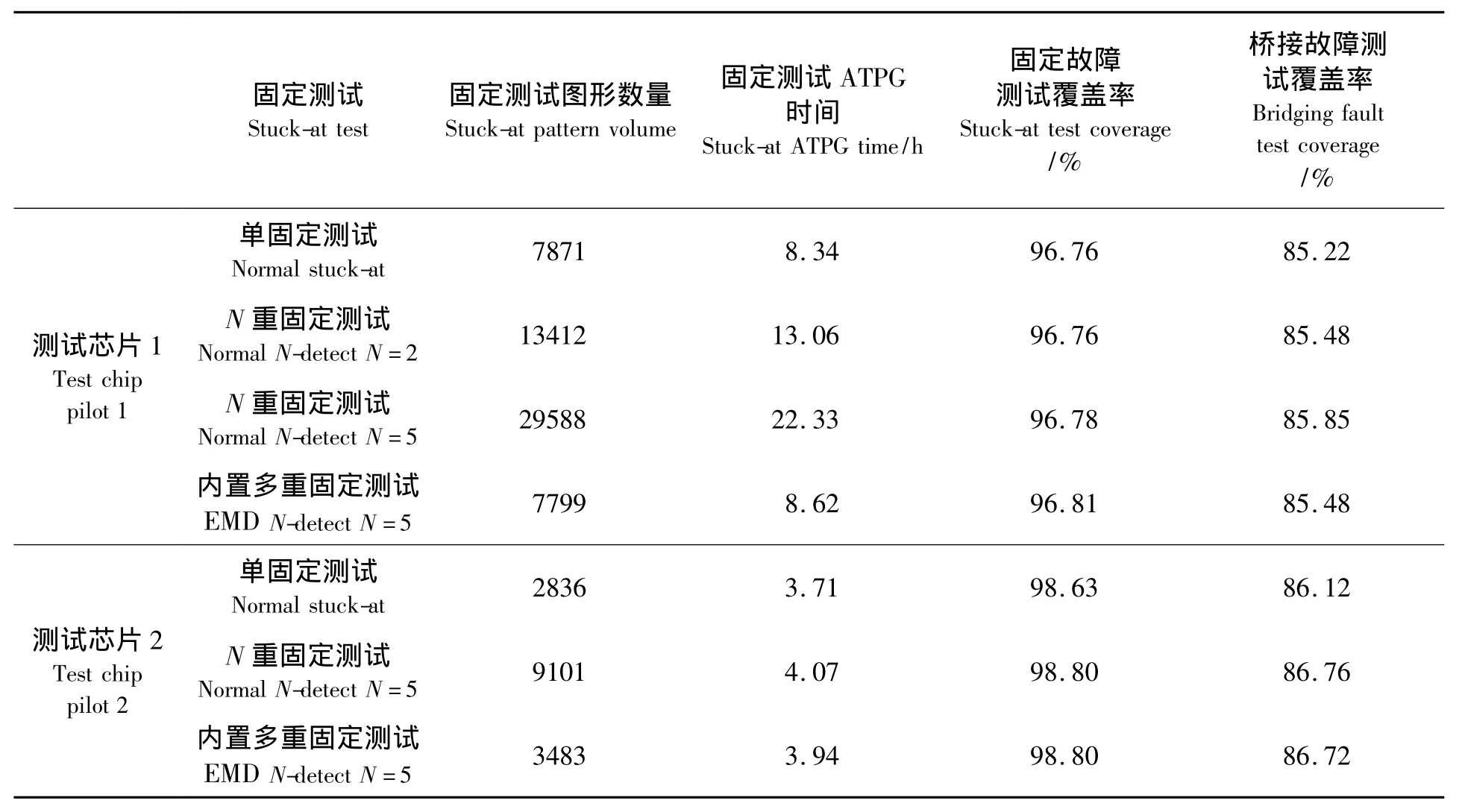

两个测试芯片均采用TSMC CMOS90 nm工艺.测试芯片1共有180000个扫描寄存器,测试芯片2共有50000个扫描寄存器.按照图3表征的综合型测试流程进行ATPG、仿真验证和结果分析.表1对比列出了测试芯片1和测试芯片2的固定测试的ATPG时间长度、测试图形的数量、测试覆盖率.同样,表2对比列出了测试芯片1和测试芯片2的桥接故障综合型测试的ATPG时间长度、测试图形的数量、测试覆盖率.

4.1 固定测试

由表1可看出:测试芯片1的固定测试覆盖率达到96%以上,测试芯片2的固定测试覆盖率达到98%以上;由表1对于固定测试,采用内置多重固定测试最有效——以相对较短的固定测试ATPG时间和较少的固定测试图形数量,达到了相对较高的固定测试覆盖率.

表1 固定测试的ATPG结果对比Tab.1 The ATPG result comparison of stuck-at test

4.2 桥接故障测试

1)采用确定性桥接故障测试方法来针对性地测桥接故障,比用固定测试法来测桥接故障,其桥接故障测试覆盖率显著提高:芯片1的桥接故障测试覆盖率从85%提高到90%(见表1).芯片2的桥接故障测试覆盖率从86%提高到89%(见表1).

2)本研究提出的综合型方法,在保持确定性桥接故障测试的高覆盖率基础上,不仅充分地利用版图完成前的设计时间,而且缩短了ATPG时间.更重要的是,很大程度上减少了测试图形数量 (从表2可得),这样会大幅节约芯片测试时间,提高测试效率和效益.

3)从表2还可以看出:在综合型测试方法中,在固定测试阶段采用内置多重固定测试法,最终得到的桥接故障测试ATPG结果最优:以合理的ATPG时间实现较高的桥接故障测试覆盖率,且测试图形数最少.

表2 综合型桥接故障测试流程的ATPG结果对比表Tab.2 The ATPG result comparison of integrated bridging fault test flow

5 结束语

本研究为了准确而完整地提取桥接故障候选点,提出7种基于版图的桥接故障物理模型,并且给出对每种故障候选点进行提取的DRC规则.为减少确定性桥接故障的测试时间,本文提出了将内置多重固定测试和确定性桥接故障测试相结合的综合型方法.用两个测试芯片对传统N重固定测试、内置多重固定测试和以确定性桥接故障测试为主体的综合型测试进行了全面地比较,验证了综合型测试流程的有效性.在没有引入新的测试负担的情况下,充分利用现有的工程方法进行有效地配合使用,取得了更好的测试效果.

[1]POMERANZ I,REDDY S M.A measure of quality for N-detection test sets [J].IEEE Transaction on Computers,2004,10(1):1497-1503.

[2]AMYEEN M E,VENKATARAMAN S,OJHA A,et al.Evaluation of the quality of N-detect scan ATPG patterns on a processor[C]//IEEE.IEEE International Test Conference.Charlotte,NC:IEEE Conference Publications,2004:669-678.

[3]ZACHARIAH S T,CHAKRAVARTY S.Extraction of two-node bridges from large industrial circuits[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2004,45(4):357-367.

[4]JEROEN GEUZEBROEK,ERIK JAN MARINISSEN,ANANTA MAJHI.Embedded multi-detect ATPG and its effect on the detection of unmodeled defects[C]//IEEE.IEEE International Test Conference.Santa Clara:IEEE Conference Publications,2007:1240-1248.

[5]GKATZIANI M,KAPUR R,QING S.Accurately determining bridging defects from layout[C]//IEEE.Design and Diagnostics of Electronic Circuits and Systems.Kraków:IEEE Conference Publications,2007:1012-1021.

[6]BENWARE B,SCHUERMYER C,RANGANATHAN S.Impact of multiple-detect test patterns on product quality[C]//IEEE.IEEE International Test Conference.Charlotte NC:IEEE Conference Publications,2003:1031-1040.

[7]FANG H X,WANG Z Y,GU X L Deterministic test for the reproduction and detection of board-level functional failures[C]//IEEE.Asia and South Pacific Design Automation Conference,ASP-DAC.Yokohama:IEEE Conference Publications,2011:491-496.

[8]CHEN G,RAJSKI J,REDDY S M,et al.N-distinguishing tests for enhanced defect diagnosis[C]//IEEE.IEEE A-sia Test Symposium.Taichung:IEEE Conference Publications,2009:183-186.

[9]VENKATARAMAN S.An experimental study of n-detect scan ATPG patterns on a processor[C]//IEEE.22nd VLSI Test Symposium.Napa Valley,CA:IEEE Conference Publications,2004:23-28.

[10]POMERANZ I,REDDY.S M Definitions of the numbers of detections of target faults and their effectiveness in guiding test generation for high defect coverage [C]//IEEE.DATE Conference.Munich:IEEE Conference Publications,2001:504-508.

[11]ALLAN G A.Targeted layout modifications for semiconductor yield/reliability enhancement[J].IEEE Transaction on Semiconductor Manufacturing,2004,4(17):573-581.