高速数字电路互连时序模型与布线长度分析※

2014-07-02唐思超

唐思超

(北京世纪瑞尔技术股份有限公司,北京100085)

引 言

在高速电路设计领域,关于布线有一种几乎是公理的认识,即“等长”走线,认为走线只要等长就一定满足时序需求,不会存在时序问题。本文对常用高速器件的互连时序建立模型,并给出一般性的时序分析公式。为了体现具体问题具体分析的原则,避免将公式当成万能公式,文中给出了MII、RMII、RGMII和SPI的实例分析。在实例分析中,结合公式分析和理论分析两种方法,用实例证明公式的局限性和两种方法的利弊。最后,基于这些实例分析,给出了SDRAM和DDR SDRAM等布线的一般性原则。

1 典型高速器件互连时序模型

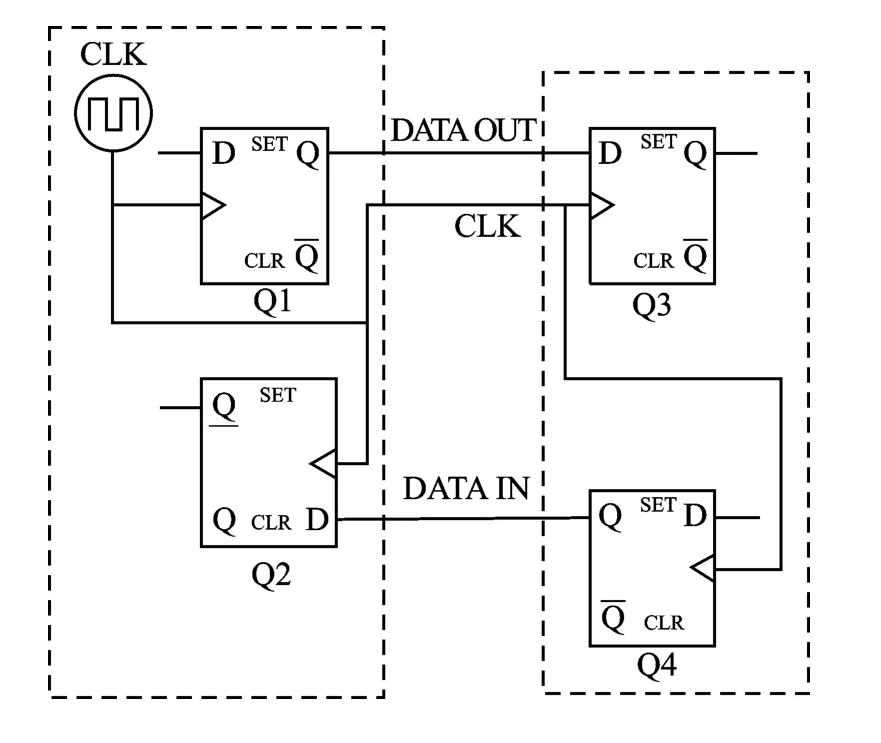

图1为通用高速器件互连接口简化模型。图中,左侧虚线框表示通信器件双方的主控端,常见的实际情形有:SDRAM控制器、SPI主控制器等。经过适当的演化,基于本模型很容易得到I2C主控端、MII接口的TX组模型、RMII共享时钟模型以及DDR控制信号与地址信号的互连模型等。右侧虚线框表示通信中的被动端。本模型中,数据是双向的,但是时钟是单一方向的。这个特点是本模型的适应场景。

图1 简化的器件互连模型

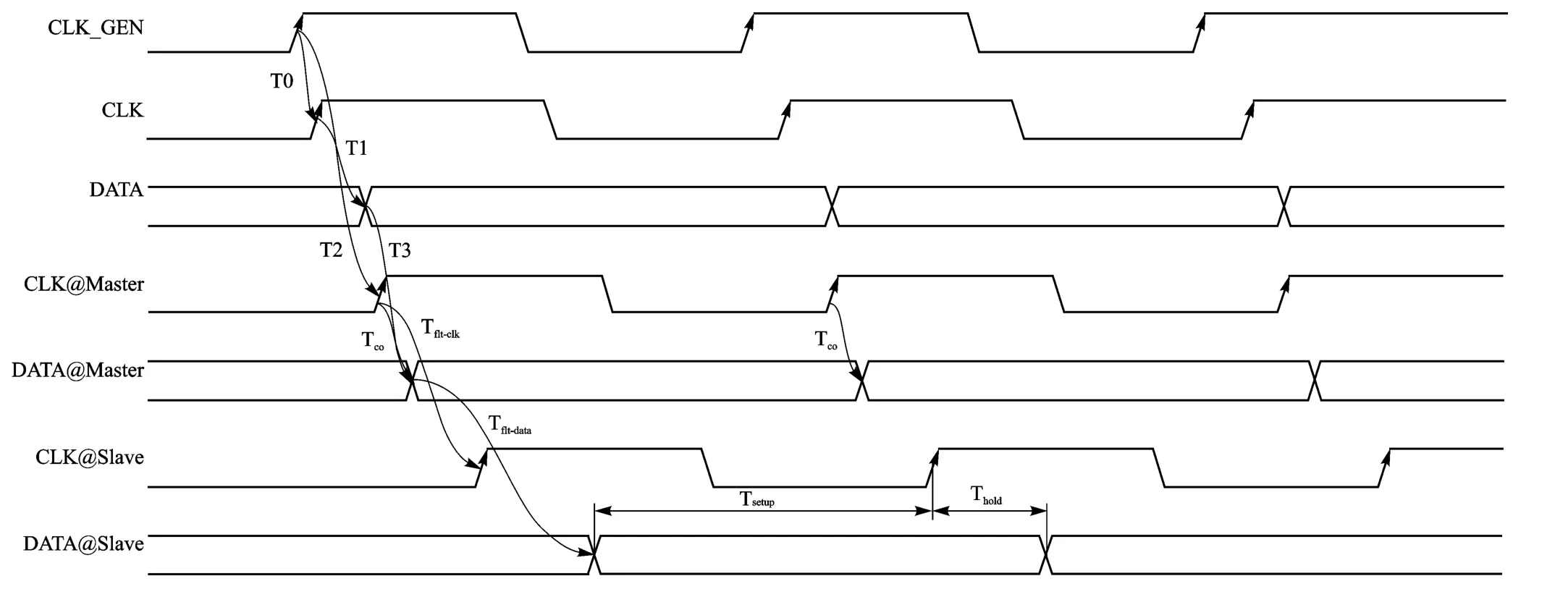

图2是基于本模型的数据写时序关系图。图中,T0表示主控端内部时钟发生器CLK发出的时钟到达触发器Q1时钟输入端的延时;T1表示触发器Q1接收到时钟后到Q1输出端出现数据的延时;T2表示主控端内部时钟发生器CLK发出的时钟到主控端外部时钟输出引脚的延时;T3表示内部触发器Q1输出的数据到达主控端外部数据输出引脚的延时。通常,半导体制造商不会给出T0~T3这些参数,而是给出一个用于反映这些参数最终等价效果的参数,即主控端外部数据引脚上出现数据时相对于外部时钟引脚出现时钟信号的延时,这里记为Tco。

图2 数据写时序关系图

时序分析最关心的参数是信号到达接收端的最终建立时间和保持时间是否符合器件要求,这里将建立时间和保持时间分别记为Tsetup和Thold。Tflt-clk和Tflt-data分别表示时钟信号和数据信号的飞行时间,即它们在对应走线上的延时。Tjitter-clk和Tjitter-data分别表示时钟信号和数据信号上的抖动时间。

分析图2中时钟信号和数据信号的相互关系,可以发现:由于Tco的存在,如果器件间的时钟和数据走线等长,则在接收端,用于发送时间的边沿不能用于数据的采样。为了在接收端对数据进行正确采样,必须调整时钟和数据走线的关系,有两种方法:第一,时钟走线长于数据走线,使得数据飞行时间较时钟短,此时,在接收端仍然可以使用产生数据的时钟沿采样数据;第二,数据走线比时钟长,使得数据飞行时间较时钟长,此时,可以使用产生数据时钟沿的下一个上升沿采样数据。

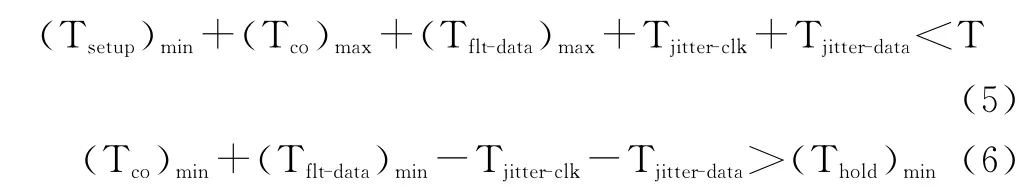

实际工程中,设计人员一般使用第二种方法并希望对于数字系统的建立时间和保持时间都留有一定裕量,因此可以得出下列公式,即建立时间和保持时间公式:

显然,Tco是器件的固有参数,Tflt-data和Tflt-clk取决于对应的PCB走线长度和走线层等。如果Tflt-data和Tflt-clk的差过小,则导致数据的保持时间不足;如果过大,则会使得建立时间不足。因此,Tflt-data和Tflt-clk的差存在上限和下限双重限制。

图3是基于本模型的数据读时序关系图。

图3 数据读时序关系图

图中参数含义与图1相同。需要注意的是:在读关系中,时钟首先需要从主控端传到从端,待从端发出的数据回到主控端后,才能由主控端对数据进行采样。因此,建立和保持时间的公式如下:

其中,Tco是器件的固有参数,Tflt-data和Tflt-clk取决于对应的PCB走线长度和走线层等。如果Tflt-data和Tflt-clk的总和过小,则导致数据的保持时间不足;如果过大,则会使得建立时间不足。因此,Tflt-data和Tflt-clk的和存在上限和下限双重限制。

2 时序分析实例

2.1 MII接口

MII接口是最常用的百兆以太网PHY芯片与MAC间的接口。对MII接口使用第1节中的公式进行分析,可知对于MII的RX通道信号组,信号间允许的走线差值可达数十厘米,可认为无需考虑等长;对于MII的TX通道信号组,分析后可知其走线和有上限。在实际布线中,TX通道信号组的走线应当越短越好。对MII接口使用理论分析法,可以得出与公式法相同的结论。

注意,时序关系不代表不需要考虑反射问题。当信号在走线上的传播和返回延时比信号的上升时间长时,就有必要考虑是否进行终端阻抗匹配以抑制反射。

2.2 RMII接口

RMII接口也是常用的百兆以太网PHY芯片与MAC间的接口。实际中使用时,一般会在外部使用一颗符合双方精度要求的50 MHz振荡器,为MAC和PHY提供共用时钟基准。

为了简化时序分析,可以将外部振荡器至MAC和PHY双方的走线设计为等长,此时时钟信号在两者的时钟输入引脚上具有完全一致的时刻。

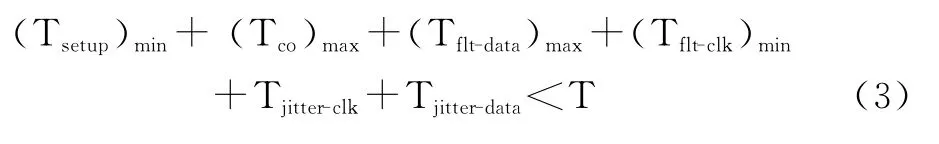

当时钟信号等时刻到达收发双方的输入引脚时,具有如图4所示的时序模型,因而仅需分析数据线的长度。

图4 共用时钟的RMII时序模型

根据时序模型,可得出时序公式:

对RXD、CRS_DV和RX_ER信号以及TXD和TX_EN信号分别使用式(5)、(6)进行分析,可得到TX和RX通道组内信号的走线长度关系。

2.3 RGMII接口

RGMII接口是最常用的千兆以太网PHY芯片与MAC间的接口。依据标准,千兆MAC和PHY有可选择实现的RGMII-ID功能。注意,RGMII时序为DDR模式。图5是RGMII的时序模型,即DDR模式的时序图。

式(7)和(8)是对应的建立时间和保持时间约束公式。式中,Tstrobe–data表示选通信号相对数据信号的传送延时;Tdata-strobe表示数据信号相对选通信号的传送延时。

将RGMII时序参数中的相应值带入公式(7)和(8),可得到RX通道和TX通道组内信号走线长度的关系。对RGMII接口进行理论分析,结果与公式计算一致。

2.4 SPI接口

出于成本因素考虑,越来越多的消费电子使用SPI FLASH作为存储器,SPI的通信速度也越来越高。目前,多数MPU都可以支持100 Mbps以上的SPI通信速度且支持多I/O通信。SPI通信的时序关系略——编者注。

结 语

进行时序分析的关键点首先在于必须对被分析的时序关系非常清楚,能够深刻理解当前对象的时序协议。其次,时序分析要针对具体问题具体分析,不存在所谓的万能时序公式。有时,单纯依靠理论分析或者时序关系公式并不一定能够解决问题,而是要两者结合使用。

对于高速信号的布线而言,存在“等长”说,即很多工程师认为只要所有的线路尽可能等长,就一定满足时序要求。事实上,只有那些时钟和数据由同一个器件发出,由另一个器件接收,并且发送端的建立时间和保持时间恰好满足接收端需求时,“等长”才算是一种偷懒的方法。除此以外,尤其是那些通过单向时钟驱动、采样双向数据或者逆向数据的信号,必须具体问题具体分析。当然, 20对于PC机这类通用设备来说,由于主板的设计需要兼容不同厂家的内存条,此时走线设计为等长确实是合理的设计。

图5 RGMII时序模型图

一般而言,对于SPI接口、MII接口、共享时钟的RMII接口或者SDRAM信号,走线应尽可能短。对于DDR SDRAM信号以及RGMII等DDR时序的接口来说,多数情况下,组内等长确实是一种简便快速的方法。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。