基于AD9852的地检设备信号源设计

2014-06-23高琪李明

高琪李明

(西安电子科技大学 西安 710071)

0 引言

随着微电子技术和数字集成电路的进步,直接数字频率合成(DDS)技术得到了飞速发展。由于DDS技术具有幅度和相位一致性好、频率转换时间短、频率分辨率高、稳定度好、输出相位连续可控、频带范围宽、可编程及全数字化结构等优点[1],广泛应用于现代无线通信系统、雷达和现代化仪器仪表等多个领域。而现场可编程门阵列(FPGA)具有集成度高、通用性好、设计灵活、方便编程等特点,因此可以快速地完成复杂的数字系统设计。本文采用FPGA和AD9852相结合的方式完成了地检设备信号源的设计。

1 AD9852简介

AD9852是AD公司生产的输出频率可达120MHz,频率转化速度小于1μs的直接频率合成芯片。参考时钟可单端或者双端输入,AD9852支持最高10MHz的串口或者最高100MHz并口通信(由Pin70 S/P SELECT选择),可方便的完成控制字传输。内部包含高速、高性能D/A转换器和比较器,可以实现可编程、可灵活使用的频率合成功能,当给AD9852提供精确的频率时钟源时,可输出一个频谱纯净、频率和相位都可以编程控制且稳定性良好的模拟正弦波[2],输出的正弦波也可通过其内部比较器转换成占空比可调的方波输出。AD9852主要功能特点如下[3]:

a.内部时钟最高可达300MHz;

b.包含1个12位cosine D/A和1个12位control D/A;

c.带有两个48位可编程频率寄存器和两个14位可编程相位寄存器;

d.具有12位可编程振幅调制寄存器和开关输出形键控功能;

e.内含4×到20×可编程基准时钟乘法器。可在内部产生高频时钟信号,避免了对外部高频振荡器的需要,减小了由于外频过高产生的相位噪声[2];

f.出色的动态性能:80dB SFDR(100MHz±1MHz);

g.反SINC滤波器,可对数据经过D/A转换后产生的SINC包络形畸变校正;

h.支持5种工作模式:SINGLE-TONE、FSK、RAMPED FSK、CHIRP、BPSK。

AD9852可编程频率寄存器为48位,可编程相位寄存器14位,若DDS系统时钟为fc,则DDS输出频率、相位分别为:

上式(1)中FTW为频率控制字,(2)中POW为相位控制字。

AD9852内置的比较器可以实现将DAC输出的正弦信号转换成方波,使用方式如图1所示。为滤除来自交流信号的镜像频率分量,由AD9852输出的正弦信号在输入比较器之前,需要完成重构滤波,滤波器的作用在于平滑AD9852内部输出的阶梯波[4]。当开关接通位置1时,比较器输入为差分互补的正弦信号,可输出占空比为50%的方波,当开关接通位置2时,可控DAC可由用户设置直流门限电压,实现占空比可调的方波输出。

图1 AD9852方波产生图

AD9852共有39个可编程寄存器,对AD9852的控制是通过向这些寄存器写数据实现的[5]。为使用户编程的数据从I/O缓冲区写入DDS寄存器,必须提供一个更新时钟。AD9852提供内部和外部更新两种方式:内部更新由32位计数器产生,当计数器自减为零后会产生一个内部更新信号;外部更新通过向Pin20提供一个上升沿时钟完成。两种更新模式可通过控制寄存器选择。

2 系统总体方案设计

系统结构如图2所示。外部接收由外参考驯服模块送出的10MHz信号,经过波形转换送入AD9852,内部10倍频后作为DDS系统时钟(此时系统频率分辨率为3.55×10-7Hz)。FPGA可接收上位机发来的频率控制信息完成对AD9852的配置,使AD9852输出10.23MHz正弦信号,经过外部低通滤波器滤波,送入MC12040(鉴频鉴相器)的一个参考输入端,鉴相器的另外一个输入端接收本地10.23MHz晶振中10.23MHz信号,外部构成完整的PLL,最终由晶振输出与10MHz相参的10.23MHz正弦信号。

本设计中由于对FPGA资源要求,速度性能与管脚数量要求都不是太高,因此从节约成本的角度考虑,我们选用Altera公司的CycloneⅢ系列FPGA EP3C16E144I7,出于速度上的考虑,AD9852与EP3C16E144I7之间的I/O口通讯采用并口连接。时钟信号采用双端差分输入。FPGA主要包含通信模块、AD9852接口模块。

图2 系统框图

2.1 FPGA通信模块

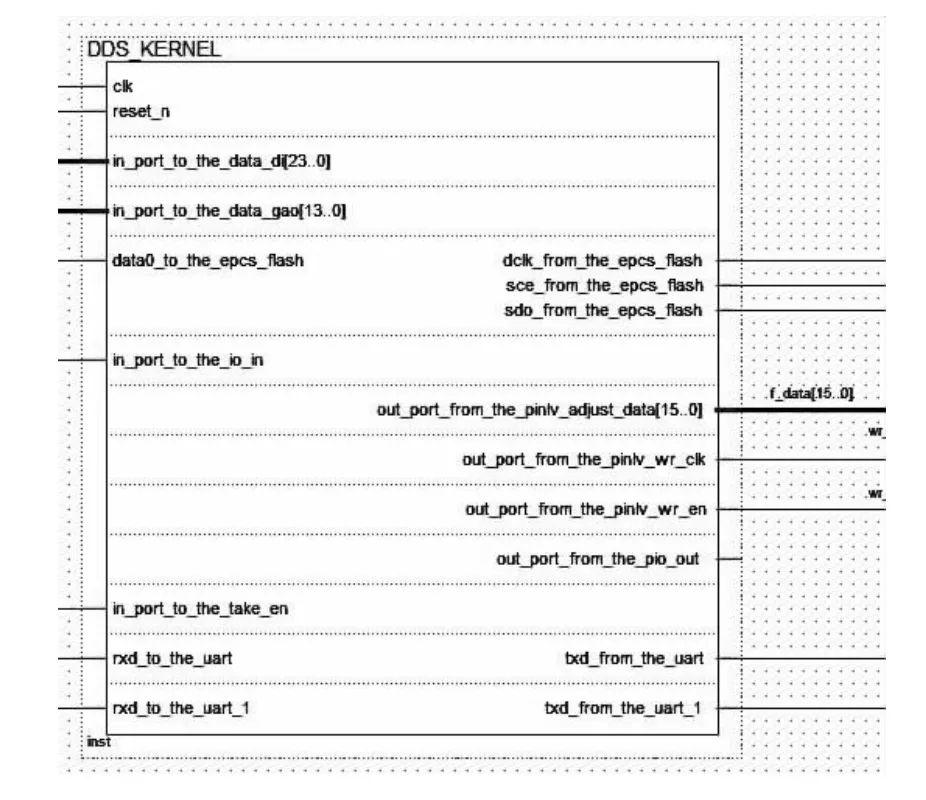

FPGA通信模块由SOPC工具设计的嵌入式NiosII软核完成,使用C语言编写,结构如图3所示。主要功能为:a.采用中断的方式接收上位机从串口RS232发送的频率和频率微调信息,按照规定协议解析,通过式(1)、(2)完成频率及相位控制字的计算,由16位数据总线发送给AD9852接口模块。b.将AD9852产生的信号与10MHz基准源的频差信息和锁定信息由串口RS232发送给上位机。

图3 FPGA通信模块

2.2 AD9852接口模块

该模块的结构如图4所示。AD9852接口模块主要操作有AD9852复位(m_res)、地址总线(addr[5..0])、数据总线(data[7..0])、写使能(wr)、数据更新(io_upd)、频率选择(FSK)。AD9852的初始化流程为:

A.上电后需要对 AD9852进行复位,使得AD9852内部所有寄存器都被设置为默认值(此时AD9852默认为内部信号更新模式)。该复位信号由m_res给出,需至少维持10个系统时钟周期的高电平。

B.接收通信模块发送的频率与相位控制字。该模块与通信模块使用异步FIFO完成控制字接收。

C.使用并行总线设置地址为1D~20的特殊功能寄存器:

a.由于需要使用内置比较器产生方波,所以需要打开比较器、I通道 DAC和数字部分,寄存器0x1D=04h;

b.参考时钟 10MHz,DDS系统时钟使用100MHz,所以倍频系数为10,设置寄存器 0x1E=0Ah;

c.设置AD9852为外部信号更新,选择工作模式为单频模式,设置寄存器0x1F=00h;

d.不使用OSK功能,为降低AD9852功耗不使用逆SINC滤波器,因此设置寄存器0x20=00h;

D.完成特殊功能寄存器设置后,内部更新计数器减到0时,寄存器的内容才更新完成。此时由于频率控制字寄存器为零,因此输出频率为零。

E.特殊功能寄存器更新后,AD9852的更新信号被设置为外部更新,使用并行传输完成频率控制字和相位控制字的写入。

F.频率与相位寄存器设置完成后,由io_upd发送一个高电平脉冲完成寄存器更新,AD9852即可按照编程方式产生预期信号。

3 电路测试结果

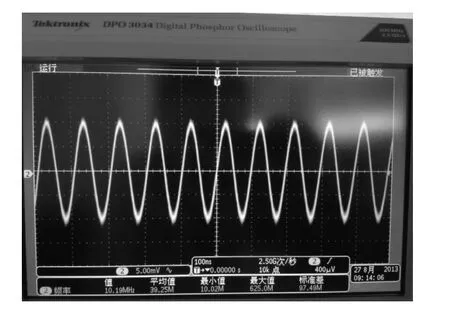

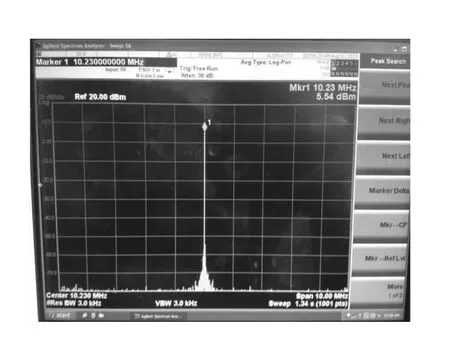

对于数字信号源来说,对产生信号的测试,既可以确认DDS是否实现了波形可变的功能,又可以分析确定DDS产生的信号是否满足设计要求。图5为信号源核心板俯视图,图6为AD9852输出正弦信号的时域图,图7为利用AD9852内部高速比较器产生的方波信号,图8、图9分别为外部高稳晶振锁定后产生的10.23MHz正弦信号的频谱图和杂散图。

图5 信号源核心板

图6 正弦信号时域图

图7 内部比较器输出方波时域图

4 结束语

本文根据AD9852性能特点,提出了一种FPGA+AD9852的信号源方案,具有结构简便、体积小、频率分辨率高、频率转换速度快、输出频谱纯净等特点。信号源的频率、幅度军均控,可以实现多种调制,满足了设备对信号源的要求。

图8 高稳晶振锁定输出正弦信号频谱

图9 高稳晶振锁定输出正弦信号杂散

[1] 郭德淳,费元春.高性能DDS芯片-AD9852的应用研究[J].电讯技术,2001,(4):52-55.

[2]李军.X波段微波倍频器的研制与一种频率源设计[D].成都:电子科技大学,2004.

[3]AD9852 datasheet,Analog Devices Inc.,2002

[4] 叶佳.基于AD9852的多功能直接数字信号合成源的研制[D].南京:南京航空航天大学,2005.

[5] 蔡磊.多路相位可控信号源[D].哈尔滨:哈尔滨工业大学,2006.