基于SOPC的高分辨率显示控制器的设计与实现

2014-06-23陶吉怀

郭 焘 陶吉怀

(电子科技大学 成都 611731)

0 引言

显示控制器在嵌入式系统中几乎必不可少,是实现图形界面的必要手段。处理器自带的显示控制器通常共用系统内存作为显存[1-2]。在显示器分辨率较高时,处理器需要管理大量的显存数据,当处理器主频较低或是系统内存的访问速率较低时,难以实现对大分辨率的显示器的驱动[2]。一种解决的方法配备专用集成芯片设计的显示控制器[3],但是这种方法一般需要显示控制器和显示器配套定制,缺乏灵活性,而且成本较高。

SOPC[4]是一种特殊的片上系统,建立在可编程逻辑技术的基础上,尽可能将一个大而完整的电子系统实现在一块FPGA硅片上,具有硬件可裁剪、可扩充、可升级,软件在系统可编程的特点,使得设计的系统在规模、功能、体积、性能、上市周期、开发成本等方面有着很大的优势。本文基于SOPC技术提出一种显示控制器的设计与实现方案,使得在处理器主频不是很高的情况下即可实现对高分辨率的LCD显示器的驱动。

1 方案设计

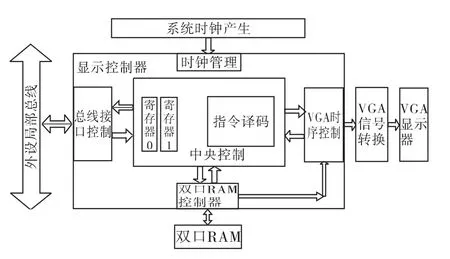

以 xilinx 的 microblaze[5]软核处理器为例,显示控制器和处理器的连接如图1所示。显示控制器通过处理器外设局部总线接口连接到基于SOPC的处理器上,作为处理器的一个外设。本设计提出两种显示控制器架构,第一种架构如图2所示,第二种架构如图3所示。通过在显示控制器内部设置处理器可以读写的寄存器,实现处理器对显示控制器的命令传达和数据传输。显示控制器内部逻辑全部通过FPGA硬件实现,包括指令获取和译码、显存数据处理处理、RAM的读写操作、VGA时序产生等。RAM控制器根据显示器上点的坐标位置将显存数据写入RAM中相应的位置,并根据VGA时序产生模块的读取请求,从相应位置读出显存数据。VGA时序控制模块产生行同步和场同步信号,并根据行同步、场同步的信息,将显存数据送到VGA接口,实现图像的显示。

本设计中,第一种架构使用单口的SDRAM作为图像数据存储器,这种架构的缺点是要求SDRAM读写数据的速率至少是VGA接口图像数据速率的两倍以上,当显示器的分辨率和刷新频率较高时,对SDRAM的读写速率要求较高。第二种架构采用双口RAM来存储显存数据,这种架构的优点是显存数据的读写可以同时进行,RAM的写数据速率只要达到VGA接口的图像数据速率即可,降低了对系统时钟的要求。

图1 显示控制器与处理器的连接

图2 基于单口RAM显示控制器架构

1.1 接口设计

显示控制器对外的接口包括:外设局部总线接口、VGA信号转换接口、RAM存储器控制接口以及时钟输入接口。

图3 基于双口RAM的显示控制器架构

外设局部总线接口由SOPC的硬件开发平台提供。以Xilinx的SOPC硬件开发环境XPS(Xilinx Platform Studio)[6]为例,XPS 为用户提供了 PLB v4.6、Fast Simple Link、AXI4-Lite等 5 种处理器总线接口,用户可以选择其中的一种接口作为自己的外设和总线的接口。

VGA信号转换接口用于将数字信号转换为VGA接口所需的模拟信号,该接口的定义如图4所示,其中,vsync是场同步信号,hsync是行同步信号,R、G、B分别为红基色分量、绿基色分量和蓝基色分量。RGB的总位宽通常有8位、16位、24位和32位几种,本设计以8位位宽为例进行设计。

图4 VGA时序控制模块对外接口

RAM存储器控制接口由RAM的类型决定,通过该接口对RAM进行显存数据的读写操作。

时钟输入接口主要是为了获取内部硬件逻辑所需要的时钟,本设计的显示控制器内部主要有两种时钟,一种是和系统处理器总线一致的时钟,一种是VGA时序产生所需要的时钟。

显示控制器内部的接口主要包括:中央控制模块和总线接口控制模块间的接口,中央控制模块和VGA时序控制模块间的接口,中央控制模块和RAM控制器的接口。

总线接口控制模块由系统产生,它为用户提供了一个用户接口,该接口由用户逻辑中使用的总线资源决定。当用户逻辑中使用可以被处理器访问的寄存器时,接口定义如图5所示,其中,Bus2IP_Clk为时钟信号,Bus2IP_Reset为对IP模块的复位信号,其余的信号线用于读写用户逻辑中可被处理器访问的寄存器。

图5 总线接口控制模块和中央控制模块间的接口

中央控制模块和VGA时序产生模块间的接口如图6所示,其中,en为对VGA时序产生模块的使能信号,valid信号指示当前VGA时序产生模块产生的X轴坐标X_label和Y轴坐标Y_label是否有效,X_label和Y_label用于指示VGA时序产生模块当前请求的是显示器哪个位置的RGB值。

图6 中央控制模块和VGA时序产生模块间的接口

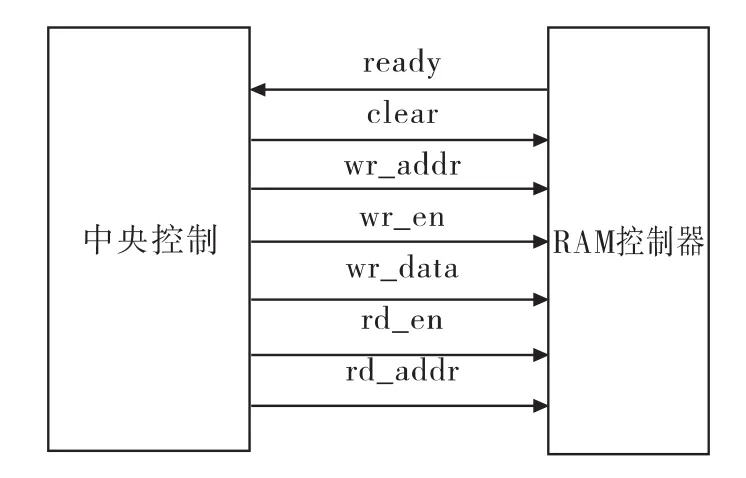

中央控制器和RAM控制器间的接口视RAM的类型而定,当采用单口的SDRAM时,写入和读出的显存数据需要FIFO缓存,当采用双口RAM时,不需FIFO缓存。以双口RAM为例,中央控制器和双口RAM控制器的接口如图7所示,其中,ready用于指示RAM目前是否处于就绪状态,clear为清除RAM命令,wr_en为写 RAM使能,wr_addr为写RAM的地址,wr_data为写RAM的数据,rd_en为读使能,rd_addr为读RAM的地址。

1.2 VGA时序

VGA接口时序[7]如图8所示(其中vd_en是为了说明视频信号vd何时有效而添加的信号,它本身不属于VGA接口的信号)。VGA接口时序中场同步信号决定了每帧图像的开始和结束,行同步信号和场同步信号共同决定扫描到的点在显示器上的位置。视频信号vd由RGB值经过数模转换得到,决定扫描到的点的彩色值。

图7 中央控制模块和RAM控制器间的接口

图8 VGA时序

以分辨率为1024×768、刷新频率为70Hz的图像格式为例,其点时钟clk为75MHz,行同步频率为56.4759kHz。

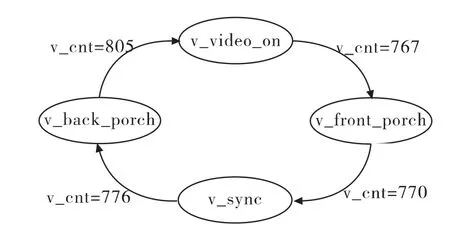

场同步信号 vsync的周期 t_vsync约为14.27ms,每场有806行,其中768行为有效显示行,38行为场消隐期。场同步信号vsync每场有一个脉冲,该脉冲的低电平宽度t_vs为106.24μs。场消隐期包括场消隐前肩t_vfp(3行)、场同步时间t_vs(6行)和场消隐后肩t_vbp(29行),共38行。

行同步信号 hsync的周期 t_hsync约为17.71μs,每行包括1328点,其中1024点为有效显示区,304点为行消隐期(非显示区)。行同步信号hsync每行有一个脉冲,该脉冲的低电平宽度t_hs为1.813μs。行消隐期包括行消隐前肩t_hfp(24个clk)、行同步时间t_hs(136个clk)和行消隐后肩t_hbp(144个clk),共304个点时钟。

行同步和场同步信号分别通过行同步、场同步状态机产生。行、场同步状态机通过行计数器h_cnt和场计数器v_cnt来进行状态转换。行同步状态机如图9所示,场同步状态机如图10所示。行计数器的触发信号为时钟clk,每来一个时钟,行计数h_cnt加1,当达到最大值1327时归零。场计数的触发为h_cnt,当 h_cnt=1327 时,场计数 v_cnt加 1,当 v_cnt=805且h_cnt=1327时v_cnt归零。在行同步计数周期内,当vd_en有效时,在每个时钟上升沿,将相应点的视频信号vd送到VGA接口。

图9 行同步状态机

图10 场同步状态机

1.3 寄存器设置

显示控制器内部设置了两个处理器可以访问的32位的寄存器,一个定义为控制寄存器CTRL[31:0],一个定义为数据寄存器DATA[31:0]。控制寄存器各比特位的定义如下:

CTRL[31]:显示控制器使能,高电平有效;

CTRL[30]:显存数据写使能,高电平有效;

CTRL[29]:显存数据读使能,高电平有效;

CTRL[28:21]:设置显示器分辨率模式;

CTRL[20:17]:设置显示器刷新频率模式;

CTRL[16]:清除显存数据,高电平有效;

CTRL[15]:指示当前数据寄存器值是否有效;

CTRL[14:0]:保留。

数据寄存器各比特位的定义如下:

DATA[31:30]:保留;

DATA[29:19]:对应显示器上的点的横坐标;

DATA[18:8]:对应显示器上的点的纵坐标;

DATA[7:0]:坐标为(DATA[29:19],DATA[18:8])的点的RGB彩色值。

2 方案验证

利用Xilinx的XPS开发环境搭建microblaze软核处理器硬件平台,将本文设计的显示控制器作为一个设备挂载到microblaze处理器的外设局部总线上[5-6]。利用Xilinx的SDK[6]开发环境为生成硬件平台的驱动程序,利用此驱动程序,在VGA接口的LCD显示器上绘制图像。为了实现动态的图像效果,实验中在显示器上动态地画圈,画圈的结果如图11所示。

图11 在显示器上动态画圆圈

实验结果表明,在150MHz的处理器频率下,实现在分辨率为1280×1024、刷新频率为60Hz的LCD显示器绘制动态图像,没有出现卡壳现象。

3 结论

本设计以 VGA接口为例,通过在 Xilinx的Spartan-6系列的FPGA上实验,在主频相对较低的软核处理器上实现了大屏幕显示器的驱动,说明了方案的可行性。本文设计的显示控制器不局限于SOPC,可应用于基于ASIC的系统中,针对不同的处理器,只需稍微修改总线接口控制逻辑即可,设计灵活,具有通用性。

[1] 杜春雷.ARM体系结构与编程[M].-北京:清华大学出版社,2003.

[2]丁铁夫,陈伟,郑喜凤等.多媒体协处理器SM501在全彩LED显示屏脱机播放系统的应用[J].液晶与显示,2009,24(6):860-865.

[3]王立风.多媒体协处理器SM501在嵌入式系统中的应用[J].单片机与嵌入式系统应用,2006,(6):42-43.

[4] 江国强.SOPC技术与应用[M].北京:机械工业出版社,2006.

[5]Xilinx Company.MicroBlaze Processor Reference Guide v13.2[EB/OL].[2011-7-6].http://www.xilinx.com.

[6]Xilinx Company.Embedded System Tools Reference Manual v13.2[EB/OL].[2011-7-6].http://www.xilinx.com.

[7] 曹允.基于FPGA的VGA时序彩条信号实现方法及其应用[J].电子工程师,2002 28(7):42-45.