一种小型化超宽带功率放大器的设计

2014-06-07安士全郭本青

安士全,郭本青,张 瑞

(1.中国电子科技集团公司第38研究所,合肥 230031;2.电子科技大学通信与信息工程学院,成都 610054)

一种小型化超宽带功率放大器的设计

安士全1,郭本青2,张 瑞1

(1.中国电子科技集团公司第38研究所,合肥 230031;2.电子科技大学通信与信息工程学院,成都 610054)

针对超宽带(0.6 GHz~2.2 GHz)高效率功率放大器的设计要求,选用CREE公司GaN器件CGH40045,在ADS仿真软件中采用Load+Pull技术确定最佳输入输出阻抗,利用基于集总元件和微带线分布参数元件的方法进行输入输出阻抗的宽带匹配。设计完成后,对电路进行了测试,测试结果表明,在输入为34 dBm,工作电压为28 V时,0.6 GHz~2.2 GHz频率范围内漏极效率优于50%,输出功率高于45 dBm,带内增益波动小于1.2 dB,验证了此方法的有效性。

功率放大器;宽带;高效率;负载牵引

0 引 言

微波功率放大器在雷达、通信、导航、卫星、电子对抗设备等系统中有着广泛的应用。随着科技的发展,对这些电子系统的性能要求不断提高。作为电子设备的关键元件之一,功率放大器直接影响着包括工作带宽在内的整个射频系统的性能指标。因此,小型化宽带高效放大器的设计一直是微波功率放大器的研究热点[1-2]。

设计了一种基于负载牵引技术的混合匹配网络的宽带高效功率放大器。

1 设计方法

微波功率放大器的输入输出阻抗等许多参数与频率相关,很大程度地限制了其频带宽度。尤其在较高频率时,它的内部反馈及寄生参量影响很大,晶体管特性会在较宽的频率范围内有较大变化,通过负载牵引法得到的高效率最佳源阻抗与负载阻抗也会随频率变化。实现宽带高效功放的一种最直接思路是设计出的匹配网络所呈现的阻抗能够顺应这种变化趋势,以得到每个频点的最高效率[3-6];然而满足相应要求的匹配网络一般难于实现。另一种思路则是选择一组源阻抗与负载阻抗值作为实现宽带高效的最佳匹配点,使在这组阻抗条件下,功放在所关注的频段内均达到较高效率。这样,设计难点就转化为宽带匹配网络的实现,即设计的输入输出网络在工作带宽内均要表现出最佳匹配点的值[7-8]。

1.1 最佳输入输出阻抗的选择

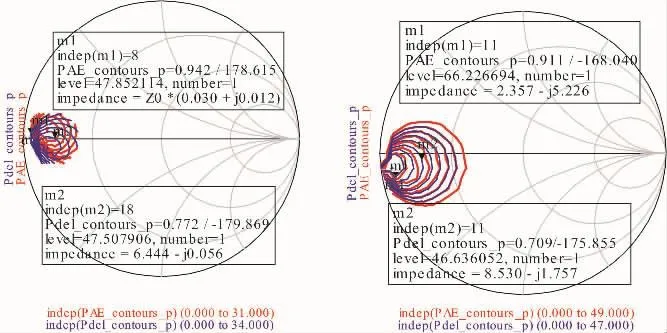

设计0.6 GHz~2.2 GHz高效率功放的第一步就是找到最佳源阻抗与负载阻抗。基于CREE公司提供的GaN HEMT CGH40045大信号模型,在ADS环境中进行源牵引与负载牵引,在整个频段内选择0.6,1.0,1.4,1.8,2.2 GHz进行源牵引与负载牵引,通过多次迭代找到最佳的输入输出阻抗,并用曲线标示出其在整个带宽内的变化趋势。根据宽带匹配电路保高放低的原则,选择靠近这条曲线中段偏高频的某点作为最佳负载匹配点能够在0.6 GH~2.2 GHz内较好地达到效率、带宽折中的目的。另外,最佳负载匹配点也应使得工作带宽内的最佳源阻抗相对集中,最终选定在1.8 GHz处的最佳负载阻抗6.5Ω和源阻抗(5-j*2Ω),分别如图1所示。

图1 1.8 GHz时负载牵引(左)与源牵引(右)下的功率效率曲线

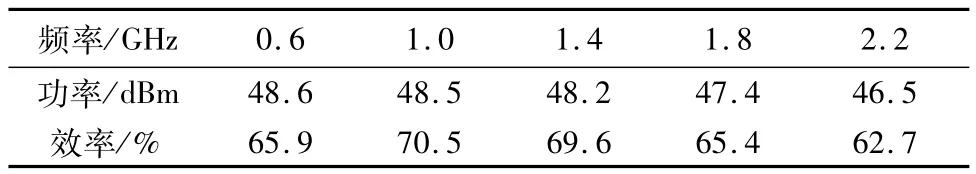

在选定的负载和源阻抗进行功率和效率的仿真测试,分别给出了设定为最佳匹配点时功放在0.6 GH~2.2 GHz范围内几个频点的功率附加效率及输出功率,见表1。由数据可见该阻抗是比较理想的。

表1 最佳负载/源阻抗下频带内5个频点的功率和效率仿真值

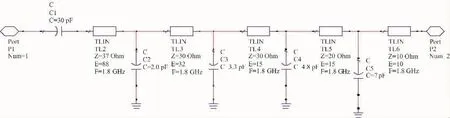

1.2 匹配电路设计

在微波功率放大器的匹配电路设计中可以选择集总元件,也可以选择分布参数的微带线。一般而言,集总元件在S波段及S波段以下频段较为常见,随着频率的升高,集总元件的寄生参量将使其特性发生很大变化。因此,在S波段以上频段多采用分布参数匹配。为了充分发挥集总和分布元件各自的优势,本电路采用二者混合的方式进行匹配[9-10]。

利用ADS中的smith chart工具可以很方便的进行集总元件与微带的混合匹配设计,低阻的微带实现实部阻抗匹配,并联电容实现消除复阻抗的虚部。为保证电路的宽带性能,匹配电路需要多级匹配以保证低Q值,利用圆图工具进行的输入匹配和生成的理想器件电路,如图2所示。

图2 利用sm ith chart进行输入阻抗匹配及生成的理想器件电路示意图

1.3 整体电路优化

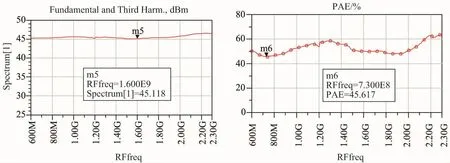

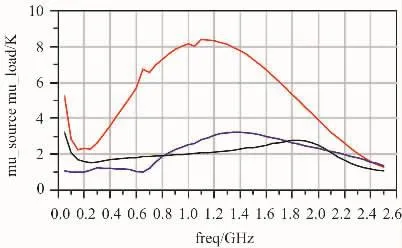

在对输入输出电路匹配好后需要进行整体仿真,综合考虑功率放大器的功率、效率、稳定性等,对电路进行微调。利用谐波仿真器对电路进行整体仿真的结果如图4所示,在输入33 dBm时,0.6~2.2 GHz频带内增益起伏小于1.2 dB,输出功率大于30 W,功率附加效率大于45%,稳定性测试显示电路处于绝对稳定状态。仿真结果满足指标要求。

图3 整体仿真电路图

图4 输出功率(左)与附加效率(右)随频率的仿真结果

2 测试结果与分析

在完成电路的ADS仿真,进行投产加工并进行测试。考虑到小型化和加工精度的要求,介质板材选用Rogers公司的RT6006,介电常数为6.15,厚度0.635 mm。电路的实物图,如图6所示,实际电路尺寸55 mm×30 mm。

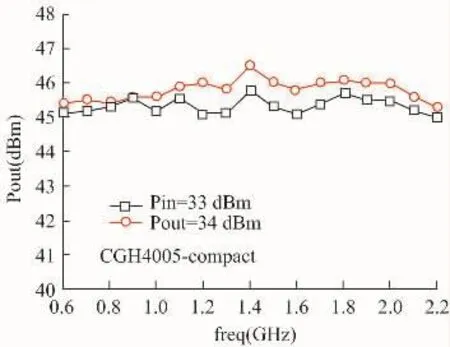

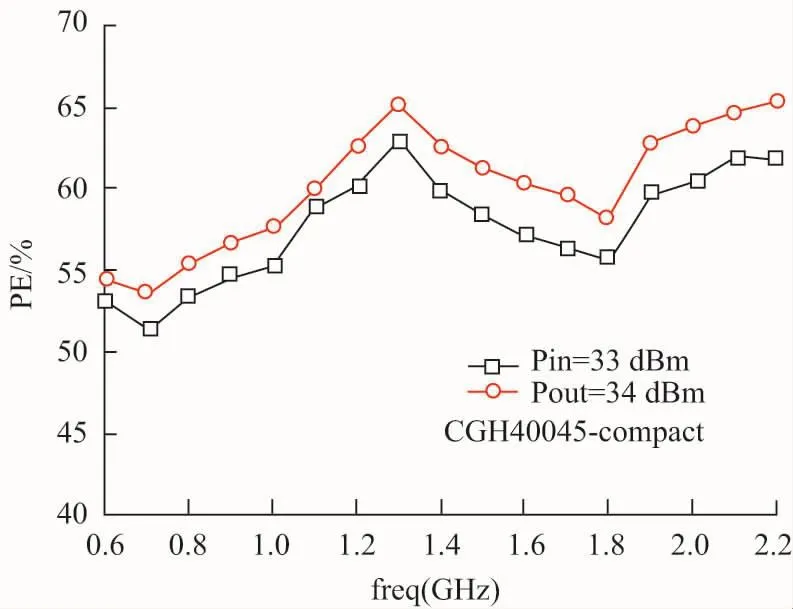

在漏压28 V,栅压-2.3 V,静态电流100 mA状态下,对电路进行了简单的调试,由于输入功率33 dBm还没有完全饱和,因此对输入功率33 dBm和34 dBm分别对功率放大器进行了测试,如图7是在0.6~2.2 GHz的频率范围内输出功率随输入功率的曲线,整个频段内输出功率都在45 dBm以上,增益大于11 dB。图8是经计算各频点的漏极效率曲线,由图可以看出,输入功率34 dBm时,在0.6~2.2 GHz的设计频段内漏极效率大于50%,满足指标需求。

图5 稳定性仿真结果

图6 小型化宽带高效功率放大器实物图

图7 输出功率曲线

图8 漏极效率与频率间的曲线

3 结 语

设计了一款小型化超宽带功率放大器,经测试在0.6~2.2 GHz频带内输出功率大于30 W,起伏小于1.2 dB,漏极效率大于50%,电路尺寸55 mm× 30 mm。该功率放大器可用于雷达、电子对抗等系统中用作宽带高效放大器。

[1]董磊,何松柏,雷奇.基于带通匹配网络理论的宽带高效率功放设计[J].信息与电子工程,2011,9(4):449+452.

[2]ÅDAHL A,ZIRATH H.A 1 GHz Class+E LDMOSPower Amplifier[C]//Proc.33rd Eur.Microw.Conf.,2003,1:285+288.

[3]ZIRATH H,RUTLEDGE D B.An LDMOSVHF Class+E Power Amplifier Using a High+Q Novel Variable Inductor[J].IEEE Trans.Microw.Theory Tech.,1999,47(12):2534+2538.

[4]MADER T B,POPOVIC Z B.The Transmission Line High+Efficiency Class+E Amplifier[J].IEEE Microw. Guided Wave Lett.,1995,5(9):290+292.

[5]XU H,GAO S,HEIKMAN S,et al.A High+Efficiency Class+EGaN HEMT Power Amplifier[J].IEEEMicrow. Wireless Compon.Lett.,2006,16(1):22+24..

[6]KEE S,et al.The Class+E/F Family of ZVS Switching Amplifiers[J].IEEE Trans.Microwave Theory Tech.,2003,51(6):1677+1690.

[7]THOMASH LEE.CMOS射频集成电路设计[M].北京:电子工业出版社,2004.

[8]中国集成电路大全编委会.微波集成电路[M].北京:国防工业出版社,1972.

[9]曹韬,曾荣.基于GaN HEMT器件的宽带高效功率放大器[J].微波学报,2012,28(6):76+79.

[10]宫为保.宽带射频功率放大器的匹配电路设计[J].广播电视信息,2010(9):66+68.

安士全(1977—),山东新泰人,高级工程师,研究方向为射频前端;

E+mail:anshiquan@126.com;

郭本青(1977—),河南新乡人,电子科技大学通信与信息工程学院特聘副研究员,研究方向为射频模拟集成电路;

张 瑞(1977—),高级工程师,研究方向为射频前端。

Design of a M iniature Ultra W ideband Power Am plifier

AN Shi+quan1,GUO Ben+qing2,ZHANG Rui1

(1.The 38th Research Institute of CETC,Anhui Hefei230031,China;2.School of Communication&Information Engineering,University of Electronic Science and Technology of China,Chengdu 610054,China)

Concerning the design goal of a highly efficient power amplifier working across 0.6 GHz~2.2 GHz,the GaN transistor CGH40045 of CREE Company is selected.The optimal input and output impedance is calculated with the help of Load+Pull technology in software ADS,realizing broadband matching with integrative devices and distributed components.Simulation is performed and produced based on themethodology.Themeasurement results indicate thatwithin 0.6 GHz~2.2 GHz,Drain Effi+ ciency excels 50%,Delivered Power is higher than 45 dBm and Gain Ripple is less than 1.2 dB as the drain bias and power drive sets to 28 V and 34 dBm respectively.These research datawell verified the ef+ fectiveness of themethodology.

power amplifier;broadband;high efficiency;load+pull

TG722.1

:A

:1673+5692(2014)06+639+04

10.3969/j.issn.1673+5692.2014.06.017

2014+09+18

2014+09+26