一种基于时序型硬件木马的IP版权保护结构

2014-06-06冯紫竹赵毅强刘长龙

冯紫竹,赵毅强,刘长龙

(1.天津大学电子信息工程学院,天津300072;2.中国电子科技集团公司第五十四研究所,石家庄050081)

一种基于时序型硬件木马的IP版权保护结构

冯紫竹1,赵毅强1,刘长龙2

(1.天津大学电子信息工程学院,天津300072;2.中国电子科技集团公司第五十四研究所,石家庄050081)

随着IP核在SoC设计中的大量使用,其版权问题得到广泛关注,通过植入硬件木马实现IP核的版权保护是一个新的研究方向。针对其中植入木马激活时间短的问题,提出一种改进结构,使IP核评估版本满足有效期长度的要求。将时序型硬件木马植入原始电路状态机的冗余状态中,选取电路中部分节点构成的序列作为木马状态的转移条件,木马激活后影响电路的正常功能,使IP核的使用受到限制。仿真结果表明,通过合理调整状态数量及序列长度,能够在优化电路面积的同时有效延长木马的激活时间,当状态数为3、序列长度为4时,该方法能够在电路面积减少0.123%的基础上使激活时间提高约120倍。

IP核;硬件木马;激活时间;有效期;状态机

1 概述

为缩短集成电路设计周期,降低制造成本,许多IC设计公司使用第三方IP核进行产品设计[1]。在购买IP版权之前,通常IP开发商会为设计者提供一个评估版本来完成功能验证,这会增加IP在未经授权情况下被非法使用的风险[2]。因此,在用于评估的IP核中通常会加入一些版权保护技术,常用方法主要有2种:(1)采用数字水印技术,即在IP核中插入一个很难移除的数字标记。当涉及侵权问题时,数字水印可以表明版权归属[3-4]。这是一种被动的保护技术,并不影响IP核被非法使用时的功能[5]。(2)在IP核中采用加密保护技术,只有通过特定平台才能实现IP的仿真与综合;通过提供IP核的功能模型实现仿真和验证,但网表和版图并不交付用户。采用这种方法不能测试IP集成在芯片中的面积、功耗等信息以及与芯片中其他模块的兼容性,具有一定局限性。

使用硬件木马保护IP核的评估版本是IP核保护技术的一个新的发展方向[6],由于硬件木马是潜伏在电路中的微小单元,并且对电路面积和功耗都影响很小,因此木马在激活前不会影响IP核的正常功能[7-8]。通过在IP核中植入一段基于有限状态机(Finite State Machine,FSM)的时序型硬件木马,利用电路中的低翻转概率节点作为木马的激活条件,节点翻转到指定值时木马激活使 IP核的功能受限[6]。这种方法类似于给 IP核限定了一段“有效期”,IC设计者在有效期过后需要付费得到一个使木马失效的序列才能继续使用。在IP核中植入基于有限状态机的硬件木马,需要在电路中找到翻转概率足够低的节点,作为木马状态的触发条件。但在一些电路中可能不存在翻转概率足够低的节点,例如一个AES算法电路,平均翻转概率最低的节点在2 000多个时钟内翻转一次,而执行一次AES加密运算需要300多个时钟周期,因此在木马激活前电路平均只能进行7次正确运算,这对于评估一个IP核的性能显然是不够的。

本文对在IP核中植入硬件木马的方法进行改进,将电路中的多个节点组成一个序列,指定一组序列值作为木马的激活条件,以降低木马的激活概率,且硬件木马将不再作为一个独立的状态机植入IP核中,而是复用原始电路中某个状态机的冗余状态。

2 时序型硬件木马

硬件木马从电路结构上可以分为组合型和时序型2种[9],组合型硬件木马是指木马电路完全由组合逻辑组成;时序型硬件木马是指木马电路中包含寄存器等时序电路,时序型硬件木马不同于组合型硬件木马,其触发结构不一定依赖于外部触发信号,可以由木马内部的计数器等结构直接触发[10]。一般来说,随着触发序列长度的增加,时序型硬件木马要比组合型硬件木马更难检测[11]。

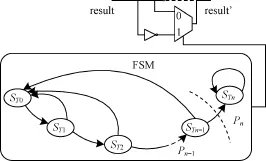

一种典型的时序型硬件木马使用有限状态机(FSM)产生触发条件,状态机的状态只能在一些极少满足的条件下才会发生跳变并使木马激活[12]。图1是基于FSM的时序型硬件木马,result是原始电路中的某个节点,将该节点与取反后的值作为多路选择器的输入信号,输出信号result'取代result信号接回原始电路中。从ST0到STn-1是电路正常工作时FSM的状态,STn是木马的激活状态,Pi为状态机的状态转移条件,这些状态转移条件都是电路中一些翻转概率较低的节点,也就是说,木马被激活的概率是一个很小的值,这个值由电路中某些选定节点的翻转概率来决定。

图1 基于FSM的时序硬件木马结构

3 基于FSM的硬件木马改进结构

第2节中提到的方法将硬件木马作为一个独立的状态机植入电路中,但植入一个新的状态机会增加电路的面积和功耗;而且该方法假定电路中存在一些极难满足的状态转移条件Pi,但在一些时钟频率较高的电路中可能不存在满足要求的低翻转概率节点,硬件木马的激活时间不能达到设计要求。为延长激活周期,需要增加木马状态机的状态数,就会带来更大的电路面积开销,并使木马的可检测性增强。

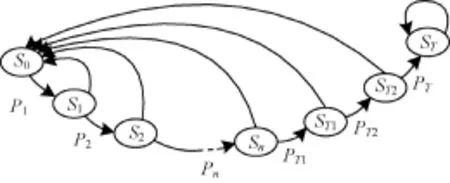

为减小因插入硬件木马而带来的面积开销并降低木马的可检测性,本设计对原始方法进行改进,利用原始电路状态机的冗余状态取代插入新的状态机来构造木马电路。如图2是一个包含n+3个状态的FSM,其中,ST1,ST2和ST是这个FSM中的3个冗余状态,这些没有被用到的状态被用来组建时序型硬件木马。由于硬件木马只改变了下一状态逻辑,因此这种同原始电路共享时序单元的优势可以缩小硬件木马对电路面积和功耗的影响,从而躲避传统木马检测技术的检测。此外,通过复用原始电路中的组合逻辑可以进一步减少面积开销。当电路中不存在低翻转概率节点时,为延长硬件木马的激活周期,满足IP核试用期的时间要求,通过选取电路中的多个节点构造一个序列作为木马状态的转移条件。

图2 利用冗余状态的硬件木马状态转移图

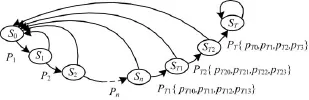

如图3所示,状态S0到Sn为原始状态机正常工作时的状态,状态ST1,ST2和ST为状态机的3个冗余状态。设计中使用的硬件木马电路复用原始状态机中的3个冗余状态,其中,ST为木马的激活状态。选取电路中4个节点构成一段序列,并指定3组序列值作为这3个冗余状态的转移条件,即图3中的PT1{pT10,pT11,pT12,pT13},PT2{pT20,pT21,pT22,pT23}和PT{pT0,pT1,pT2,pT3}。电路在运行中依次满足PT1,PT2和PT时,状态机从Sn状态顺序经过ST1和ST2,跳到ST状态,使木马激活。否则,状态机将返回初始状态。原始状态机每执行一次才会对硬件木马的状态转移条件判断一次,并且可以通过改变冗余状态的数量和状态转移条件中的节点数来调整木马的激活时间。

图3 使用序列作为转移条件的硬件木马状态转移

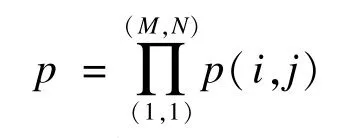

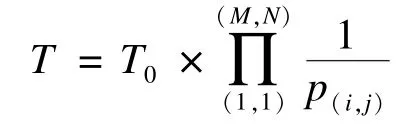

对木马的激活时间进行理论计算,假定选取原始状态机中的M个冗余状态S1,S2,…,SM植入木马电路,每个冗余状态使用电路中的N个节点T1,T2,…,Tn构成一段序列,每个节点翻转到指定值的概率为p(i,j)(i=1,2,…,M,j=1,2,…,N)。木马激活一次的概率理论上为:

若在电路的一个工作周期T0内,植入木马的状态机只执行一次,则木马激活一次的时间为:

采用原始方法植入硬件木马,木马的状态数与电路中节点数同为N,节点翻转到指定值的概率为pi(i=1,2,…,N),由于木马植入一个独立的状态机中,每个时钟周期都要进行状态转移条件的判断,木马激活一次的时间为:

比较使用2种不同方法得到的木马激活时间可知,原始方法中硬件木马激活时间的计算以电路的时钟周期Tclk为基础,而改进方法中以整个电路的一个工作周期T0(T0≫Tclk)为基础。因此,节点的翻转概率pi不需要太低就可以使木马有足够长的激活时间;同时可以根据需要改变M和N的值来调节木马的激活时间以及电路面积的增加。

4 实验结果与分析

本文设计了一个AES加/解密算法电路,使用NOVAS公司的verdi软件对电路中的所有节点在执行约2万个时钟周期(70次加/解密运算)后的翻转概率进行统计,在全部节点中,翻转概率最低的寄存器在2万个周期内也翻转了10次,即平均每执行7次加/解密运算木马就要被激活1次,这对于评估一个IP显然是不够的。

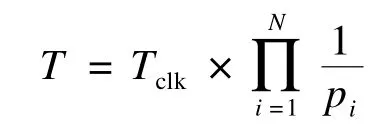

对木马的激活条件进行改进,将硬件木马电路植入AES加/解密算法电路的一个有限状态机中,选取电路中的节点构造一个序列,并设定几组序列值作为木马状态的转移条件。图4为电路执行加/解密运算的仿真结果。

图4 AES加/解密算法电路的仿真波形

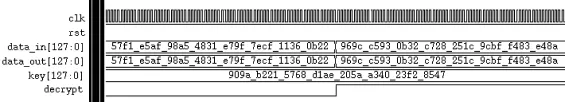

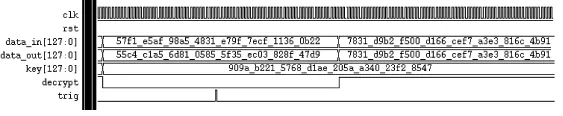

对植入硬件木马的电路进行仿真分析,在key信号和data_in信号的输入端注入大量的随机值。在执行5×107个时钟周期后对木马的激活次数进行统计。图5为AES加/解密算法电路中木马激活一次的仿真波形。与图4进行对比,可以看出,在执行数据解密运算时,木马被激活(trig= 1),输出与加密前的信号值不同,解密后的值出现错误。

图5 木马被激活时的仿真波形

统计结果显示,若在电路中选取4个节点插入控制轮密钥加状态机的3个冗余状态中,则在5× 106个时钟周期内,木马一共激活5次,平均激活一次需要约106个时钟周期,而执行一次AES加/解密运算需要333个时钟周期,因此电路在木马激活之前已经能够进行约3 000次正确运算。另外,根据电路的不同功能,可以通过调整序列长度来改变木马的激活时间。

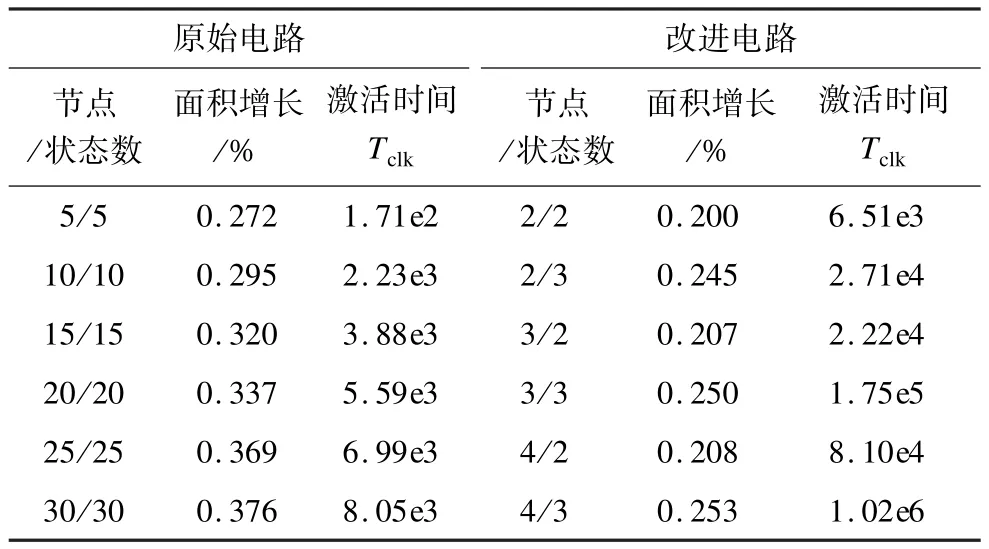

分别使用原始方法和改进方法在AES加/解密运算电路中植入木马电路,其中原始方法是将木马作为一个独立的状态机植入电路中,且每个状态选取电路中翻转概率相对低的节点作为激活条件;改进方法将木马植入原始电路状态机的冗余状态中,并采用多个节点组成的序列作为木马状态的激活条件,对2种方法进行仿真验证,其电路特性如表1所示。可以看出,使用改进的方法在电路面积上有很大优化,并且激活时间成倍增加。例如改进方法中节点数为4、状态数为3时,电路面积增长比原始方法中使用30个节点时要小0.123%,但激活时间却是原始方法的120倍以上。而且由于使用节点数、状态数都很少,其隐蔽性也比使用原始方法好。

表1 使用2种方法激活木马的电路特性对比

5 结束语

硬件木马的出现给信息安全问题带来了新的挑战,芯片中一旦被植入硬件木马,将会给安全性要求较高的应用(诸如通信和国家基础设施等)带来巨大威胁,但通过合理利用硬件木马的特性,可以实现电路的自我保护功能。本文针对基于FSM的时序型硬件木马开展研究,通过对硬件木马的激活方式进行改进,并将其植入电路中,既能达到IP版权保护的作用,又能放宽对IC设计者的使用限制,具有实际而广泛的应用价值。后期将继续对该设计进行流片及测试工作,将木马的实际激活时间与仿真时得到的数据进行比对,进一步验证该方法的有效性。

[1] Tehranipoor M,Koushanfar F.A Survey of Hardware Trojan Taxonomy and Detection[J].IEEE Design& Test of Computers,2010,27(1):10-25.

[2] Karri R,Rajendran J,Rosenfeld K,et al.Trustworthy Hardware:Identifying and Classifying Hardware Trojans [J].Computer,2010,43(10):39-46.

[3] Torunoglu I,Charbon E.Watermarking-based Copyright Protection of Sequential Functions[J].IEEE Journal of Solid-state Circuits,2000,35(3):434-440.

[4] Oliveira A L.Techniques for the Creation of Digital Watermarks in Sequential Circuit Designs[J].IEEE Transactions on Computer-aided Design of Integrated Circuits and Systems,2001,20(9):1101-1117.

[5] Fan Yucheng,Tsao Henwai.Watermarking for Intellectual Property Protection[J].IEEE Electronics Letters, 2003,39(18):1316-1318.

[6] Narasimhan S,Chakraborty R S,Bhunia S.Hardware IP Protection During Evaluation Using Embedded Sequential Trojan[J].IEEE Design&Test of Computers,2012, 29(3):70-79.

[7] 绉 程,张 鹏,邓高明,等.基于功率旁路泄露的硬件木马设计[J].计算机工程,2011,37(11):135-137.

[8] Rad R,Plusquellic J,Tehranipoor M.A Sensitivity Analysis of Power Signal Methods for Detecting Hardware Trojans Under Real Process and Environmental Conditions[J].IEEE Transactions on Very Large Scale Integration Systems,2010,18(12):1735-1744.

[9] Chakraborty R S,S,Narasimhan S,Bhunia S.Hardware Trojan:Threats and Emerging Solutions[C]//Proc.of IEEE International High Level Design Validation and Test Workshop.San Francisco,USA:IEEE Computer Society,2009:166-171.

[10] Liu Huafeng,Luo Hongwei,Wang Liwei.Design of Hardware Trojan Horse Based on Counter[C]//Proc.of International Conference on Quality,Reliability,Risk, Maintenance,and Safety Engineering.Xi'an,China: [s.n.],2011:1007-1009.

[11] Salmani H,Tehranipoor M,Plusquellic J.A Novel Technique for Improving Hardware Trojan Detection and Reducing Trojan Activation Time[J].IEEE Transactions on Very Large Scale Integration Systems,2012,20(1): 112-125.

[12] Wang Xinmu,Narasimhan S,Krishna A,et al.Sequential HardwareTrojan:Side-channelAware Design and Placement[C]//Proc.of the 29th IEEE International Conferenceon ComputerDesign.Amherst,USA: [s.n.],2011:297-300.

编辑 任吉慧

A Sequential Hardware Trojan-based Framework for IP Copyright Protection

FENG Zi-zhu1,ZHAO Yi-qiang1,LIU Chang-long2

(1.School of Electronic Information Engineering,Tianjin University,Tianjin 300072,China;

2.The 54th Research Institute of China Electronics Technology Group Corporation,Shijiazhuang 050081,China)

With the widespread use of Intellectual Property(IP)in System-on-Chip(SoC)design,protection of hardware IP cores against piracy during evaluation becomes a major concern.Embedding a sequential hardware Trojan inside an IP is a new solution to protect the evaluation version of hardware IP.This paper proposes an advanced framework to lengthen the Trojan's activation time which is the decisive factor of the expiry date of an IP.The sequential Trojan is inserted in the unused states of a Finite State Machine(FSM)in the target circuit and some rare nodes making up a sequence can be chosen as Trojan trigger conditions,and the normal function of the IP core is disturbed when the Trojan is activated.Simulation results demonstrate that the improved framework can effectively lengthen the activation time of the inserted Trojan by 120 times and simultaneously reduce the design overhead by 0.123% when reasonably choosing the number of states as 3 and the length of sequence as 4.

IP core;hardware Trojan;activation time;expiry date;Finite State Machine(FSM)

1000-3428(2014)09-0019-04

A

TP407

10.3969/j.issn.1000-3428.2014.09.004

天津市自然科学基金资助重点项目(12JCZDJC20500)。

冯紫竹(1989-),女,硕士研究生,主研方向:信息安全,入侵检测;赵毅强,教授;刘长龙,博士。

2013-09-02

2013-10-22E-mail:tcfzz@126.com