基于PowerQUICC处理器的高速以太网接口设计

2014-05-25周玉娟

周玉娟

(中国电子科技集团公司第五十四研究所 河北 石家庄 050081)

基于PowerQUICC处理器的高速以太网接口设计

周玉娟

(中国电子科技集团公司第五十四研究所 河北 石家庄 050081)

PowerQUICC处理器专门针对融合、兼容和成本问题而设计。PowerQUICC处理器基于e500 Power Architecture技术的SoC平台开发,采用QUICC Engine技术和集成安全引擎。重点介绍了一种基于PowerQUICC处理器的高性能通信处理器模块及在此基础上实现的2种高速以太网接口,包括用eTSEC实现的高速以太网接口和用QUICC机实现的高速以太网接口,最后通过测试得到了这2种接口的性能,并加以比较。

PowerQUICC eTSEC QUICC机 性能

1 引言

如今基于IP的网络技术正在快速发展,由于传统的电路交换网络基础设施仍在继续运行,所以IP网络必须与现有基础设施无缝融合。设计采用的高性能PowerQUICC通信处理器专门针对融合、兼容和成本问题设计,支持多种接口和协议,并提供他们之间的高性能互连互通。

为适应网络技术快速发展的需求,各控制节点间应该具有高速和实时的数据通信能力。由于以太网络具有较大的带宽,可以满足数据传输的实时性要求,同时具有通用性强和技术成熟等优点,因此得到广泛地应用。介绍的基于PowerQUICC处理器的2种高速以太网接口具有性能高、使用方便、成本低、研发周期短和通用性强等特点,可应用于多种设备。

2 高性能通信处理器模块的实现

基于PowerQUICC处理器的高性能通信处理器模块将数据面及控制面的功能集中到统一的硬件平台上,特别适合通信网络的互连互通、网络安全设计以及对接口和协议类型多样性的需求。

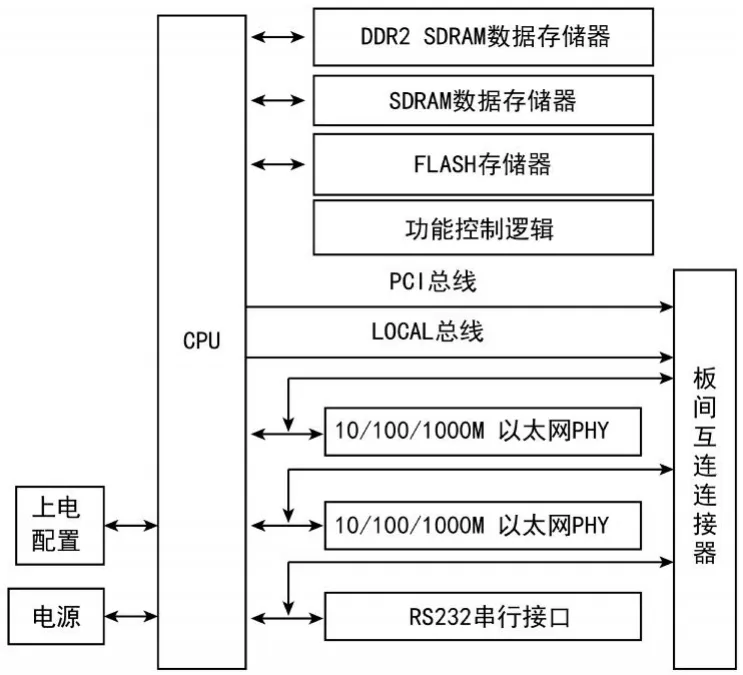

此高性能通信处理器模块主要由高性能CPU[1]、DDR2 SDRAM数据存储器、FLASH存储器、SDRAM数据存储器、RS-232串行接口、10/100/1000Mbps以太网接口(2个)、功能控制逻辑、上电配置、板间互连连接器和电源等组成,实现功能框图如图1所示。

图1 高性能通信处理器模块实现功能框图

高性能CPU最高运行速率高达533 MHz以上,采用PowerQUICC处理器[2]实现;DDR2 SDRAM数据存储器提供512 M字节的数据存储及32 M字节的程序存储,采用MT47H32M16BN-37E-IT实现;程序存储器和SDRAM数据存储器用于存储和运行底层硬件驱动程序和高层协议处理程序,程序存储器采用128J3A型FLASH实现,SDRAM数据存储器采用128J3A型SDRAM实现;10/100/1 000 Mbps以太网接口用于传输以太网承载的IP业务数据,采用88E1111-B2-1I000-BAB[3]实现;RS-232串行接口用于传输控制与通信信息,采用MAX3232E实现;功能控制逻辑用于进行整个板卡的功能控制,采用EP1C6T144I7实现;上电配置用于传输电平信号,采用PTH03030WAD实现;板间互连连接器与高速功能扩展模块相连,应用于性能扩展,采用高密度连接器87024-650实现。

3 2种高速以太网接口的实现

设计方案中使用增强的三速以太网控制器eTSEC实现一种高速以太网接口,使用QUICC机实现另外一种高速以太网接口。

3.1 用eTSEC实现高速以太网接口

增强的三速以太网控制器(eTSECs)可提供10 Mbps、100 Mbps及1 000 Mbps以太网/IEEE802.3接口速率。每个eTSEC支持多种标准的媒体无关接口,2个eTSECs可提供灵活的选择配置,支持不同速度的连通性及控制访问功能。

eTSEC能够自动识别与提取承载在以太网上的标准与非标准协议,包括对IPv4、IPv6与TCP/UDP包的识别及提取。eTSEC还可实现TCP/IP协议栈的加速。接口模式可配置为MII、GMII、TBI、RTBI、RGMII、RMII、8位FIFO和16位FIFO模式[2]。eTSEC功能模块结构框图如图2所示。

图2 eTSEC功能模块结构框图

用eTSEC实现高速以太网接口,需要对参数和寄存器等进行设置,具体如下:①先设置默认的参数;于进行buffer descriptor(BD)设置,BD格式如表1所示;③进行寄存器的初始化及参数RAM区的设置;④设置使能,进行数据的发送和接收,此时可通过设置环回验证接收的数据是否正确。

表1 BD结构示意图

3.2 用QUICC机实现高速以太网接口

QUICC机技术是一个可编程片上系统(SoC)功能块,可以加快通信协议的运行。它采用2个RISC引擎,而不是1个CPM引擎,提供达到以前4倍的吞吐量。QUICC机技术则增加了第3层和更高层的功能,以执行各种任务,如互通、转发、交换和分析,还提供集成的多协议处理和互通功能,速度高达1.2 GBytes,通过降低辅助Power Architecture处理器内核的工作负载来增强整个系统的性能。此外,QUICC机技术实现了与以前CPM的软件兼容和微代码兼容。

QUICC机是PowerQUICC处理器内部集成的功能模块,内部集成了多种通信外围控制器[4],可集成到芯片中用于构建多种功能模块的设计,用QUICC机实现高速以太网接口功能模块结构图如图3所示。

图3 UEC功能模块结构框图

用QUICC机实现高速以太网接口,需要对一些参数和寄存器等进行设置,具体同eTSEC,但此处需通过配置寄存器进行并行口的初始化。

4 2种高速以太网接口的性能比较

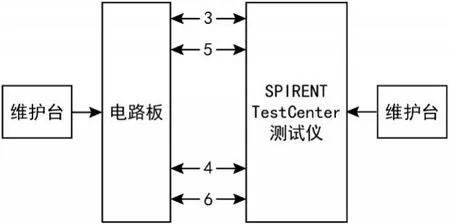

TestCenter测试仪是思博伦公司开发的一款功能强大的测试管理工具,可以真实地模拟实际网络的场景和流量模式的真实镜像,可以测量网络的接入/路由/交换、安全性和移动性等。下面通过SPIRENT TestCenter测试仪测试2种高速以太网口的性能[5,6],物理连接如图4所示。

图4 用SPIRENT TestCenter测试高速以太网接口性能的物理连接图

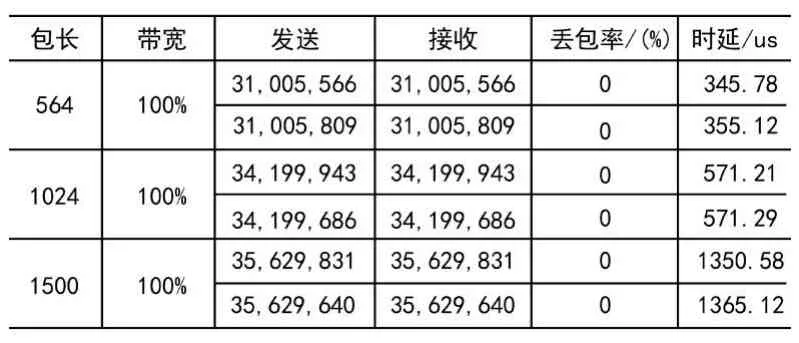

图4中,连接3、5表示ETSEC1与ETSEC2之间3层转发;连接4、6表示QUICC机UCC1与UCC2之间3层转发。在电路板和SPIRENT TestCenter测试仪进行相应的设置,启动测试仪开始侧试。测试结果如表2和表3所示。

表2 eTSEC实现的高速以太网接口之间三层转发性能表

表3 QUICC机实现的高速以太网接口之间三层转发性能表

5 结束语

提出了基于PowerQUICC处理器的2种高速以太网接口设计方案。设计方案具有通用性强、控制方便可靠和成本低等特点。将2种设计应用于测试系统进行实验验证,结果表明都能满足工程要求,目前2种高速以太网接口都已应用到工程中。

[1]戴梅萼.微型计算机技术及应用[M].北京:清华大学出版社, 2008.

[2]PowerQUICC Processor User Manual.Version 1[R].FreeScale Corp,2007.

[3]Integrated 10/100/1000 Ultra Gigabit Ethernet Transceiver. Version H[R].Marvell Corp,2006.

[4]QUICC Engine Block Reference Manual with Protocol Interworking.Version 4.4[R].FreeScale Corp.2012.

[5]SEIFERT R.千兆以太网技术与应用[M].郎波,等,译.北京:机械工业出版社,2000.

[6]信息产业电信传输研究所.千兆比以太网交换机测试方法[M].北京:人民邮电出版社,2001.

Design on High-speed Ethernet Interface Based Power on Processor QUICC

ZHOU Yu-juan

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

The PowerQUICC processor is specially designed to realize the integration,compatibility and cost reduction.This processor is developed with SoC platform based on e500 Power Architecture technology,and adopts the QUICC Engine technology and the integrated security engine.This paper mainly introduces a high-performance communication processing module based on PowerQUICC processors and two kinds of high-speed Ethernet interfaces based on the processing module,including the high-speed Ethernet interface based on eTSEC and the high-speed Ethernet interface based on QUICC engine.Finally,the performances of two interfaces are tested and compared.

PowerQUICC;eTSEC;QUICC engine;performance

TP393

A

1008-1739(2014)05-54-3

定稿日期:2014-02-12