基于时序优先的电路容错混合加固方案

2014-05-22黄正峰蒋翠云梁华国

黄正峰 陈 凡 蒋翠云 梁华国

基于时序优先的电路容错混合加固方案

黄正峰①陈 凡*②蒋翠云③梁华国①

①(合肥工业大学电子科学与应用物理学院 合肥 230009)②(合肥工业大学计算机与信息学院 合肥 230009)③(合肥工业大学数学学院 合肥 230009)

为了有效降低容忍软错误设计的硬件和时序开销,该文提出一种时序优先的电路容错混合加固方案。该方案使用两阶段加固策略,综合运用触发器替换和复制门法。第1阶段,基于时序优先的原则,在电路时序松弛的路径上使用高可靠性时空冗余触发器来加固电路;第2阶段,在时序紧张的路径使用复制门法进行加固。和传统方案相比,该方案既有效屏蔽单粒子瞬态(SET)和单粒子翻转(SEU),又减少了面积开销。ISCAS’89电路在45 nm工艺下的实验表明,平均面积开销为36.84%,电路平均软错误率降低99%以上。

微电子;软错误;时序裕度;触发器替换;复制门法

1 引言

微电子技术的不断发展,使器件尺寸降低到纳米尺度。持续减少的节点电容和高速增长的芯片复杂度使得集成电路对环境越来越敏感,由高能粒子引起的软错误不断增加。高能粒子轰击存储器或触发器等时序逻辑单元时,将引发单粒子翻转(Single Event Upset, SEU),时序单元的值将发生翻转,错误的值将保持到下一个值写入;轰击组合逻辑电路,将发生单粒子瞬态(Single Event Transient, SET),产生毛刺,并且有可能沿组合逻辑通路传播,如果毛刺恰好被时序逻辑采样到,将会导致集成电路功能错误。在较早工艺中,组合逻辑由于存在逻辑、电气和时钟窗屏蔽效应,软错误率较低,关注更多的是时序逻辑中的软错误。随着工艺尺寸变小,组合逻辑单元对软错误越来越敏感。组合逻辑单元的临界电量越来越小,粒子轰击更易造成翻转;流水线深度的加深,削弱了逻辑屏蔽和电气屏蔽效应;电路频率升高,导致时钟窗口变窄,削弱了时钟窗屏蔽效应。研究指出[1],微电子器件随着工艺尺寸越来越小,软错误成为一个显著的可靠性问题。软错误的衡量指标由软错误发生的频率(Soft Error Rate, SER) 来表征,单位为FIT(Failure In Time)。1FIT表示在109h内发生1次软错误,SER通常表征了电路运行期间受软错误的影响程度。

集成电路软错误研究主要有以下方面:(1)硬件和软件的协同仿真平台的软错误分析;(2)软错误率检测和缓解技术;(3)电路的加固。国内外针对电路的加固问题,已经提出许多加固方案,其中冗余是最常用的方式,按冗余方式分为空间冗余和时间冗余。针对时序逻辑中的SEU,主要是设计抗SEU的锁存器,提出的结构如TMR-latch, SDT-latch, HiPeR-latch[2]以及本研究小组所提出RHBD-latch[3]等。针对组合逻辑中SET,有基于时序冗余的方法、复制门法[4]、电压调整法[5]、门尺寸调整法[6]、输出钳位电路法[7]和选择逻辑节点法[8]等。文献[5]利用较高电压的门不易产生瞬态脉冲或者产生瞬态脉冲比较短小,在路径上更易被电气屏蔽来加固电路,该方法不适合在电路级实现,操作复杂。文献[6]利用门尺寸调整法,在当今主流的纳米工艺下,该方法很不适用,晶体管尺寸调整会干扰标准单元库广泛采用的工作方式且实施的复杂度也越来越高。文献[9]借鉴于C单元的原理,将门的晶体管级结构复制成两份,在只有一份出错,另一份正确的情况下,通过CWSP单元保持上一个正确的输出,硬件开销为原来的两倍。文献[10]引入成本感知的方法对组合逻辑单元进行选择性加固,依据算法自动执行可靠性的改进和相关成本之间的权衡,该方法没有考虑电气屏蔽,不够精确。文献[11]提出基于关键路径的3模冗余表决器插入算法,在不降低电路可靠性的情况下,减少了电路关键路径延时,但没有完全消除。

针对软错误问题,本文提出基于时序优先的电路容错混合加固策略。优先使用高可靠性触发器,利用时序冗余的SET防护原理来防护电路中的软错误,在面积开销很小的情况下使得可靠性有了很大提高,有效降低了容错代价。在某些要求高可靠性的应用领域,针对不能利用时序冗余法在时序紧张路径进行加固的不足,使用触发器替换和复制门法相结合的容错加固方案。由于使用了高可靠性容错时序单元,使得电路能免疫SEU。跟其它加固方案相比,本文方案不引入性能开销,优先加固最为关键的时序单元和组合逻辑节点,达到了容错开销和性能的有效折中。

2 触发器选择的加固策略

2.1 选择性加固

加固分为全加固和选择性加固,全加固是指对电路中所有的逻辑单元进行加固,但是该策略带来了较大的面积、延时、功耗开销。研究表明[4, 12],组合逻辑节点对于SET的敏感度并不相同。一部分节点的敏感度很高,屏蔽这些节点能很大提高电路的可靠性。因此,对电路有选择性地部分加固,可以有效地平衡可靠性和容错代价。

选择性的部分加固策略需要同时考虑面积开销、性能开销、SER等诸多设计指标。加固策略分为面积优先的加固策略和速度优先的加固策略。

2.2 时序冗余的触发器替换方法

现有大部分加固策略都是基于面积优先,没有考虑关键路径延时,因此提出考虑时序的触发器替换加固方法,利用触发器加延时单元的时序冗余SET防护原理来进行容错。在电路所有路径中找出时序宽松的路径,得到这些路径中的时序单元集合,加固这些时序单元集合不会降低电路性能。对这些集合中的时序单元在面积开销限制下,选择对电路可靠性影响从大到小的次序进行加固。通过将这些时序单元替换为容错时序单元,使其不仅能免疫自身SEU,还能屏蔽组合逻辑中的SET。文献[2]提出的HiPeR-latch具有良好的抗SEU性能。该结构的内部节点和输出节点可以容忍瞬态故障且与晶体管尺寸无关,具有更好的扩展性。与目前大多数文献中提到的锁存器相比,该结构对瞬态故障表现出更好的鲁棒性,同时更节省面积和功耗开销。与标准锁存器相比,延时时间更少,对电路性能影响很小。

本文方案运用Synopsys公司的Design Compiler (DC),将基准电路的网表文件输入到DC中,用DC综合穷举出基准电路所有路径。在这些路径中,通过C++统计出包含对应触发器的最大路径延时值,记在DT(m)中。用DT(m)表示每条路径的延时值,该路径含触发器m(m表示该路径中的触发器名),从DT(m)找出值最大的,即为关键路径延时值,用delay表示。通过增加延时单元dt来屏蔽组合逻辑SET,如式(1)所示。

找出DT(m)中小于等于Slack(m)的触发器(SetFF),通过精确的软错误率计算工具BFIT[13]及对该程序的改进,对电路中触发器进行SER分析,对这些触发器(SetCFF)的软错误率从大到小进行选择性替换。

3 触发器选择和复制门法混合的加固策略

上述方法虽然在电路的性能不降低的情况下,很大提高了电路的容错能力,可是在一些高可靠性应用领域,如军事和航空航天领域、银行金融领域以及关于人身安全的微电子器件使用领域,要求器件的可靠性达到99%以上,这要求更高的软错误防护能力。上述方法由于只选择时序冗余的路径,忽略了时序敏感路径,给容错带来了限制,为此提出触发器选择替换和复制门法结合的加固策略。

3.1 复制门法

文献[4]提出复制门法对组合逻辑进行加固。利用并行晶体管来扩大输出节点的驱动强度,能够更好地补偿瞬态脉冲,从而可以提高关键电荷值,并且可以屏蔽掉更多瞬态故障。随着新的工艺导致的晶体管交界面处的面积越来越小,瞬态脉冲强度将受到越来越多的限制。图1,图2为“与非”门进行复制门法的实施方法。

图1 原始“与非”门

图2 复制门法结构

与晶体管尺寸调整法相比,复制门法更适用于集成电路工艺尺寸的日益减小。复制门法复杂性很低,能够很好地扩展来适应工艺尺寸的减小。通过复制标准单元库中单元,可以很容易地在电路级实施。该方法还避免了重新设计和重新定制现有的标准单元库,和现有的设计流程兼容。通过关键电荷仿真,能将单个门单元软错误率降低25倍以上。

3.2 本文策略的具体实施

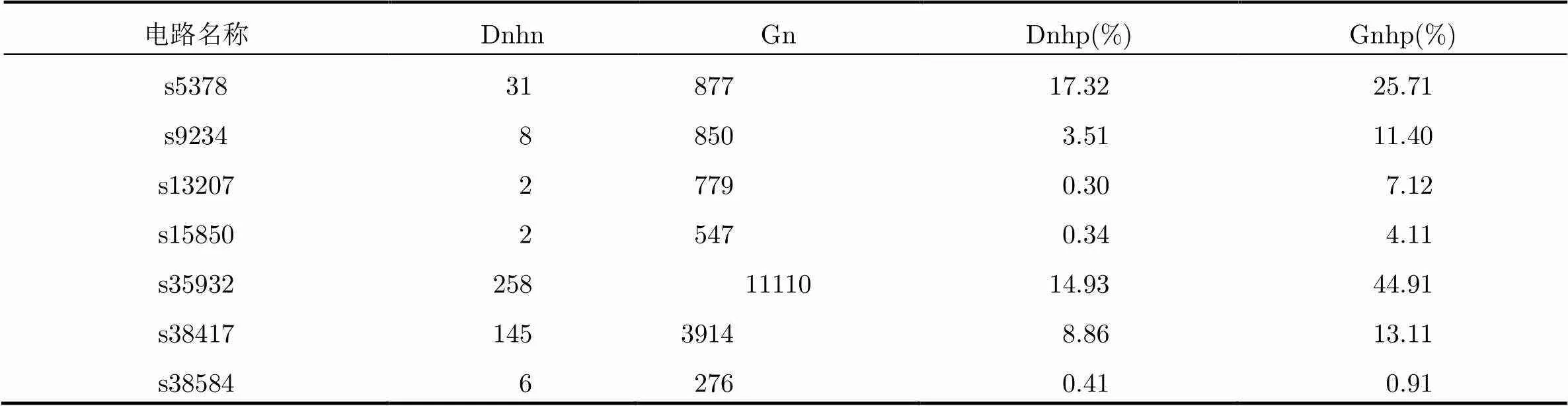

通过对基准电路文件拓扑分析,首先找出电路中不能加固的触发器,得到跟该触发器相连接路径的门的情况。由于组合逻辑中存在3种屏蔽效应,有的门不会产生瞬态脉冲,或者瞬态脉冲会被屏蔽掉,对这些门不用进行加固。通过BFIT对每个组合逻辑门软错误率进行较为精确的分析,统计出出错门的名称及门产生的软错误大小,与前面得到的跟触发器相连接的门进行对比,去掉那些不会对输出端造成软错误的门。基准电路中不能利用时序冗余法加固的触发器数设为Dnhn(DFF not harden number),对应这些触发器路径上会产生软错误的门数设为Gn(GATE number),不能加固触发器在基准电路中占的比例设为Dnhp(DFF not harden percentage),需要加固的门占基准电路中门的比例设为Gnhp(GATE need harden percentage),如表1所示。

表1 Dnhp和Gnhp情况

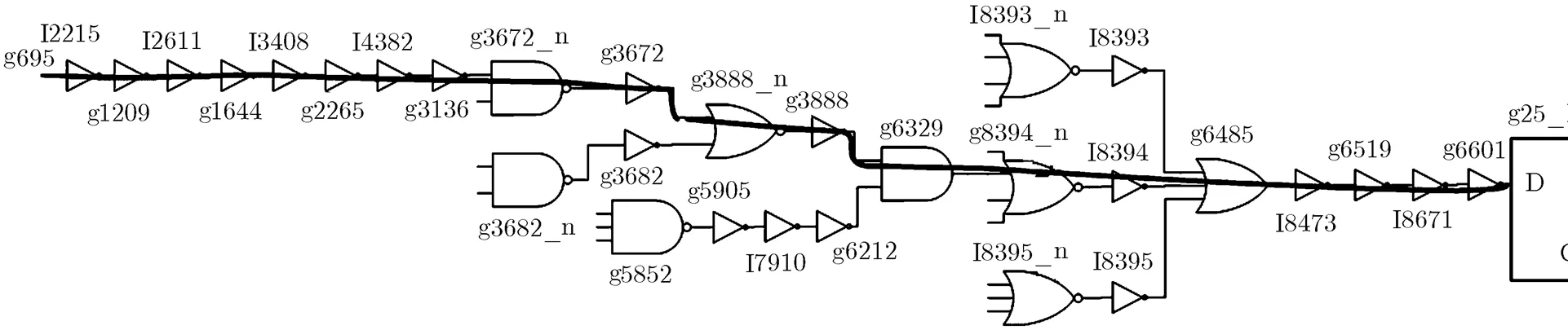

通过对电路路径进行分析,如在s9234电路中,通过算法得出g25_NEXT是不能使用时序冗余原理来防护SET的。故使用复制门法,对跟该触发器连接的路径上产生软错误的门进行加固,从而屏蔽组合逻辑SET。图3标注的曲线为跟该触发器相连接的一条路径,进行加固后的结果如图4所示。

图3 不能加固触发器对应的一条路径

图4 利用触发器替换和复制门法的加固方法

与g25_NEXT曲线标注的路径刚好每个门都有瞬态故障产生,所以每个门都用复制门法进行加固,而且这里触发器也替换成抗SEU的触发器,但是该触发器不能加延时单元。通过此方法,可以屏蔽上游逻辑门产生的SET,且由于使用了高可靠性触发器,也能防护SEU。

至此,本文已经提出了一个完整的选择性加固框架,可以使用时序冗余的触发器替换作为第1 级加固策略,将原电路中的标准触发器替换成HiPeR- DFF,使其不仅对SEU免疫,也能屏蔽组合逻辑中的SET。如果上述方法的容错性能达不到某些高可靠性的应用场合,可以使用触发器选择和复制门法相结合的第2 级加固策略。总的加固策略流程图如图5 所示。

4 混合加固效果分析

4.1 实验结果及分析

对ISCAS’89基准电路进行实验分析,使用45 nm Nangate工艺库。对电路中SER的分析使用BFIT工具,BFIT可以对任何一种可能的电路状态精确计算每个逻辑门受到粒子轰击引起的错误率,所以可以方便地分析和优化门级软错误。在Red Hat Enterprise Linux 5平台下运行BFIT程序,计算传播到每个触发器的FIT以及每个组合逻辑门的FIT数。利用C++对电路路径进行拓扑分析,得出不能加固触发器路径上的门的名称和个数,与BFIT输出文件进行对比分析,找出该路径上会产生软错误的门,对这些门进行复制门法加固。

图5 触发器选择和复制门法结合的加固流程图

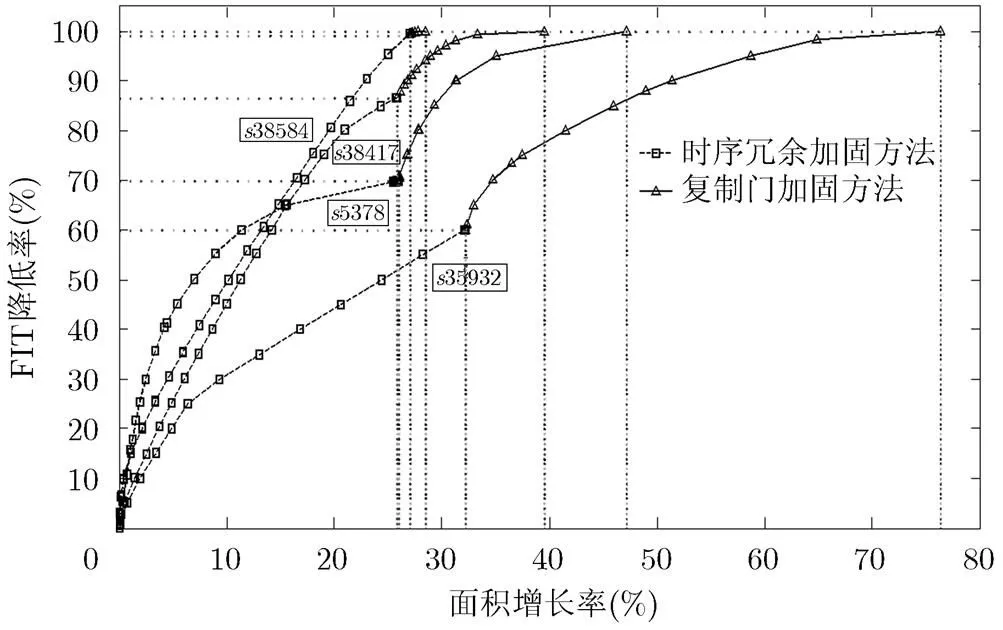

图6是利用本文方案针对ISCAS’89中电路的加固情况分析。其中横坐标代表面积的增长率,纵坐标代表FIT的降低率。由小正方形连接成的曲线是使用时序冗余原理的SET加固方法,由小三角形连接成的曲线是使用复制门法。从图中可以看出,开始时两种曲线都很陡峭,然后慢慢趋于平缓。这说明是按照贪婪算法来进行选择性加固的,将触发器和门的软错误率进行排序,优先加固产生FIT最大的触发器或者门,使得在面积开销较小的情况下,达到容错性能的最大提升并且加固策略一直没有给电路性能带来影响。

图7给出了触发器和门的加固比例与软错误防护比例的曲线图。图中由小正方形连接成的曲线是触发器的加固比例和软错误防护情况的曲线关系,由小三角形连接成的曲线是在触发器加固后的基础上门的加固比例和软错误防护情况的曲线关系。从图7中可以看出,软错误防护比例和触发器以及门的加固比例成正比,但不是线性关系,这是因为触发器和门对电路中软错误的贡献率不一样导致的。可以对加固的触发器的软错误大小进行排序,对不能加固的触发器路径上门的软错误也排序,优先加固软错误更大的触发器或者门,在面积开销和软错误防护性能之间取得更好的成本效益。从图7中可以看出,在触发器加固比例基础上,只需加固很小部分组合逻辑门,这样面积开销也控制在了合理范围内。

图6 利用触发器选择和复制门法进行加固的面积-FIT曲线图

图7 触发器和门的加固比例和软错误防护比例曲线图

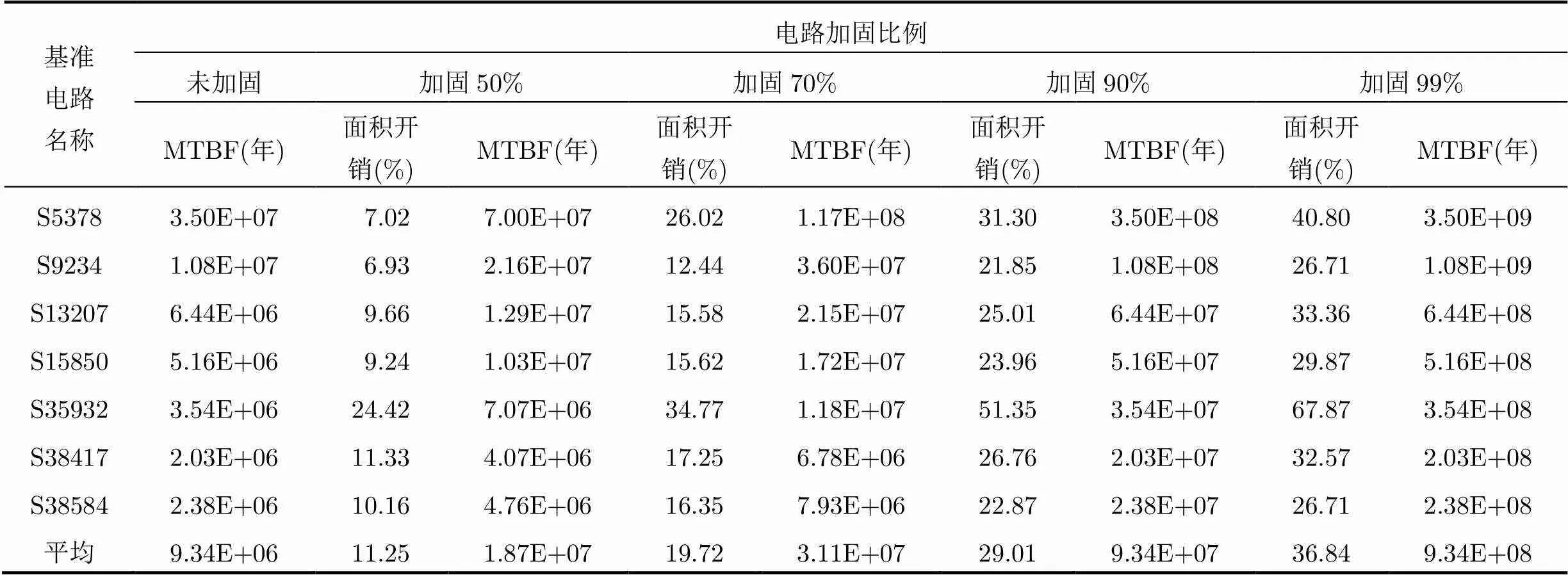

表2是ISCAS’89电路在不同加固百分比下,面积开销与平均故障间隔时间(MTBF)关系表。表中第1列给出了电路的名称,2~6大列给出了不同加固百分比下,所需要的面积开销和MTBF值大小,每1列最后一行给出平均的面积开销和MTBF值。可以看出,在加固比例不是很大的情况下,所需要的面积开销非常小而MTBF值却很大,随着加固比例的增大,MTBF值也是显著增大的。

图8是混合加固方案中,时序冗余法加固和复制门法加固屏蔽SET所占比例情况。可以看出,使用触发器替换法对SET防护比例占的很大,这是因为电路中只有极少数的触发器处在关键路径或者延时值较大的路径上,大部分触发器对应的路径的延时值都很小,从而基于速度优先加固的策略在实际中使用价值很高。而基于复制门法加固占的比例很小,这也节省了面积开销。

表2 ISCAS’89电路不同加固百分比下面积开销和MTBF关系

4.2 与相关工作比较

本文方案选用高性能抗SEU锁存器进行选择性加固,同时利用时序冗余SET防护原理和复制门法对组合逻辑SET进行加固。在保证电路性能并且面积开销很小的情况下,达到了电路容错性能的很大提高。文献[9]通过使用CWSP单元对组合逻辑门进行选择性替换;文献[14]提出时空3模冗余法对电路加固。以上方法能够在软错率和面积开销之间达到一定的折中,有效地降低了加固的代价。但是上述文献都没有考虑电路的关键路径,都对电路造成了一定的性能影响。

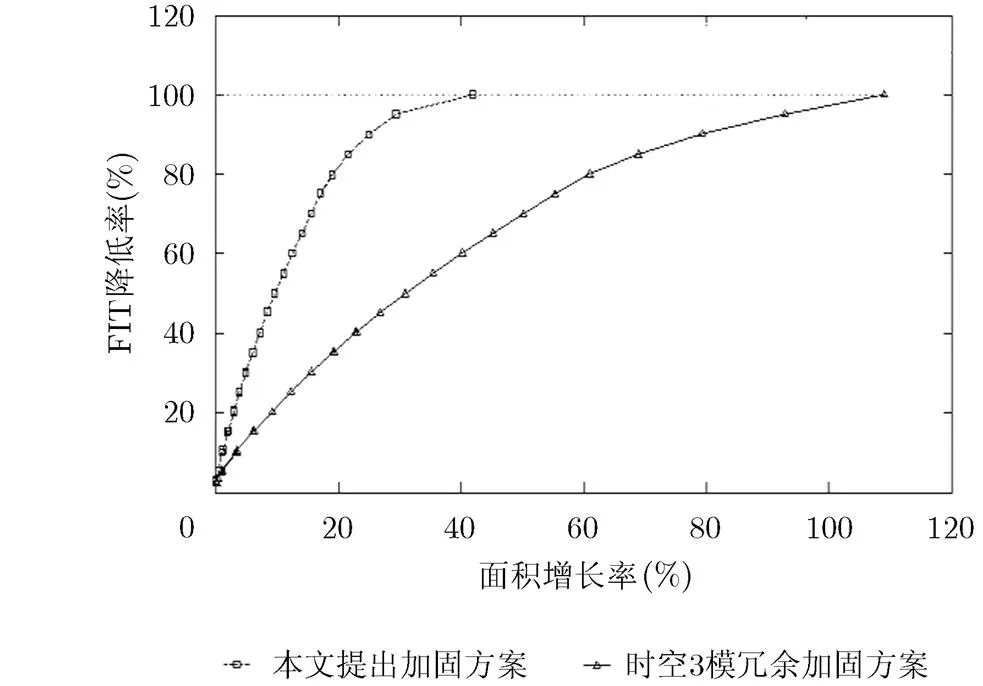

选择一个好的抗SEU时序单元是非常重要的。文献[14]中,使用时空3模冗余进行选择性替换加固,需要200%以上的面积开销,而且大多数表决器本身对软错误不免疫,这也限制了3模冗余的功效。图9是本文方案和时空3模冗余方案对电路进行加固的曲线比较图,从图中可以看出,在相同面积开销下,本文方案的可靠性提高大大高于时空3模冗余方案。

表3给出了在将组合逻辑单元可靠性提高到99%时,本文方案与其它方案平均面积开销比较。

表3本文方案与其他方案的比较

方案增加的面积开销(%)加固比例(%) 文献[9]方案44.7499 文献[14]方案99.7799 本文方案36.8499

图9 本文方案和时空3模冗余方案的面积-FIT曲线图

5 结束语

为了降低容忍软错误的硬件和时序开销,本文提出了一种新的电路混合加固策略。在保持电路性能情况下,利用时间冗余容错的思想,优先选择将电路中标准触发器替换为高性能抗SEU的时空冗余触发器,来屏蔽SET和防护SEU。针对一些要求高可靠性的应用领域,采用触发器替换和复制门法相结合的加固策略。利用对电路路径的拓扑分析,找出不能使用时空冗余触发器的路径,得到这些路径上会产生软错误的门,对这些门用复制门法加固。该方案的平均面积开销为36.84%时,软错误率降低了99%以上。该方案是根据贪婪算法对触发器和组合逻辑单元进行选择性加固的,能在有效面积开销下,最大程度降低电路软错误率。可以在实际应用情况下,合理选择面积开销来进行选择性加固。本文方案都是优先考虑电路时序为前提,在时序开销、面积开销和电路可靠性三者之间取得了有效的平衡。

[1] Massengill L W, Bhuva B L, Holman W T,Technology scaling and soft error reliability[C]. IEEE International in Reliability Physics Symposium (IRPS),Garden Grove, CA, April 2012: 3C.1.1-3C.1.7.

[2] Omaña M, Rossi D, and Metra C. High-performance robust latches[J]., 2010, 59(11): 1455-1465.

[3] Huang Zheng-feng and Liang Hua-guo. A novel radiation hardened by design latch[J]., 2009, 30(3): 0350071-0350074.

[4] Nieuwland A K, Jasarevic S, and Jerin G. Combinational logic soft error analysis and protection[C]. 12th IEEE International On-Line Testing Symposium, IOLTS, Lake of Como, Italy, July 2006: 251-257.

[5] Wu Kai-chiang and Marculescu D. Power-aware soft error hardening via selective voltage scaling[C]. IEEE International Conference on Computer Design, ICCD,Lake Tahoe, CA, Oct. 12-15, 2008: 301-306.

[6] Zhou Quming and Mohanram Kartik. Gate sizing to radiation harden combinational logic[J].2006, 25(1): 155-166.

[7] Garg R, Jayakumar N, Khatri S P,.. Circuit-level design approaches for radiation-hard digital electronics[J].(), 2009, 17(6): 781-792.

[8] Mahatme N N, Chatterjee Indranil, Patki Akash,.. An efficient technique to select logic nodes for single event transient pulse-width reduction[J]., 2013, 53(1): 114-117.

[9] 王俊, 梁华国, 黄正峰, 等. 一种对面积开销有效的组合逻辑选择性加固方案[J]. 计算机研究与发展, 2010, 47(S1): 173-177.

Wang Jun, Liang Hua-guo, Huang Zheng-feng,.. An effective selective hardening scheme of combinational logic for area overhead[J]., 2010, 47(S1): 173-177.

[10] Pagliarini S N, Naviner Lirida A De B, and Naviner Jean-FrancoisSelective hardening methodology for combinational logic[C]. Test Workshop (LATW), 13th Latin American, April, 2012: 1-6.

[11] 谭宜涛, 杨海钢, 黄娟, 等. 基于关键路径的三模冗余表决器插入算法[J]. 电子与信息学报, 2012, 34(2): 487-492.

Tan Yi-tao, Yang Hai-gang, Huang Juan,.. Voter insertion algorithm based on critical path for triple module redundancy[J].&, 2012, 34(2): 487-492.

[12] Polian I and Hayes J P. Selective hardening: toward cost-effective error tolerance[J].&2011, 28(3): 54-63.

[13] Holcomb D, Li Wen-chao, and Sanjit S A. Design as you see FIT: system-level soft error analysis of sequential circuits[C].Design, Automation & Test in Europe Conference & Exhibition, Nice, France, DATE’09, Apr. 20-24, 2009: 785-790.

[14] 孙岩, 张民选, 李少青, 等. 基于敏感寄存器替换的电路软错误率与开销最优化[J]. 计算机研究与发展, 2011, 48(1): 28-35.

Sun Yan, Zhang Min-xuan, Li Shao-qing,.. Optimizing soft error rate and overhead of circuits based on sensitive registers replacement[J]., 2011, 48(1): 28-35.

黄正峰: 男,1978年生,博士,副教授,主要研究方向为嵌入式系统综合与测试、数字集成电路的硬件容错、星载SoC芯片的抗辐射加固.

陈 凡: 男,1988年生,硕士,主要研究方向为数字集成电路的硬件容错.

梁华国: 男,1959年生,博士,教授,博士生导师,主要研究方向为内建自测试、数字系统设计自动化、ATPG算法、分布式控制等.

A Hybrid Hardening Strategy for Circuit Soft-error-tolerance Based on Timing Priority

Huang Zheng-feng①Chen Fan②Jiang Cui-yun③Liang Hua-guo①

①(&230009,)②(&,,230009,)③(,,230009,)

In order to reduce effectively the hardware and timing overhead for circuit soft-error-tolerance, a hybrid hardening technique for soft error tolerance is proposed based on timing priority in this paper. A two-stage hardening strategy is exploitsed by using flip-flop replacement and duplicated gate method to harden circuit. At first stage, based on the timing priority principle, high reliability temporal redundancy flip-flop is used to harden circuit on the path of timing slack. At second stage, duplicated gate method is used on timing sensitive path. Compared with traditional techniques, the proposed technique can not only mask the Single Event Transient (SET) and protect against the Single Event Upset (SEU), but also reduce the overhead of the area. The experiment result of ISCAS’89 benchmark circuits in 45 nm Nangate process proves that the circuit average soft error rate is reduced by more than 99% and the average area overhead is 36.84%.

Micro-electron; Soft error; Timing slack; Flip-flop replacement; Duplicated gate method

TN402

A

1009-5896(2014)01-0234-07

10.3724/SP.J.1146.2013.00449

2013-04-07收到,2013-07-02改回

国家自然科学基金(61274036, 61106038, 61106020, 61371025)和博士点基金(20110111120012)资助课题

陈凡 cf2008chenfan@163.com