800~975 MHz太阳射电数字观测终端的设计与实现

2014-05-13张西洋何乐生董亮杨晓玲

张西洋,何乐生,董亮,杨晓玲

(1.云南大学信息学院,云南 昆明 650091;2.中国科学院天体结构与演化重点实验室,云南 昆明 650011;3.中国科学院云南天文台,云南 昆明 650011;4.电子科技大学通信与信息工程学院,四川 成都 611731)

800~975 MHz太阳射电数字观测终端的设计与实现

张西洋1,2,何乐生1,2,董亮2,3,杨晓玲4

(1.云南大学信息学院,云南 昆明 650091;2.中国科学院天体结构与演化重点实验室,云南 昆明 650011;3.中国科学院云南天文台,云南 昆明 650011;4.电子科技大学通信与信息工程学院,四川 成都 611731)

位于云南天文台凤凰山本部的10 m太阳射电望远镜是中国太阳射电物理界重要的观测设备之一,其设计之初,800~975 MHz频段受到移动电话的严重干扰,不能正常工作,因此缺失这一频段的观测资料。近年来,随着微波和数字器件性能的提升以及移动电话工作频段的改变,使得这一重要频段的观测变得可行。针对800~975 MHz频段的太阳射电天文信号,提出了一种基于现场可编程门阵列(Field Programmable Gate Array,FPGA)和千兆以太网的实时采集与处理方法。在数据采集和处理过程中,系统采用流水线方式,得到了太阳射电信号的实时频谱图;采用硬件描述语言Verilog实现了千兆以太网的数据传输,提高了传输效率;另外本系统采用分时传输机制,完成千兆以太网的UDP数据包的传输。最后还对所得数据进行了误差分析和结果分析,证明了本文提出的实时信号采集、分析和传输方法的正确性和可靠性。

射电天文学;实时信号处理;FPGA;千兆以太网;数字观测终端

CN53-1189/P ISSN1672-7673

位于云南天文台凤凰山本部的10 m太阳射电望远镜是中国太阳射电物理界重要的观测设备之一,其覆盖频段为厘米波波段(625~1 500 MHz),对研究太阳活动有着重要的意义。十多年前,建立10 m高分辨率频谱射电望远镜时,800~975 MHz位于移动电话工作频段,受到干扰较多,易引起接收机饱和,无法进行正常观测,为此当时舍弃了重要的800~975 MHz频段。

目前,微波器件及数字信号处理终端的动态范围较之十年前已经大大提升,250MSPS以上采样率的高速模拟数字转换器(Analog-to-Digital Converter,ADC)的动态范围能达到72 dBc(dBc,相对于载波频率幅度)。另外,移动电话的工作频段也发生了较大的变化。因此,本系统通过合理的射频前端和数字终端的设计,补充了这一重要频段的观测。本系统的各项性能指标较之早先设计的10 m射电望远镜其他频段的数字观测终端都有较大幅度的提高。

1 系统结构

本系统采用图1的结构实现数字观测终端。首先通过模拟下变频器,将10 m天线接收的800~975 MHz模拟信号作下变频处理,得到0~87.5 MHz模拟信号,再通过245.761 MHz AD采样[1]输入到现场可编程门阵列(Field Programmable Gate Array,FPGA),现场可编程门阵列对信号作实时频谱分析并叠加后通过千兆以太网,将数据以UDP方式发送到远端PC机;PC机通过C#语言自行开发的软件对数据进行整合、显示和存储。针对射电信号的左右两个旋向,系统中所有的信号采集和处理步骤都被分为左、右旋向两个部分。本系统充分利用了现场可编程门阵列的并行性,解决了两个旋向同时进行实时处理的矛盾。

图1 系统结构框图Fig.1 The block diagram of our digital observation terminal system

本文重点论述的数字观测终端部分的核心是基于现场可编程门阵列的信号处理部分,主要包括:对两路信号加窗、FFT变换、平方和开根号、取对数、叠加和通过以太网UDP方式封装和传输等处理步骤,各个步骤之间的关系如图2。

图2 FPGA信号处理部分结构框图Fig.2 The block diagram of the FPGA signal-processing section of our system

2 系统设计

2.1 现场可编程门阵列设计

本系统采用了Xilinx公司40 ns工艺、3D层叠技术的Virtex-6系列顶级现场可编程门阵列[2]: XC6VLX240,其最高工作频率可达300 MHz以上,含有24万个逻辑单元,可以满足实时数据采集和处理的需要。

系统中双通道AD转换[3]部分采用4DSP公司的高速AD采集卡FMC150实现,FMC150采集卡的AD转换芯片为TI公司的14位顶级高速AD芯片ADS62P49,其全功率输入带宽为500 MHz,输入范围10 dBm,在全速条件下其输入信噪比可达73 dBFS(dBFS,相对于ADC的满量程范围),无杂散动态范围SFDR为88 dBc。由于Xilinx公司的现场可编程门阵列内部没有集成模拟锁相环,由其提供的时钟孔径抖动较大,不能作为模拟数字转换所需的时钟源。因此本系统采用FMC150板载的模拟锁相环产生的245.761 MHz时钟作为模拟数字转换器的采样时钟,和现场可编程门阵列中与采样相关部分的时钟。即图2中虚线框外的所有部分都采用这个时钟作为工作时钟。至于虚线框内的部分,必须工作于以千兆以太网所需的1 GHz频率上,无法由245.761 MHz时钟直接产生,因此使用了现场可编程门阵列集成数字锁相环产生的125 MHz工作时钟。

本系统的FMC150采集卡与ML605之间通过Xilinx公司定义的,带宽达到9GB/S的LPC接口实现高速连接。

图2中现场可编程门阵列内部数据处理的步骤和精度如下:左边的加窗起到了抑制频谱泄露、消除栅栏效应[3]的作用,其结果与模拟数字转换器采样部分保持一致为14位宽;采用FFT变换对信号作频谱分析,FFT采用完全精度输出28位实数和28位虚数;功率计算是将信号的FFT复数结果转换为实际功率,本系统的功率结果是13位;取对数是对功率的对数表示,叠加是取均值,以降低数据产生的速率,叠加输出的结果是13位;TCP/IP接口用来对功率结果作以太网UDP传输。下面对各部分作具体介绍。

2.1.1 加窗与FFT变换

加窗采用Memory IP core[4],预先将8 192点Hanning窗系数存入存储单元,与延时同步后的信号相乘。FFT变换调用FFT IP核完成[5-8],采用流水线模式[9],做14位8 192点FFT。

2.1.2 计算功率与取对数

计算功率是对FFT的复数结果作平方和与开根号运算,系统调用了Xilinx的IP核完成。FFT结果为28位,实部和虚部做平方和结果为57位。取高48位开两次根号最终结果为13位数据。取对数,采用Memory IP Core的方式作对数表进行查询输出。对数表通过计算自然数1至8192的对数放大2000倍后四舍五入。最终这个对数表也是13位。整个系统采用流水线方式,需在末级输出进行相位同步,其是计算平方和、开根号和取对数模块的运算时间,根据FFT的输出索引,得到新的同步索引。

2.1.3 数据叠加

叠加是通过两个存储器乒乓式相加完成。其中一个与新到的数据相加之后存入另一个存储器,在完成8192点(一次完整的FFT结果)相加后,这种操作反转,反复相加。叠加单元通过同步索引完成相加的起止。

2.1.4 跨时钟域的设计

系统中,AD采样、加窗、FFT变换、计算功率、取对数和叠加部分采用的时钟频率为245.761 MHz,而千兆以太网需要125 MHz的时钟频率。信号由频谱分析部分到千兆以太网传输时,跨越了两个不同的时钟域,这种情况的直接传输很容易产生亚稳态。并且,本系统两路频谱分析结果是相互独立的。两路相互独立的信号同时进入不同频率的千兆以太网部分进行传输,亚稳态发生的概率更大。

为了避免亚稳态的产生,系统采用基于FIFO的“等待握手机制”克服这个问题:信号采集处理部分每当完成一定长度信号的采集和处理后,就会将结果放入FIFO,并发出数据传输请求信号,使用125 MHz时钟的千兆以太网部分在收到两路的传输请求信号后,将返回一个允许传输信号并从FIFO中读取处理结果,并完成两路信号处理结果的传输。

2.1.5 UDP包的生成和传输

由于每个通道的FFT计算以及叠加是独立完成的,所以需要同步两通道的相位。系统是让先完成的通道等待后完成的通道实现。两通道的数据同步后,进行UDP帧封装[10-11]。系统采用1 024字节UDP帧。FFT叠加最终得到13位结果,传输前4 096个点。即每通道有8 192个字节,两通道需要16 KBytes,16帧,最后再加包尾共17帧。包尾帧主要完成包的和校验、左右旋的标识,以及一个完整数据包结束的指示。

系统采用245.76 MHz时钟做FFT叠加,叠加1 024次耗时34 ms。即传输的数据是34 ms内数据的平均值。因为FPGA的流水线结构,在做1 024次叠加的同时可以传输上次叠加结果,在保证数据的连续性和正确性时,UDP包传输的最大时间为34 ms。这里采用1ms的帧间间隔,即一个UDP包传输用时17 ms,剩余17 ms空闲,同时这个空闲时间留给上位机处理。

2.2 上位机软件设计

系统以C#作为上位机软件开发工具,其具有以下特点(1)简洁的语法;(2)精心的面向对象设计;(3)与Web的紧密结合;(4)完整的安全性与错误处理;(5)版本处理技术;(6)灵活性与兼容性[12]。

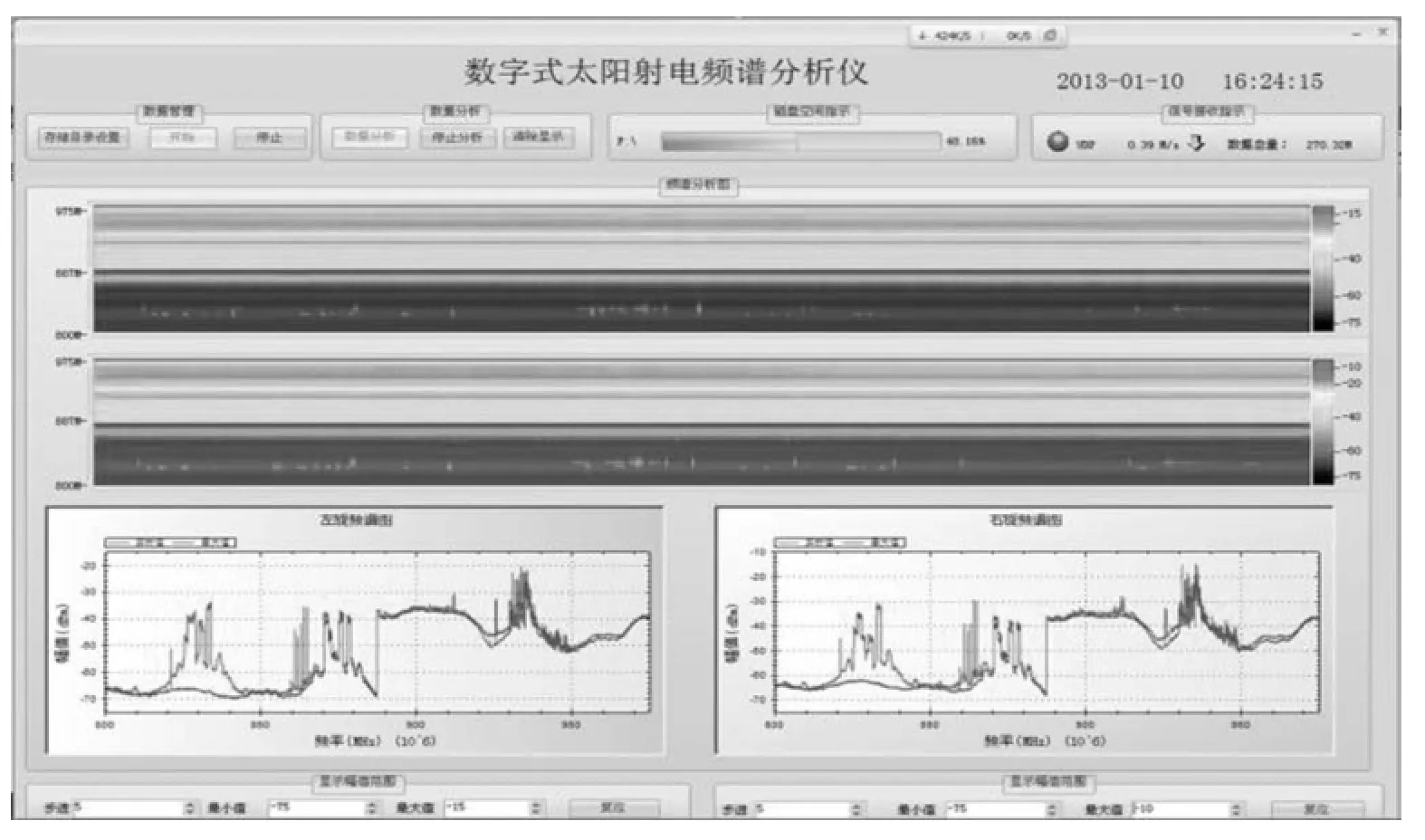

上位机等待UDP接收缓冲区的数据,当收到包尾后作包的完整性和正确性校验。为了减缓显示负担,在收到50包数据后做一次显示。系统产生一个完整的数据包用时34 ms,所以刷新间隔为1.7 s。当数据达到240 MB后重新另写数据文件,方便以后数据移动与管理。上位机软件界面图如图3。

图3 上位机软件界面图Fig.3 PC software interface of our system

3 截断误差分析

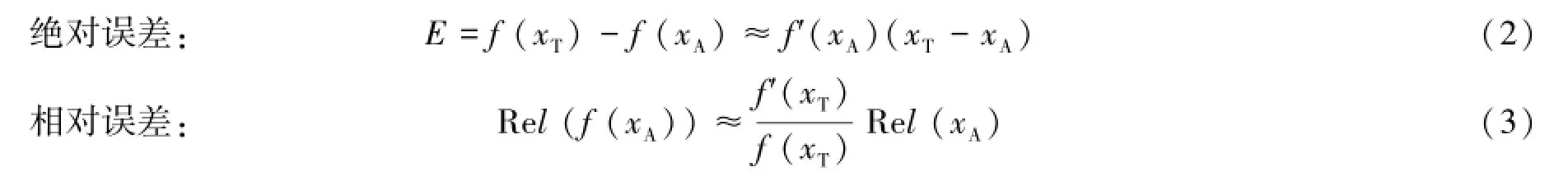

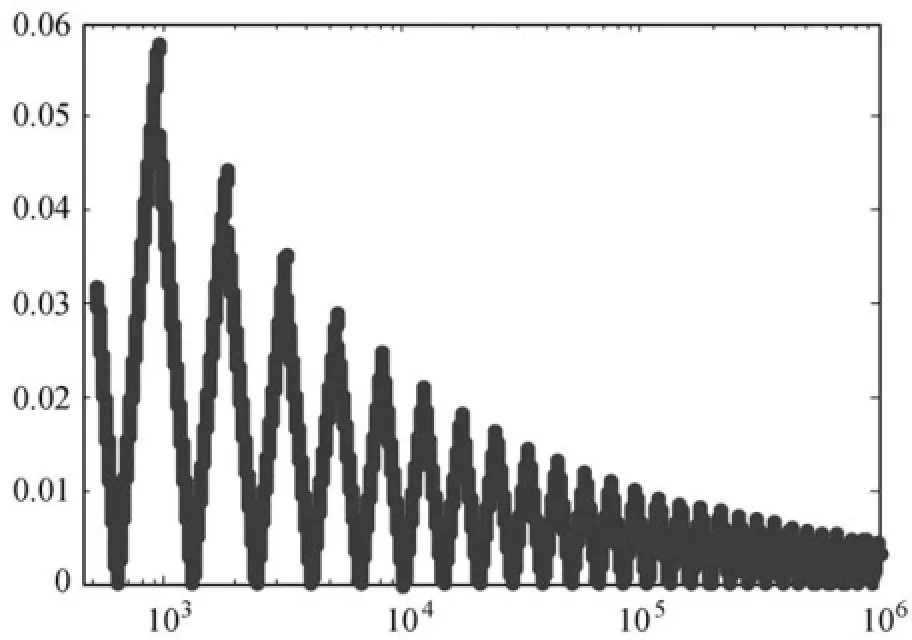

下面就图2中,在FPGA实施的一系列算法产生的系统截断误差进行分析,看其是否会对系统的精度带来无法容忍的影响。采用柯西中值定理分析系统的截断误差:

其中c是xA和xT间的一个未知点。因为通常xA和xT很接近,所以,

(1)对于x<29=512,xA=0,代入(2)、(3)式有:

(2)对于29≤x<257,xT=xA,代入(2)、(3)式,考虑结果的四舍五入,有:

(1)对于x<29=512,代入(4)、(5)式,考虑结果的四舍五入,有:

3、对于取对数f(x)=2000 log10x。

(1)对于x<29=512,代入(8)、(9)式,考虑结果的四舍五入,有:

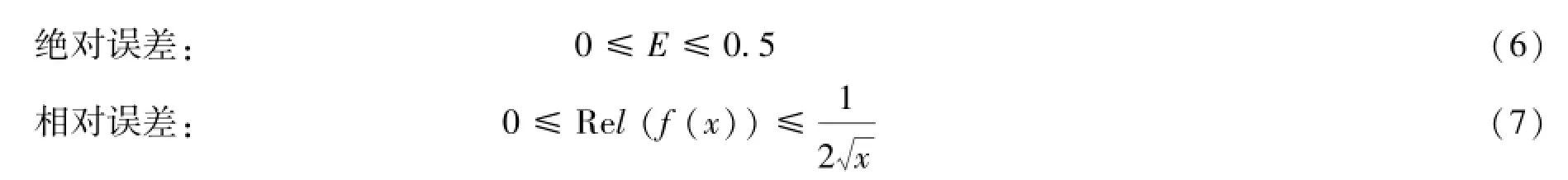

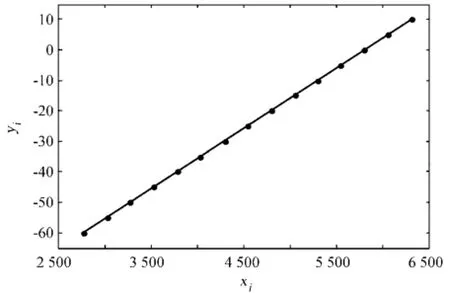

最终结果如图4和图5。图4是FPGA数字处理部分最终输出的相对误差,可以看出,它是随着数值的增大相对误差变的越小;图5(a)是理论值与实际最终结果输出的比较;图5(b)是系统定标后最终显示的结果,很明显,系统在-60 dBm时误差小于1 dBm。

经过上面的分析,采用本文提出的方法后,系统误差在可以容许的范围内甚至还有放宽的余地,但由于FPGA内部还有足够的计算资源,没有为此降低计算的精度。

图4 最终结果512至106的相对误差Fig.4 Relative errors of the final outputs(in the range of 512 to 106)of the FPGA section

4 系统定标

上述所有步骤中,系统对输入的射电信号进行了AD转换、FFT和叠加等操作,对于系统功率而言,这些变化都属于一次线性变换。因此,输出的绝对数值虽然没有物理意义,但是和输入的射电信号能量成一次线性关系。因此在执行完上述所有操作之后,还需要使用一元线性回归模拟对系统定标。

图5 最终结果部分比较.(a)系统输出结果比较;(b)上位机标定结果比较Fig.5 Comparison of some final outputs to theoretical values.(a)Comparison for final outputs of the system. (b)Comparison for final outputs after being calibrated by the PC

本文采用Agilent矢量信号发生器E4438C ESG,放出10 dBm~-60 dBm步进5 dBm的正弦信号,通过系统进行计算并作记录,结果如表1,其中,xi表示系统频谱分析的结果;yi表示Agilent矢量信号发生器输出的信号能量真值。这里x是自变量,y是应变量,要求y对x的回归。

表1 信号能量对应表Table 1 A list of signal-energy inputs and corresponding signal-energy outputs for the system

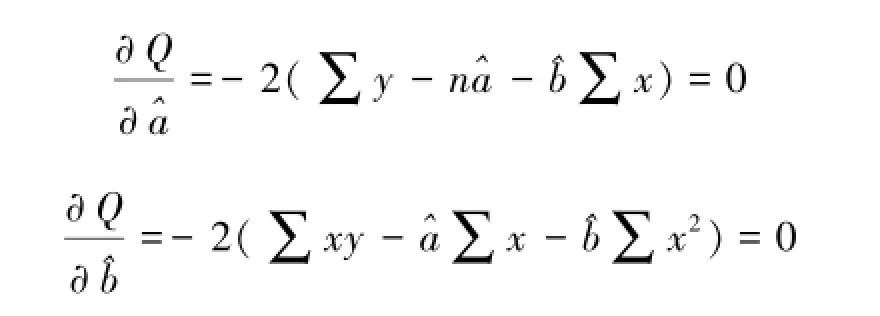

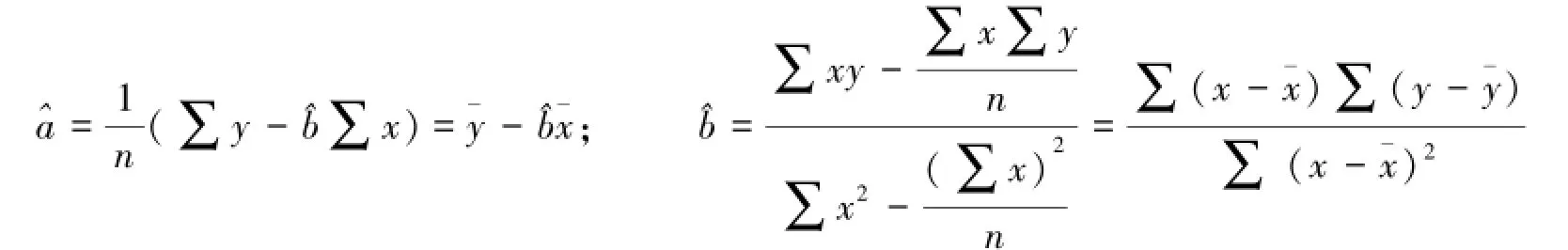

其误差总和,可以表示为误差平方和的形式:

解上式,可得:

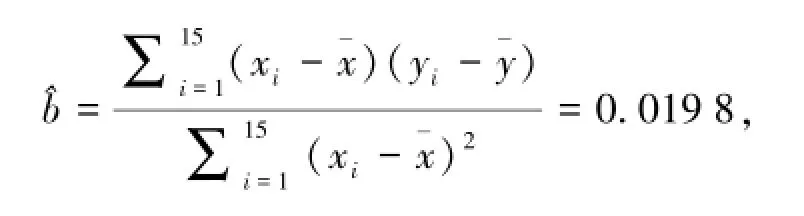

本文样本总数n=15,计算参数b的估计:

计算参数a的估计:

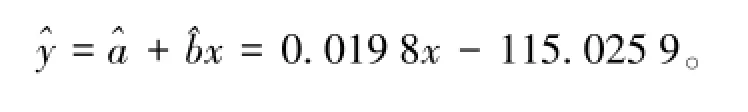

因此所求的回归直线方程为:

回归直线与实测真值散点的关系如图6。

相关系数rxy>0.8,表明x与y有很强的线性相关性,说明系统采用的一元一次回归模型的正确性,同时也说明了上述拟合过程得到的估计系数a和b是正确的。

5 结果分析

为测试系统的线性度,使用Agilent E4438C ESG矢量信号发生器进行测试。Agilent E4438C ESG调至频率步进扫描方式,输出805~875 MHz、5 000点、1 s积分时间、-2 dBm正弦信号,接入系统进行测试。系统经过70 min的测试,其扫频频段为805~863 MHz,结果如图7,整个扫频过程得到的频谱结果是一条直线,经过对存储数据的分析发现,信号功率波动在-2 dBm以下,频谱分析的结果最大误差在0.1 dBm以内,属于正常范围。说明系统具体良好的测试精度。

图6 信号能量散点图与其回归直线图Fig.6 A plot of signal-energy outputs versus signal-energy inputs with the best-fit linear relation included

图7 扫频测试结果Fig.7 Results of the frequency-sweeping test

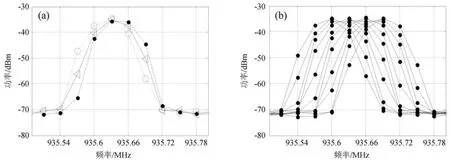

图8是用MATLAB导入历史数据绘制的图,能实时反映系统对频率的响应情况。由图8可以看出,在每隔0.03 MHz的频点上都有信号的能量值,符合系统软件设置的最低频率分辨率0.03 MHz。而且,从图8(b)可以看出,在0.03 MHz频段内,系统绘制了4条谱线,所以,在不考虑峰值能量的情况下,系统的最低频率分辨率可达0.007 5 MHz。

图8 频率分辨率测试结果.(a)3条谱线;(b)11条谱线Fig.8 Results of the test for the frequency resolution.(a)The case with three spectral lines. (b)The case with eleven spectral lines

综上所述,系统的技术指标与目前使用的数字观测终端比较结果如表2。

6 结束语

系统针对800~975 MHz频段太阳活动观测信号,提出了完整的终端解决方案,系统基于Xilinx FPGA XC6VLX240设计了整个频谱分析过程以及千兆以太网UDP的传输。目前,系统已经完成了测试(实物图见图9),加入实际信号,实践证明了系统的正确性、可靠性和可行性。上述通过FPGA、高速ADC和软件无线电构建射电天文观测仪器的方法,被证明是有效的,将在未来的射电天文领域发挥更加巨大的作用。

图9 数字终端实物图Fig.9 A picture of our digital observation terminal

表2 本系统与原系统方案的技术指标的比较Table 2 Comparison between technical specifications of our system and those of a current system in use

[1] 陈珏利,曾成志,郑海荣,等.基于ADS6122和FPGA的多通道信号采集系统的设计[J].电子器件,2012,35(4):406-411.

Chen Jueli,Zeng Chengzhi,Zheng Hairong,et al.Design of multichannel data acquisition system based on ADS6122 and FPGA[J].Chinese Journal of Electron Devices,2012,35(4): 406-411.

[2] 朱凯,张坚.基于解析信号处理的下变频系统FPGA实现与天文应用[J].天文研究与技术——国家天文台台刊,2009,6(1):51-56.

Zhu Kai,Zhang Jian.The FPGA realization of a DDC system based on analytical-signal processing and its application in astronomy[J].Astronomical Research&Technology——Publications of National Astronomical Observatories of China,2009,6(1):51-56.

[3] 刘广臣,张惠安,贾爱宾.数字信号处理中的加窗问题研究[J].长沙大学学报,2003,17 (4):59-62.

Liu Guangchen,Zhang Huian,Jia Aibin.Study on the window-adding problem in the digital signal processing[J].Journal of Changsha University,2003,17(4):59-62.

[4] Xilinx Corporation.LogiCORE IP BlockMemoryGenerat-or v6.2.[EB/OL].[2013-04-21]. http://www.xilinx.com.,2011:1-119.

[5] Xilinx Corporation.LogiCORE IP Fast Fourier Transfo-rm v7.1.[EB/OL].[2013-04-21].http://www.xilinx.com.,2011:1-59.

[6] 任健,高晓蓉.基于FPGA的FFT处理器设计[J].现代电子技术,2010(24):142-144+147.

Ren Jian,Gao Xiaorong.FPGA-based design of FFT processor[J].Modern Electronics Technique,2010(24):142-144+147.

[7] 刘健,史彩娟,赵丽莉.基于FPGA的高速浮点FFT的实现研究[J].微型机与应用,2012 (14):79-81+84.

Liu Jian,Shi Caijuan,Zhao Lili.Research of high speed floating point FFT based on FPGA[J].Microcomputer&Its Applications,2012(14):79-81+84.

[8] 刘彬杰,吴廷婷.基于Xilinx FPGA IP核的FFT算法的设计与实现[J].内江科技,2011 (4):154-155.

[9] 樊光辉,许茹,王德清.基于FPGA的高速流水线FFT算法实现[J].电子工程师,2008,34(3):38-40+53.

Fan Guanghui,Xu Ru,Wang Deqing.Implementation of high speed pipelining FFT algorithm based on FPGA[J].Electronic Engineer,2008,34(3):38-40+53.

[10] 徐进,陈卯蒸,李健.嵌入式TCP/IP协议在接收机杜瓦性能参数监测系统中的应用[J].天文研究与技术——国家天文台台刊,2011,8(2):108-112.

Xu Jin,Chen Maozheng,Li Jian.Application of an embedded TCP/IP protocol in a dewar performance-parameter monitoring system of a radio receiver[J].Astronomical Research&Technology——Publications of National Astronomical Observatories of China,2011,8(2):108-112.

[11] 谌俊毅,陈东,范玉峰,等.基于嵌入式系统的望远镜远程控制实验[J].天文研究与技术——国家天文台台刊,2007,4(1):36-41.

Chen Junyi,Chen Dong,Fan Yufeng,et al.The remote control experiment of the telescope based on the embedded internet[J].Astronomical Research&Technology——Publications of National Astronomical Observatories of China,2007,4(1):36-41.

[12] 高经理.C#语言的特点[EB/OL].[2013-04-21].http://www.365zhaosheng.com/html/2010/06/20100629152156215454.shtml.

Design and Implementation of a Digital Observation Terminal for Solar Radio Observation within the 800MHz-975MHz Band

Zhang Xiyang1,2,He Lesheng1,2,Dong Liang2,3,Yang Xiaoling4

(1.College of Information Science and Engineering,Yunnan University,Kunming 650091,China,Email:he_lesheng@263.net;2.Key Laboratory of Structure and Evolution of Celestial Bodies,Chinese Academy of Sciences,Kunming 650011,China;3.Yunnan Observatories,Chinese Academy of Sciences,Kunming 650011,China;4.College of Communication and Information Engineering,University of Electronic Science and Technology of China,Chengdu 611731,China)

The 10m solar radio telescope of the Yunnan Observatories(at the Phoenix Mountain)is an important observational equipment of solar radio physics in China.With its original design,the radio telescope did not work properly in the 800MHz-975MHz band because of the interference of mobile phones.In recent years,with the enhancement of the technological specifications of microwave devices and digital components,and with the change of the operation bands of mobile phones,solar radio observation with the telescope in this important band becomes feasible.In this paper we propose real-time signal acquisition/processing methods for the solar radio observation using the telescope in the 800MHz-975MHz band based on the FPGA and Gigabit-Ethernet technologies.The pipeline of the system in which we implement the methods adopts the Verilog hardware description language,so that it has achieved data transmission through a Gigabit Ethernet and has improved the data-transmission efficiency.We have obtained real-time solar radio spectra through this system. In addition,the system incorporates time-sharing transmission mechanisms,which allow the Gigabit-Ethernet UDP packet transmission.We finally present the error analysis of outputs of the system as well as results of certain tests of the system.These show the accuracy and reliability of the proposed real-time methods.

Radio astronomy;Real-time signal processing;FPGA;Gigabit Ethernet;Digital observation terminal

TP274

A

1672-7673(2014)02-0118-09

2013-04-21;

2013-05-10

张西洋,男,硕士.研究方向:数字信号处理.Email:he_lesheng@263.net