基于FPGA的红外相机时序构造设计

2014-05-10韩红霞曹立华

韩红霞,孙 航,曹立华

(中国科学院 长春光学精密机械与物理研究所,吉林 长春 130033)

1 引 言

光电跟踪测量设备是能够跟踪空中飞行目标,并给出目标方位值和俯仰值的设备。红外相机是根据物体的热辐射成像的相机,目前在军事、医疗、航天等很多领域都广泛应用。光电跟踪测量设备采用红外相机跟踪目标,可以在目标与背景亮度差值不大的情况下仍然稳定跟踪,然而红外相机的使用寿命是有限的,大型红外相机的使用寿命一般是2 000~5 000h,如果频繁地开启相机,必然会缩短设备的使用年限,同时大靶面红外相机基本依赖进口而且价格昂贵,更换相机不仅会增加成本而且会耗费很长的订货时间。为减少红外相机的开机时间,节省项目开发成本,设计了红外相机时序构造系统,在进行项目调试和实验时,采用构造的红外相机输出信号,提供给后续图像处理等系统作为数据源,在进行实际的跟踪任务时再开启红外相机。设计的基于FPGA的红外相机时序构造系统输出的信号时序与真实的红外相机输出时序保持一致,输出的像素值数据采用渐变数,可以作为图像传输系统、图像处理等后续系统的数据源,以供其进行编程和调试,调试成功之后直接将程序应用到红外相机信号的传输、处理等操作,这样就省去了程序开发、调试和验证时频繁的启动红外相机的过程,节省了相机的开机时间,同时也延长了设备的使用年限,节约了项目的开发成本,因此基于FPGA的红外相机时序构造系统设计具有很强的工程实践意义。

2 系统结构设计

2.1 硬件平台结构设计

基于FPGA的红外相机时序构造系统硬件平台主要包括电平转换单元、FPGA逻辑设计单元、时钟处理单元以及串口数据收发单元等,其中FPGA逻辑设计单元是设计的核心,实现系统的时序配置和逻辑控制,图1给出系统硬件平台设计框图。

图1 红外相机时序构造系统硬件平台设计框图Fig.1 Hardware structure diagram of the IR camera sequence construction design

如图1所示,晶振时钟OS_CLK为系统提供输入时钟信号,由FPGA内嵌的PLL对其进行处理,产生系统的工作时钟信号。串行数据输入电平转换芯片采用MAX3071,将RS422电平格式信号转为LVTTL电平格式信号,提供给FPGA。相机信号接收芯片采用DS90CR288,将相机输出的CameraLink电平格式信号转换为LVTTL电平格式信号,提供给FPGA进行时序测量,时序测量完成之后FPGA编程构造红外相机信号,代替红外相机作为数据源,提供给后续图像处理等系统,这样在调试过程中就可以不再启动红外相机了。FPGA逻辑设计单元是整个系统设计的核心,实现所有的时序配置和逻辑控制,通过FPGA编程可以实现红外相机时序的详细测量和记录、时序构造信号的输出以及所有外围芯片的逻辑控制等,FPGA芯片采用EP2C5-T144I8。相机构造信号发送芯片采用DS90-CR287,将FPGA输出的LVTTL电平格式信号转换为CameraLink电平格式信号,提供给图像处理等后续单元。串行数据输入电平转换芯片采用MAX3071,将LVTTL电平格式信号转为RS422电平格式信号,提供给后续系统。

2.2 FPGA逻辑结构设计

基于FPGA的相机时序构造设计中,FPGA是整个设计的核心器件,如图1所示,FPGA逻辑设计中包括PLL模块、时序测量/记录模块、场同步信号FVAL产生模块、行同步信号LVAL产生模块、数据有效信号DVAL产生模块以及渐变数据信号DATA产生模块。

PLL模块对输入的晶振时钟OS_CLK进行倍频/分频等处理,得到构造的像素时钟信号CLK。时序测量/记录模块接收真实红外相机的输出信号,采用FPGA编程和SignalTap工具相结合的方法对相机的时序进行详细测量,并记录形成相机时序文件,作为模拟时序产生的依据。场同步信号产生模块(FVAL_MAKE MODULE)以时序记录文件为依据,编程实现场同步信号输出。行同步信号产生模块(LVAL_MAKE MODULE)以时序记录文件为依据,编程实现行同步信号的输出。数据有效信号产生模块(DVAL_MAKE MODULE)以时序记录文件为依据,编程实现数据有效信号的输出。像素值信号即渐变数据产生模块(DATA_MAKE_MODULE)通过编程实现在行有效的情况下输出渐变数据,代替真实的像素值。

3 软件设计

基于FPGA的红外相机时序构造系统的软件设计主要实现了真实红外相机时序的详细测量及记录,时钟信号的处理以及根据测量得到的时序构造与真实相机时序一致的时序信号。

3.1 时序测量及记录

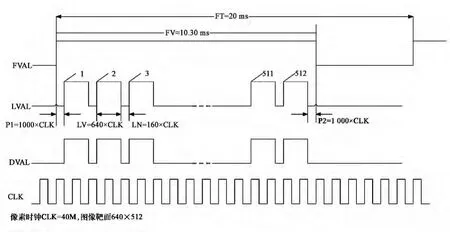

真实相机时序的测量是进行基于FPGA的红外相机时序构造的前提,测量产生的时序记录文件是进行后续时序构造程序的基础。图2以某红外相机的时序测量为例,给出经过时序测量后得到的时序记录文件示意图。

图2 某红外相机时序记录文件Fig.2 Sequence record file of an IR camera

如图2所示,相机的时序记录文件包括了像素时钟信号CLK、场同步信号FVAL、行同步信号LVAL以及数据有效信号DVAL的相关信息。像素时钟信号CLK由示波器测量得到,图中相机像素时钟为频率40MHz,占空比1∶1的连续信号。场同步信号FVAL包括场周期FT和场有效时间FV,场周期信号可以由示波器测得,图中场周期时间FT=20ms,场有效时间FV=10.30ms。行同步信号LVAL的测量需要采用FPGA编程和SignalTap工具结合测得,需要给出的行同步信息包括一场图像中包含的有效行数、行有效时间LV、行消隐时间LN、起始行信号距离场起始信号的时间P1以及结束行信号距离场结束信号的时间P2,图2中可见一场包含512行有效数据,LV=640×CLK,LN=160×CLK,P1=P2=100×CLK。数据有效信号DVAL的测量也需要采用FPGA编程和SignalTap工具结合测得,DVAL时序一般与LVAL信号时序相同。

3.2 时序构造

相机的时序构造是在已知相机时序文件的基础上,构造与其时序一致的输出信号,在进行调试等工作时,作为数据源提供给图像传输、图像处理等后续系统,以节省红外相机的实际开机时间。

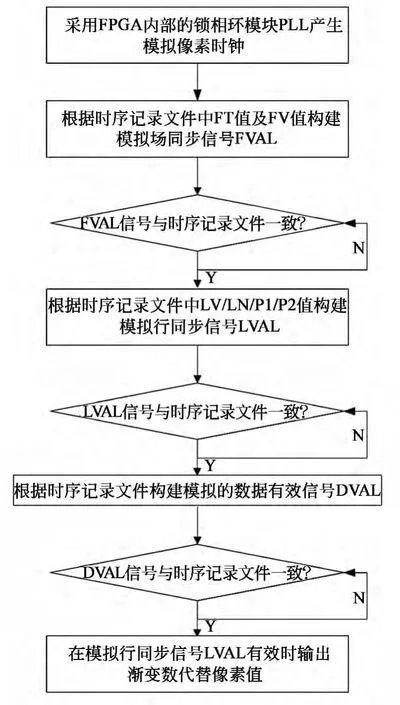

图3 基于FPGA的时序构造流程图Fig.3 Flow chart of the sequence conformation based on FPGA

时序构造软件设计中,首先采用FPGA内嵌的锁相环模块PLL对输入的晶振时钟OS_CLK进行处理,得到构造的像素时钟信号CLK;接着根据时序记录文件中场同步周期FT及场有效时间FV,对时钟信号进行计数处理,得到模拟的场同步信号FVAL;之后根据记录文件中P1/P2/LV/LN的计数值以及一行中包含的有效行数,以FVAL为基准,编程实现模拟的行同步信号LVAL的输出;之后根据数据记录文件构造数据有效信号DVAL,一般情况下,DVAL信号与LVAL信号是相同的;最后在LVAL信号有效的情况下输出渐变数,代替相机输出的像素值。图3给出基于FPGA的时序构造软件流程图。

在时序构造程序设计中,所有的测量值都以参数的形式在FPGA程序中体现,这样对于不同的相机只要根据时序记录文件修改相应的参数值即可,不用修改程序段,因此程序具有很强的可移植性。

3.3 具体程序设计

根据图3所示的时序构造软件流程图,程序设计主要包括时钟信号CLK产生模块、场同步信号FVAL产生模块、行同步信号LVAL产生模块、数据有效信号DVAL产生模块、渐变数据DATA产生模块以及SignalTap时序验证模块等。由于篇幅原因,这里以场同步信号FVAL产生模块为例,给出程序的具体设计。

首先根据输入时钟信号产生像素时钟信号,外部的输入时钟OS_CLK频率为50MHz,图2所示时序文件中相机像素时钟为40M,采用内部锁相环模块PLL对OS_CLK进行除5乘4处理,产生40M的像素时钟。图2所示,场同步信号FVAL周期为20ms,场同步有效时间约10.3 ms,根据公式(1)和公式(2)可以得到FT包括的时钟周期数K1和FV包括的时钟周期数K2。

式中:K1为场同步周期FT包括的时钟周期数,FT为场同步周期,TCLK为时钟周期;K2为场同步有效FV包括的时钟周期数,LV为行同步有效长度(及包括的时钟个数),LN为行消隐长度,Lnum为一场包括的行数,P1为行起始距离场起始的长度,P2为行结束距离场结束的长度。这样计算得到场信号FT包括(20×106)/25=800000个时钟周期,场同步有效FV包括(640+160)×511+640+1000+1 000=411 440个时钟周期。根据如上计算,可以通过编程对时钟信号进行精确计数,使得场同步信号持续800000个时钟周期,场同步有效持续411 440个时钟周期,场同步无效持续388 560个时钟周期。以场同步FVAL构造为例,给出如下程序段设计。

以上程序通过计数的方式实现了场同步信号FVAL的构造,行同步LVAL、数据有效信号DVAL等信号的构造程序与场同步信号FVAL的构造程序结构基本相同。

4 时序验证及实验

4.1 时序验证

按图3所示的流程图进行时序构造程序设计,输出模拟的相机时序信号,之后,要进行时序验证,若构造的时序信号与时序文件一致,则证明输出的信号时序正确,可以提供给后续的图像传输、图像处理等系统作为数据源。时序验证的方法是对输出的信号进行实际测量,与时序文件进行比较,场同步信号FVAL采用示波器测量,其他信号采用SignalTap工具回采的方法进行测量。图4给出采用SignalTap工具对构造的时序信号进行验证的视频截图。

图4 采用SignalTap工具验证时序构造信号Fig.4 Using SignalTap tool to validate the sequence construction signal

图4给出采用SignalTap工具验证时序构造信号的效果图,SignalTap文件以输出的时钟信号CLK为全局采样时钟,对输出的场同步信号FVAL、行同步信号LVAL以及数据有效信号DVAL进行测试。图4(a)显示出输出的行同步信号起始位置距离场同步信号起始位置参数P1为1 000个时钟周期;图4(b)显示出行同步信号有效参数LV为640个时钟周期,行同步消隐参数LN为160个时钟周期;图4(c)显示出行同步结束位置距离场同步信号结束位置参数P2为1 000个时钟周期。由图4可知,输出的构造信号时序与图2的时序记录文件完全一致,时序构造程序设计正确。

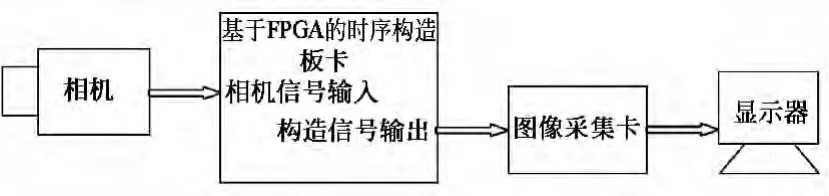

4.2 实验

在验证了时序构造程序正确的基础上,对输出的构造相机信号进行采集实验,实验组成框图如图5所示。如图5所示,试验中,相机信号输入时序构造板,进行时序测量,根据红外相机的真实时序构造与其时序一致的信号,输出给图像采集卡,图像采集卡对构造的时序信号进行采集,将图像显示在显示器上。

图5 构造信号采集实验结构框图Fig.5 Experiment structure map of the construction signal collection

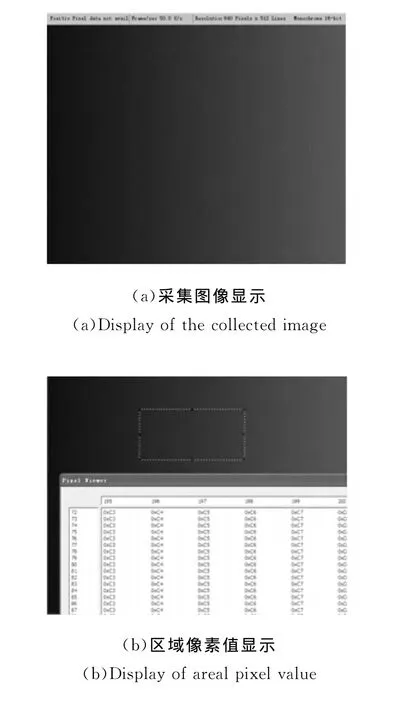

图6给出采集得到的显示图像。

时序构造板卡输出的场同步FVAL、行同步LVAL、数据有效DVAL及像素时钟CLK信号与相机的时序完全一致,像素值用渐变数代替。

图6(a)可以看出图像稳定显示,由于像素值是渐变数据,因此图像亮度也是渐变的,图像帧频显示为50Hz,靶面尺寸显示640×512;图6(b)采用Pixel Viewer工具显示虚线框区域的像素值,可以看出像素值为稳定的渐变数值。实验证明:基于FPGA的时序构造板卡输出时序与相机时序完全一致,可以作为数据源提供给后续系统,在调试时代替红外相机,以减少其开机时间。

图6 时序构造板图像输出采集效果图Fig.6 Collected image of the sequence construction board

5 结 论

基于FPGA的相机时序构造设计按照测量所得的红外相机时序文件,构造与相机时序信号完全一致的信号,为图像传输、图像处理等后续系统提供数据源,以进行调试和实验工作。实验以某红外相机为例,构造帧频为50Hz,像素时钟为40M,靶面尺寸为640×512,像素值为渐变数的输出信号,并进行图像采集。实验表明:采用构造的相机信号作为信号源可以满足图像传输、图像处理等系统的调试和实验要求,效果良好。在调试实验中采用构造的信号源代替实际的红外相机,大量减少了红外相机的开机时间,为项目节约成本,因此设计具有实际的工程应用价值。

[1] 熊文彬,蒋泉,曲建军,等.基于FPGA实现的视频显示系统[J].液晶与显示,2011,26(1):92-95.Xiong W B,Jiang Q,Qu J J,et al.Video display system based on FPGA [J].Chinese Journal of Liquid Crystals and Displays,2011,26(1):92-95.(in Chinese)

[2] 孙航,冯强,韩红霞.基于FPGA的红外序列图像动态压缩显示[J].液晶与显示,2011,26(8):551-554.Sun H,Feng Q,Han H X.Infrared sequence image dynamic compression display based on FPGA [J].Chinese Journal of Liquid Crystals and Displays,2011,26(8):551-554.(in Chinese)

[3] 宋振丰,李岩,于洋.数字图像注入式红外目标捕获跟踪训练仿真[J].中国光学与应用光学,2010,13(2):194-200.Song Z F,Li Y,Yu Y.Simulation for IR capturing and tracking train based on digital image injection[J].Chinese Journal of Optics and Applied Optics,2010,13(2):194-200.(in Chinese)

[4] 李满良,吴钦章.光电经纬仪CCD曝光中心测量系统的设计[J].光学精密工程,2013,21(5):1304-1310.Li M L,Wu Q Z.CCD exposure center measuring system for photoelectric theodolite[J].Opics and Precision Engineering,2013,21(5):1304-1310.(in Chinese)

[5] 许文海,吴厚德.超高分辨率CCD成像系统的设计[J].光学精密工程,2012,20(7):1603-1610.Xu W H,Wu H D.Design of ultra-high resolution CCD imaging systems[J].Opics and Precision Engineering,2012,20(7):1603-1610.(in Chinese)

[6] 冉峰,杨辉,黄舒平.面阵CCD彩色视频图像实时采集系统的设计[J].光学精密工程,2010,18(1):273-280.Ran F,Yang H,Huang S P.Design of real-time color video capture system for area array CCD [J].Opics and Precision Engineering,2010,18(1):273-280.(in Chinese)

[7] Levine P A,Saucer D J,Shallcross F V.High frame rata multi-port CCD Image and camera[J].SPIE,1992,1952:257-267.

[8] LIX Z,YU Z Y,SHANG F.Multifunction image target generator[J].Experimental Technology and Management,2002,19(4):36-37.