基于MAX+PLUSII模块化设计的智力竞赛抢答器

2014-04-29黄云连恒辉

黄云 连恒辉

摘 要: 設计了一款造价低,体积小,操作简单,适用性广的抢答器。该抢答器是基于MAX+PLUSII软件,在FPGA芯片上设计的,可实现多人智力竞赛抢答。

关键词: 智力抢答器; 多人抢答; MAX+PULSII软件; FPGA芯片

中图分类号:TP211+.5 文献标志码:A 文章编号:1006-8228(2014)01-29-03

0 引言

本文所介绍的智力竞赛抢答器,具有广泛的适用性。通过改变硬件电路接线,施加时钟信号频率,以及进行软件调试,使之可以灵活改变抢答者人数、回答问题时间和蜂鸣提醒时间等。本文选取一个实例介绍其原理。

1 开发条件

1.1 知识基础

⑴ 熟练使用MAX+PLUSII软件。

⑵ 学习数字电路基础课程。

⑶ 了解《GW48-CK EDA实验开发系统简介》,了解连接方式。

1.2 所用原件

⑴ GW48系列EDA/SOC验开发系统(提供有目标芯片FPGA-型号EP1K30TC144-3、数码显示器、二极管、三极管、钮子开关、晶振等资源)。

⑵ 电路设计建议采用下列器件:74175、74147、74192、7448、ANDX、ORX、NOT等。

2 实现的功能

⑴ 有4路抢答;

⑵ 数字显示抢答组别;

⑶ 由主持人复位后方可抢答;

⑷ 声音提示已有人抢答;

⑸ 抢答成功后,有60秒的回答问题时间,并显示倒计时;

⑹ 最后五秒蜂鸣提示;

⑺ 抢答只需一次按键即可,无需一直按住。

3 电路基本原理

3.1 抢答控制

电路采用74175(4D触发器),其原理图如图1所示,四个D输入分别为四个抢答者开关(P1,P2,P3,P4),CL为主持人复位开关,主持人按动开关CLRN接0, 芯片置0,此时各抢答者输出均为低电平,抢答开始。此后,若上升沿有人先抢答,假定为P1,则CLK出现高电平,产生上升沿,则1Q输出高电平,且不管接下来各抢答者抢答情况如何,由于1Q=1,CLK始终为1,无上升沿,因此各输出端保持当前状态。只有CL开通,芯片置0,才能改变状态,再次抢答。

3.2 数字显示抢答组别

为了显示抢答组别,采用74147(优先编码器)对输出编码,其原理图如图2所示。由于74147输入/输出为低电平有效,在其输入/输出均加入了非门,所以能使其正确的显示组别。

3.3 回答问题倒计时

实验中,倒计时设定为60s,采用的是74192(十进制计数器),因此需两块芯片联合使用实现60进制计数。原理图如图3所示,左边是十位,右边个位。倒计时是在有人抢答成功开始计数的,将抢答者输出做'或'运算后,分别接入两计数器的置数端(十位置6,个位置0),一旦有抢答者抢答,LDN高电平,不置数,倒计时开始。采用减法计数,因此将1HZ的时钟信号CP接上个位的DN,同时将个位的BON接十位的DN。在此需说明一个问题:BON是低电平有效,当计数一轮后有借位时,输出为低电平,有读者会有疑问:为何不把其先反相从而产生上升沿再接入十位的DN?这是因为,BON输出值还跟CP有关。设当CP上升沿到来时,个位计数器数到0000,由于CP上升沿后为高电平,BON为高电平,此后CP变为低电平,BON变为低电平,CP下个上升沿一到,计数器变为1001,BON同时也变为高电平,此时给十位计数器DN一个上升沿,十位计数器计数,实现了十位、个位同时变化。相反,如果将BON先反相,则十位会先于个位变化。最后当60s计数完毕之后,为了停止计数,将十位计数器BON反相后分别接两个计数器的CLR清0。

3.4 抢答蜂鸣器提示

结合计数器设计了蜂鸣器提示,其原理图如图4所示,图4中计数器为十位计数器,没人抢答时计数器置6。S2,S3均为1,当有人抢答成功时,四输出'或'变为1,蜂鸣器响,同时计数器停止置数,在CP上升沿到来时十位计数器变为5,同时蜂鸣器停止响,蜂鸣器响的时间为抢答开始时到CP下个上升沿的时间。

3.5 倒计时最后5秒提示

倒数时最后5秒十位为0000,个位为0101,0100,0011,0010,0001时蜂鸣器均需要响,个位为1001,1000,0111,0110,0000,均不能响(0000不能响的原因是倒计时完后一直清0)。注意表达式:G2G3+G4,当个位为5,4,3,2,1,0时表达式恒为0,个位为9,8,7,6时表达式恒为1,因此将十位的S3,S2,S1和G2G3+G4经'或非'运算后可实现5,4,3,2,1,0蜂鸣器响,为了使0不响,可以使G1,G2,G3,G4'或非'后与S3,S2,S1,G2G3+G4一起'或非',可以实现倒数5秒输出为1,为了让蜂鸣器能响5下,将上面得到的输出与CP'与'后可以让蜂鸣器在最后5秒响5下,其原理图如图5所示。

3.6 各分电路组合

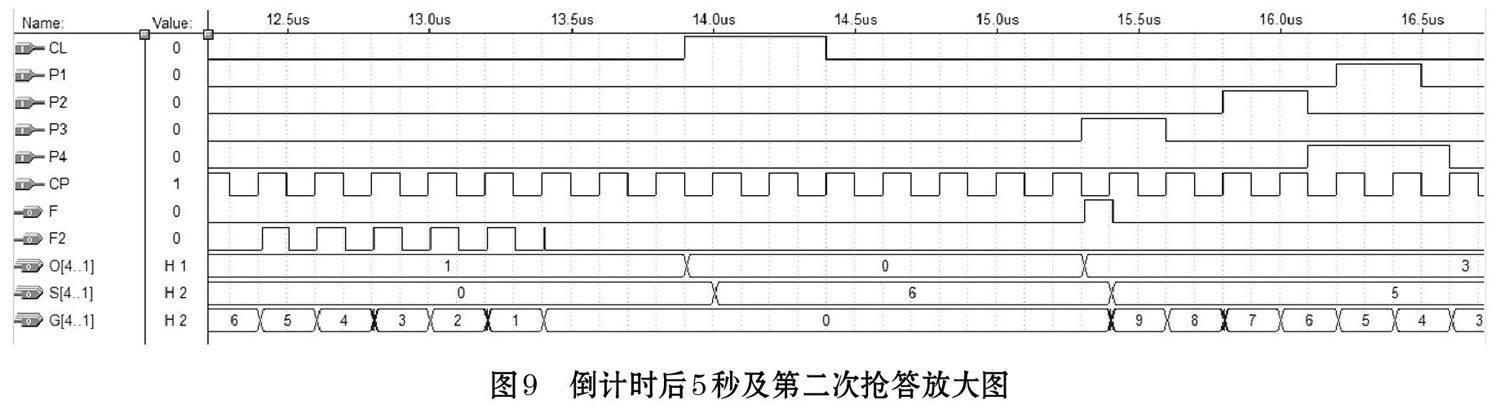

最后一步是将各功能电路组合在一起。系统总的电路原理图如图6所示。

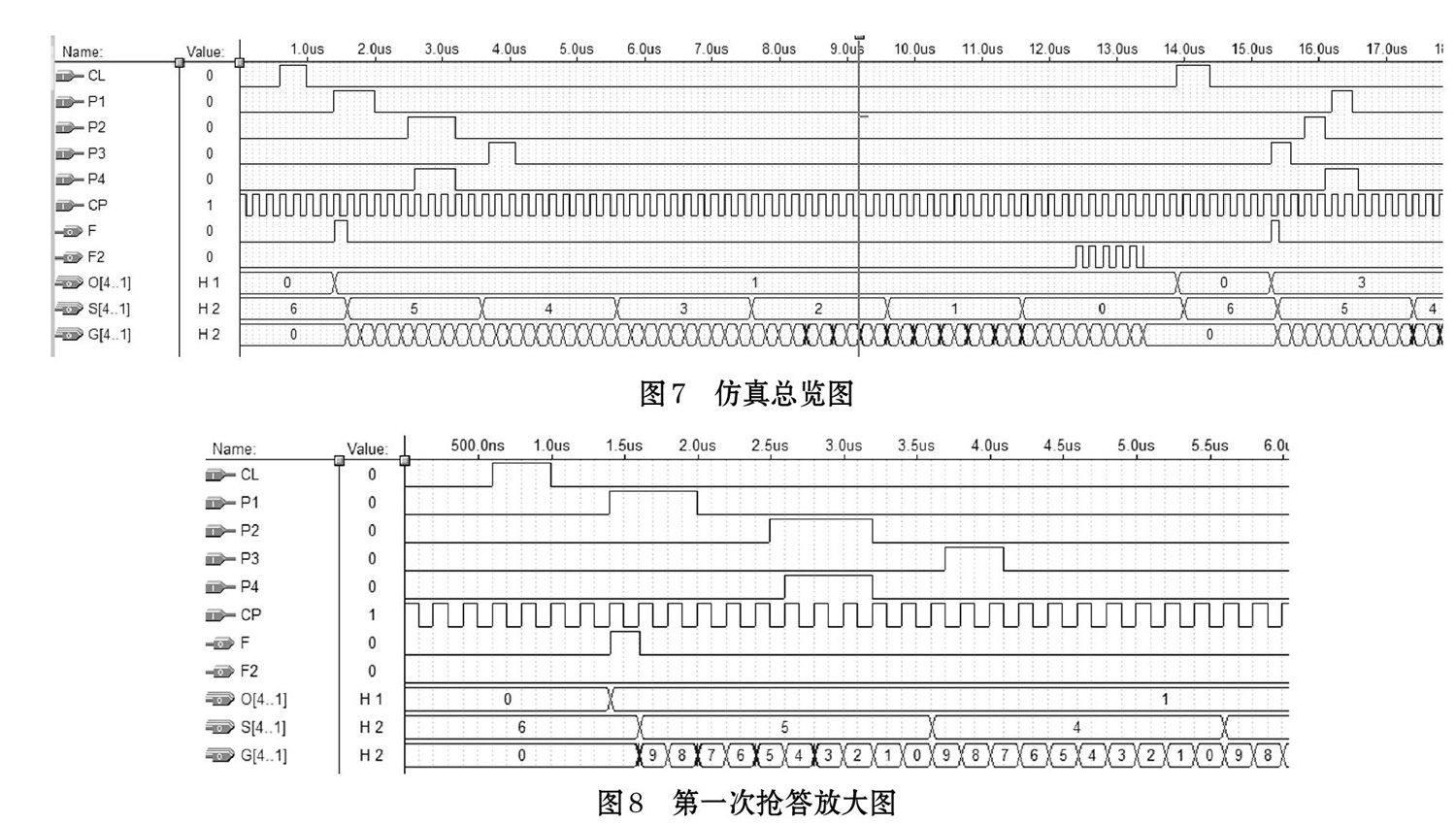

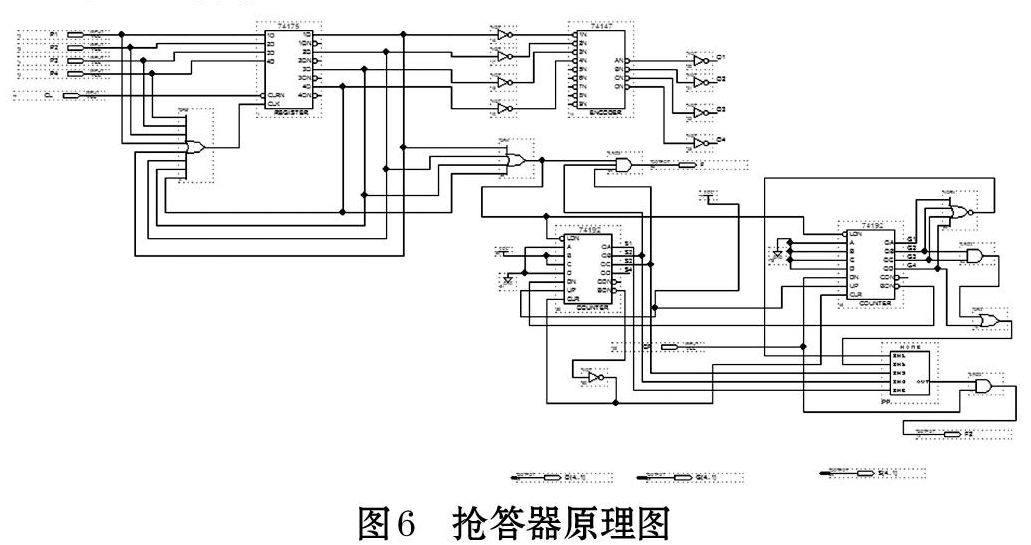

4 仿真与调试

波形图的仿真图如图7,图8,图9所示,仿真图中P1,P2,P3,P4为抢答者波形,CL为主持人波形,CP为时钟波形,F为抢答提示蜂鸣器波形,F2为抢答倒计时5秒提示蜂鸣器波形,S为倒计时十位数波形,G为倒计时个位数波形。仿真图中主持人按了两次复位键,第一次P1抢到,且F提示蜂鸣器响,此后60秒倒计时后能停止计数,且最后5秒F2提示蜂鸣器响了5下(在倒计时完后有非常短暂的毛刺,其影响可以忽略),主持人第二次复位后,仍可以正常抢答,此次被3抢到。仿真结果与设计的理想结果相符。

5 结束语

通过仿真与实验,验证了本智力抢答器设计的正确性与可行性;并且可以通过改变电路参数和结构,改变回答倒计时时间和最后蜂鸣时间,使本智力抢答器具有灵活性,能适用于不同的场合,使产品具有更广的市场。与目前市场上流通的抢答器比较,该抢答器显得更加灵活,造价更低,适用于一些组装爱好者及中低消费人群使用。今后还需要对该智力抢答器添加更具时代元素的功能,以及实现更高的可靠性。

参考文献:

[1] 周跃庆.MAX+PLUSII操作指南[M].自动化学院,2008.

[2] 周跃庆.数字电子技术基础教程[M].天津大学出版社,2006.

[3] 王志鹏,付丽琴.可编程逻辑器件开发技术 MAX+PLUSII[M].国防工

业出版社,2005.

[4] 卢飞跃.红外遥控多路抢答器的设计[J].番禺职业技术学报,2003:

59-68

[5] 马轲瀛.八路数字抢答器系统[J].华商,2007.30(9):167-172

[6] 李燕,宋芳.多路抢答器设计[J].湘潭师范学院学报,2004.2.