基于DDS技术相位可调的低频信号源硬件实现

2014-04-19陈国童

陈国童

(宁德师范学院 物理与电气工程系,福建 宁德 352100)

基于DDS技术相位可调的低频信号源硬件实现

陈国童

(宁德师范学院 物理与电气工程系,福建 宁德 352100)

本文提出了一种新型相位可调的低频信号源设计方法.采用DDS(Direct Digital Synthesis)技术产生数字式移相正弦波信号.信号生成由CPLD实现,主要包括相位累加器和波形查找表.以单片机为控制芯片,产生频率控制字和相位控制字传送给CPLD,可大幅减轻对单片机速度的要求.

DDS;单片机;CPLD;低频信号源;相位调节

1 引言

在科学研究、生产实践中,常常需要产生稳定的重复波形,如正弦波或者方波.在许多情况下,要求产生波形的频率稳定,能够准确调节,还要求能够产生多路输出信号,这些信号之间的相位保持确定的关系[1].目前使用的信号发生器绝大部分都是由模拟电路构成,这会使频率达数百兆赫兹,在高频范围内其频率稳定性与可调性较好.但是用于低频信号输出时,其需要RC值很大,大电阻、大电容在制造上很困难,参数准确度难以保证[2,3],而且体积大,漏电损耗也大,加上传统的模拟移相(如:阻容移相,变压器移相等)有许多不足[4].对此,本系统设计了一种基于DDS技术相位可调的低频信号源.通过结合单片机和CPLD技术,利用DDS的方法来实现频率、幅度、相位均可调节的低频信号源实现方法.

2 系统组成原理

基于DDS技术相位可调的低频信号源系统框图如图1所示.

图1 系统组成框图

利用CPLD、单片机与电子线路技术设计一个可调相位低频信号源.单片机主要实现输出信号的频率、相位差和幅度的设置,输出信号的频率、相位和幅度的显示,向CPLD提供频率控制字和相位控制字.CPLD主要实现DDS技术,利用CPLD中相位累加器输出的数据作为波形存储器的相位取样地址,通过相位累加器输出的数据读取波形存储器中的数据,再经过模/数转换电路、幅度调节电路、低通滤波器电路,最后产生两路频率、相位差和幅度都可调的正弦信号.

2.1 DDS技术原理

DDS技术将输出波形的一个完整周期的幅度值按顺序地存放在波形存储器中,通过控制相位增量产生频率、相位可控制的波形.DDS电路包括基准时钟、相位增量寄存器、相位累加器、波形存储器、D/A转换器和低频滤波器(LPF)等模块.DDS的基本原理如图2所示[5].

图2 DDS的基本原理图

图中,相位增量寄存器用于寄存频率控制数据,相位累加器能够完成相位累加的功能,波形存储器存储波形数据的一个完整周期幅度值数据,D/A转换器实现数字量转换成模拟量的功能,它将数字量形式的波形幅值数据转化为所要求合成频率的模拟量形式信号,低通滤波器起到滤除高次谐波分量的功能.为保证合成信号的精确度,整个系统必须在统一的时钟下工作.累加器由N位加法器输出的累加寄存器级联构成.每来一个时钟脉冲fcp,加法器将频率控制字M与累加寄存器输出的累加相位数据相加一次,把相加后的结果送至累加寄存器的数据输入端.累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲作用下继续与频率控制字相加.所以,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加.由此,相位累加器在每来一个时钟脉冲输入时,把频率控制字M累加一次,相位累加器输出的数据就是合成信号的相位,当相位累加器累加满量时就会产生一次溢出,完成一个周期的动作,这个周期就是DDS合成信号的周期,累加器的溢出频率就是DDS输出的信号频率.

相位累加器中的数据设为24位,把输出数据的前11位作为波形存储器的相位采样地址,当相位累加器加一个频率控制字(频率控制字也为24位),通过相位累加器数据的前11位读取波形存储器中的数据,这样就可把存储在波形存储器内的波形抽样值(二进制编码)读出,完成相位到幅度值的转换.波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅度值转换成所要求合成频率的模拟量形式信号.低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号.

DDS在相对带宽、频率转换时间、高分辨率、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能.DDS输出的信号频率可以由下式给定:

式中:f0为输出信号频率,M为频率控制字,fcp为系统时钟频率,△f为信号分辨率,N为相位累加器的位数.

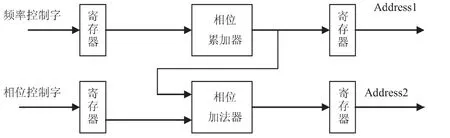

通过分别设定频率控制字M、相位累加器的位数N和系统时钟频率fcp,就可以按要求产生任意频率的输出信号.基于DDS技术的数字式移相信号发生器的主要模块如图3所示.

图3 DDS技术的数字式移相信号发生器主要模块框图

2.2 DDS系统参数确定

2.2.1 确定系统时钟频率fcp

不妨设输出信号最高频率为fmax、最高频率fmax下的最少采样点数为Smin,则有

由式(2)确定系统时钟频率fcp的下限值.同时又要满足输出信号频率分辨率计算公式

fmax·Smin=1kHz×2048=2.048MHz,fcp≥2.048MHz,为了方便获得时钟脉冲,取fcp=24MHz.

2.2.2 确定相位累加器的位数N

因为信号频率分辨率△f=fcp/2N,所以2N=fcp/△f,即2N=10MHz/20Hz=24×106/10=10×105=2400000

因为220=1048576,221=2097152,而220﹤2400000﹤221,所以,相位累加器的位数N的最小值应为21bit.

一方面,N的最小值21bit已大于2Byte,另一方面,考虑适当提高系统的频率分辨率,所以综合这两个方面,取N=24.由此可见,系统的频率分辨率为△f=24MHz/224=1.4304Hz.

此时输出信号的频率分辨率为1.4304Hz,可满足精度的设计要求.

2.2.3 确定频率控制字M的位数

由式(1)可以求得频率控制字为

由上式可知,频率控制字M的最大值出现在输出信号频率f0max=1kHz的时候,则Mmax=224×1× 103/24000000=699.050667

由于29=512,210=1024,而29<699.050667<210,因此取频率控制字M的位数为10bit.

系统中的24bit相位累加器实现对频率控制字的累加,为了实现这种累加而将10bit的频率控制字扩展成24bit,扩展的具体方法是在上述10bit频率控制字前面(左边)添加14个逻辑0即可.

2.2.4 确定波形存储器的地址位数W

本系统决定存储信号一个周期的幅度值采样点数为2048,因此波形存储器的地址位数W=11.

2.2.5 确定量化字长D

信号一个周期的幅度值采样量化字长D对输出信号的失真度影响很大,本系统决定取量化字长D=8bit.这样的话,系统中的D/A转换器的字长也应该是8bit.

2.2.6 确定相位控制字K的位数

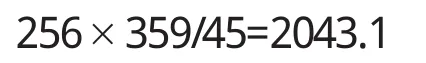

如果“相位加法器”采用10bit加法器实现,既以“相位累加器”的输出结果之高10位,作为被加数,则有360︰2048=θ︰K

则

式中:θ是相位差,K是相位差为θ时对应的相位控制字.K的最大值出现在θ取最大值359°时,即

则相位控制字K的位数取11bit就能满足设计任务关于移相的要求(分辨率为0.2°,移相范围是0~359°).

若“相位加法器”采用24bit加法器实现,则上述11bit的相位控制字应扩展成24bit,具体扩展方法是在上述11bit相位控制字后面(右边)添加13个逻辑0即可.

3 部分主要电路实现

3.1 幅度调节电路设计

电路由DAC0832和LM324N组成,通过控制DAC0832的基准电压VREF来控制输出信号的幅度.通过单片机发出的数字量不同,来控制调幅的这块DAC0832的输出电流Iout1,使其输出电压改变.DAC0832的输出端V0作为后两块D/A转换器的DAC0832的基准电压VREF,所以通过基准电压VREF的大小可以控制后两块DAC0832输出端V0的大小.因此可实现幅度调节的功能.幅度调节电路如图4所示.

图4 幅度调节电路

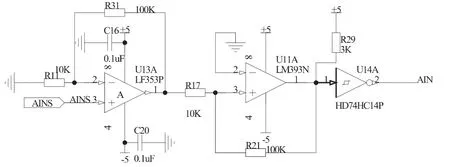

3.2 相位调节电路设计

相位调节电路可以用来检测两路输入正弦波的相位差.电路有两路正弦信号输出通道,通过单片机提供的相位控制字调节另一路信号的相位,从而调节两路信号的相位差,当第一路信号调节好频率输出时,使相位控制字与其相位累加器中的数据相加,可以改变相位累加器前11位的数据,从而改变读取波形存储器中的数据,实现了改变第二路信号的相位.电路由同相放大电路、迟滞比较器和反向器构成,其实现电路如图5所示.

图5 相位调节电路

3.3 RS232电路设计

Max232产品是由德州仪器公司(TI)推出的一款兼容RS232标准的芯片.该器件包含2驱动器、2接收器和一个电压发生器电路提供TIA/EIA -232-F电平.该器件符合TIA/EIA-232-F标准,每一个接收器将TIA/EIA-232-F电平转换成5-V TTL/CMOS电平.每一个发送器将TTL/CMOS电平转换成TIA/EIA-232-F电平.计算机与单片机的串行通信通过MAX232电路来实现,单片机通讯电平是TTL0-5V,计算机是-12V,通讯电平不同需要转换.MAX232电路如图6所示.

图6 RS232电路

3.4 频率调节设计

相位累加器中的数据设为24位,把前11位作为波形存储器的地址,用芯片2716作为波形存储器(2716的内存为2K,地址位为11位,所以正好存储2048的采样点数据),后13位起始时为0.晶振用24M的,所以来一个脉冲的时间间隔为1/(24×106)秒.

当相位累加器加一个频率控制字(频率控制字也为24位),就这样通过相位累加器数据的前11位读取波形存储器中的数据,通过频率控制字的大小来控制读取波形存储器中数据及两个采样点之间的时间间隔,从而控制产生信号的频率.如果频率控制字很小,相位累加器的后13位很长时间加不到前11位,前11长时间不变,所以读取波形存储器中数据长时间不变,因此频率就很小.如果频率控制字很大时则相反.因此实现了频率调节的功能.

4 结束语

为实现相位、频率、幅度均可调的低频信号源,提出了一种采用DDS技术的低频数字信号源设计方法.结合单片机和CPLD实现对信号源的控制,介绍了DDS技术的基本原理和参数配置方法,主要介绍了系统的相位调节电路、幅度调节电路和通信接口电路的实现方法,同时介绍了频率调节的基本原理,通过对系统的硬件配置实现了相位、频率、幅度均可调的数字电源设计.

〔1〕薛延侠,赫建国.CPLD实现DDS信号源的设计[J].现代电子技术,2005,210(19):73-76.

〔2〕彭建亮,朱凡.基于单片机和CPLD的数字式移相信号发生器的设计[J].仪器仪表用户,2005,12 (3):19-21.

〔3〕廖建庆,梁国祥.基于DSP的高压容型电气设备介质损耗测量仪设计[J].陕西科技大学学报(自然科学版),2012,30(4):102-105,109.

〔4〕王庆,刘涤尘.基于CPLD的高精度可程控多路信号源[J].仪表技术与传感器,2005,(3):36-38.

〔5〕李小波,孙志勇,刘春生.基于CPLD和单片机的低频信号源设计[J].仪表技术与传感器,2005,(11):46-48.

TN98

A

1673-260X(2014)02-0042-03