集成电路反向设计解析

2014-04-14姚森宝滕谋艳

姚森宝 滕谋艳 陈 璐

(深圳创维半导体设计中心有限公司,广东 深圳 518108)

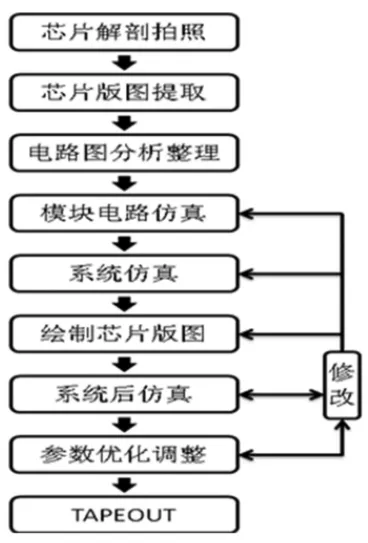

1 反向设计流程

反向设计流程见图1所示,主要就是把待分析芯片转换成电路图和版图的过程。

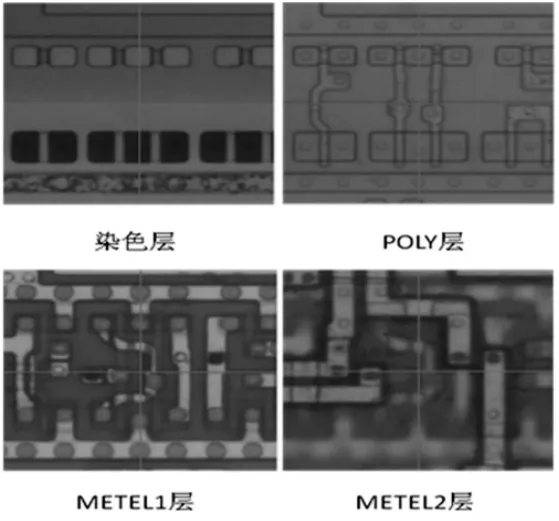

1.1 芯片解剖拍照

我们所看到的照片图形是氧化层刻蚀形成的轨迹。每个物理层看到的图形就是芯片通过解剖、染色、去层后得到逆向设计所需的图形信息,然后用光学显微镜摄取芯片图形信息再进行拼接对准。国内外有多家能够提供完整解剖和电路提取的反向设计服务的公司。图2所示就是某反向设计服务公司将芯片解剖拍照后的数据。

图1

图2

1.2 芯片网表提取

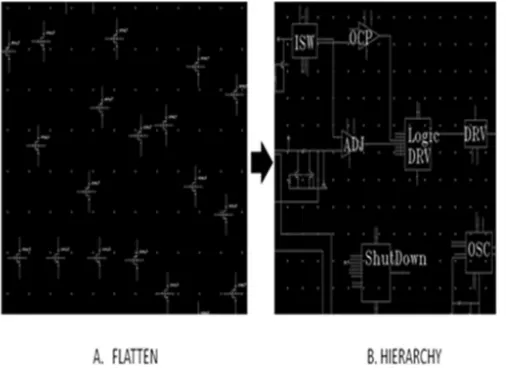

因为反向设计是一种自底向上的设计方法,所以芯片网表数据的提取质量显得尤其重要,初始数据的正确率直接影响电路整理、分析、物理验证。为了得到高准确率的网表,一般会安排两组工程师分别独立对网表数据进行提取。在两组工程师完成网表提取后分别进行电学规则检查以提高正确率,最后再进行网表对比验证(SVS)。图3为已经提取完成的部分芯片网表。

1.3 芯片电路分析整理

将通过验证的网表通过EDIF、VERILOG、SPICE等格式导入EDA设计工具进行电路图的分析整理。图3左边为网表通过EDIF格式导入,我们得到的是一个平层的网表数据,电路整理是把平层的电路进行层次化整理,形成一个电路的层次化结构,以便理解设计者的思路与技巧。图3右边所示为经过整理的电路图。

图3

图4

1.4 芯片电路仿真

根据新的工艺调整电路器件参数,将已经层次化的电路图,通过仿真工具例如Hspice、Spectre、Hsim等EDA工具对电路模块功能进行仿真验证。

1.5 芯片版图绘制

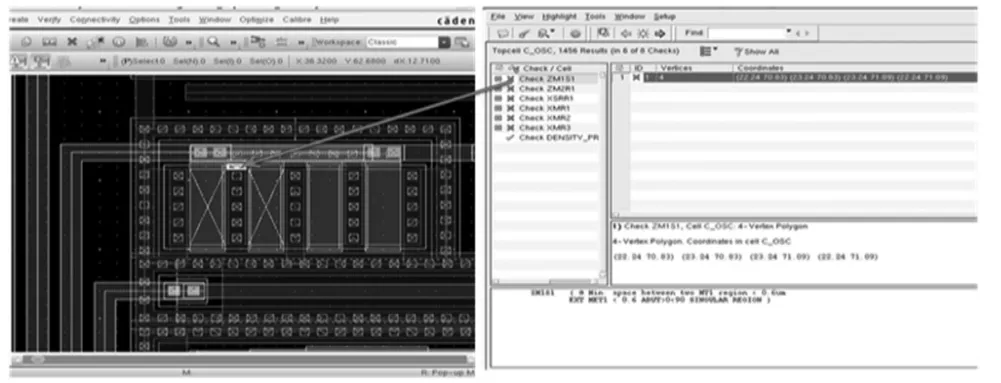

根据新的工艺文件绘制通过功能仿真验证的电路版图,使用Dracula、Assura、Calibre(图 5)等软件进行 DRC、LVS、ERC 验证。

图5

1.6 系统后仿真

完成版图总体布局布线后,用EDA工具进行寄生参数提取把提取的网表进行仿真验证,并将结果与前仿真结果做对比。对影响电路性能的寄生参数进行电路或者版图的调整。最后优化版图及数据TAPEOUT。

2 总结

本文浅析了集成电路反向设计流程,从实例中列举说明反向设计流程,介绍每一个步骤主要的实现方法。不少人认为集成电路反向设计已经严重影响微电子产业的发展,其实不然,不同工艺的设计规则要使其兼容需要花大量的时间修改。反向并不只意味着抄袭,在原有的电路结构上理解分析以及优化后最终实现相同的或更优的功能电路。

[1]于鹏,杜娇,游涛,谢学军.集成电路反向工程知识产权问题探析[J].中国集成电路,2010(11).