基于FPGA的IIC总线控制器设计

2014-04-01,

,

(中原工学院,郑州 450007)

IIC总线是双向、两线、串行、多主控接口标准,具有总线仲裁机制,适合在器件之间进行短距离、非经常性的数据通信,由于其使用两线的硬件接口简单,在微电子通信控制领域被广泛应用[1-2].现场可编程门阵列(FPGA)使用专用的集成电路,时序控制能力较强,处理信息的速度非常快,含有大量软核,方便系统二次开发,在通信领域的应用快速、灵活.为充分利用FPGA的逻辑资源,提高硬件系统的集成度,将IIC控制器嵌入FPGA内,实现DSP的高速异步存储器接口到IIC总线接口的转化.

1 IIC控制器系统设计

1.1 IIC接口及通信协议

IIC总线包括双向数据线SDA和时钟线SCL,分别通过上拉电阻连接到正的电源电压,实现全双工同步数据传送[3].

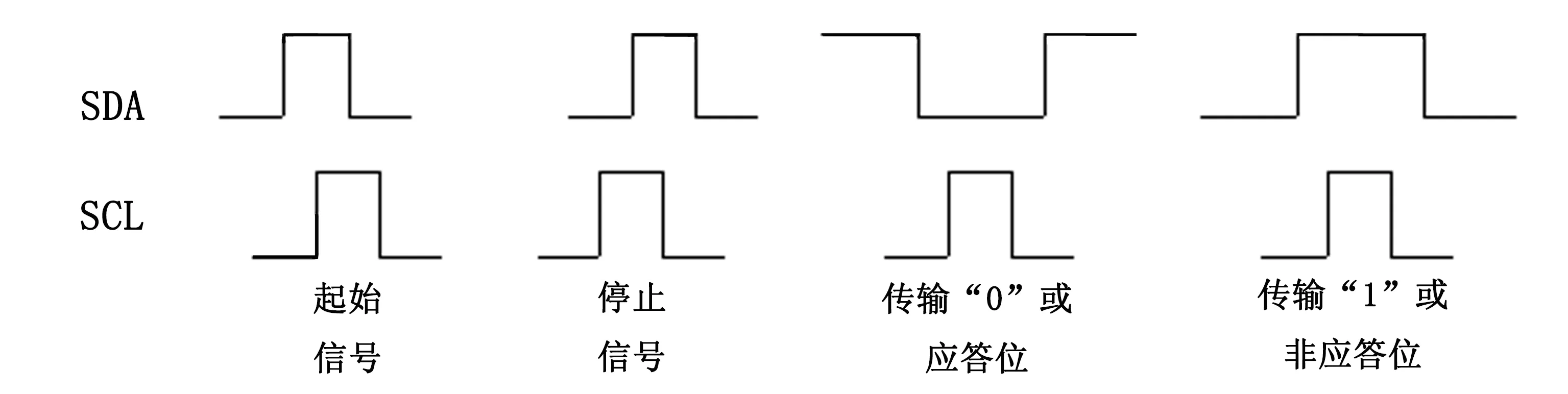

IIC通信协议是基于起止状态识别的.起始信号表现为在SCL高电平时SDA线从高到低,停止信号则表现为在SCL高电平时SDA线从低到高.应答信号是在SCL高电平时SDA为低电平,非应答信号相反,表现为在SCL高电平时SDA也为高电平.数据传输“0”和“1”时,与发送应答位和非应答位时序图相同,如图1所示.在其他任何时刻,只有SCL在低电平期间,SDA状态才能发生变化,否则,SDA上的数据必须保持不变[3].

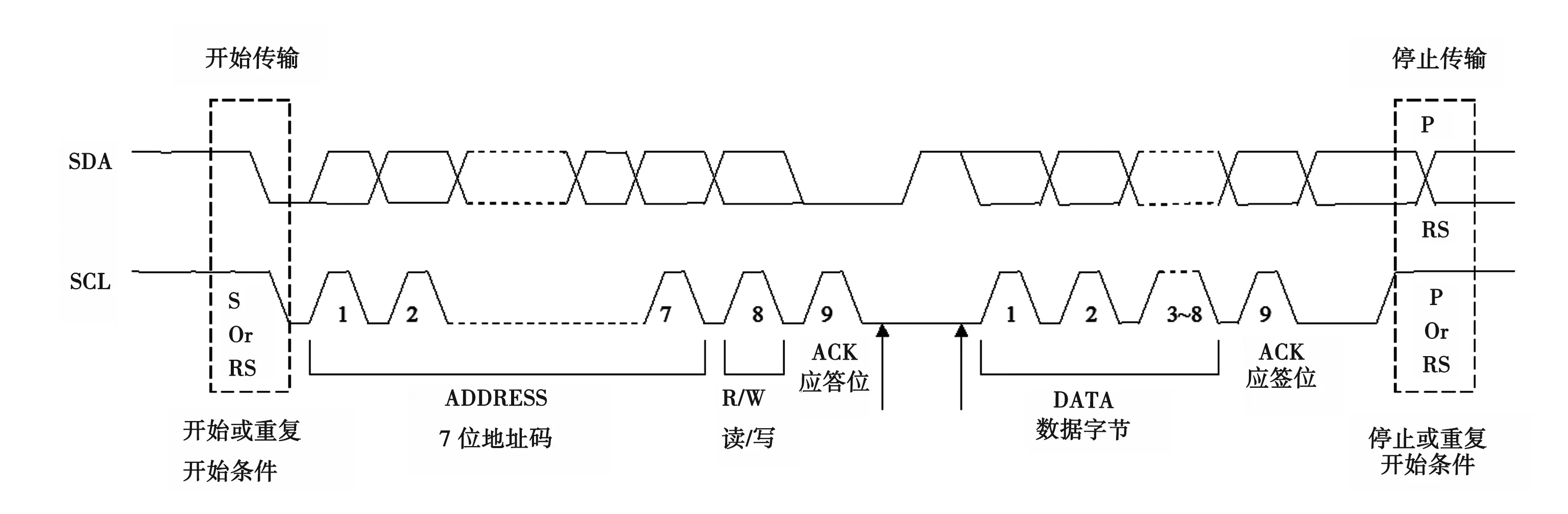

在一个起止状态之间,数据字节数没有限制,但每个数据字节必须得到确认.确认状态时,在SDA上每一个8位字节后面的第9位用低电平表示.图2表示一个完整的数据传输过程.IIC发送起始信号后,从器件的7位寻址地址和1位读写标志位R/W被发送(当R/W为0时,表示由主器件向从器件写数据;当R/W为1时,表示由主器件向从器件读数据),有应答信号后,开始传送数据,直到发送停止信号.数据是以字节为单位的,每发送一个字节就要检测SDA线上的应答信号,有则继续发送,否则就停止发送数据[4-5].

图1 IIC总线SDA与SCL时序划分

图2 完整的数据传输过程

写通讯过程为:①主器件在检测到总线空闲的状况下,发送一个START信号掌管总线;②主器件发送一个地址字节(包括7位地址码和1位R/W);③当从器件检测到总器件发送的地址与自己的地址相同时,发送一个应答信号(ACK);④主器件收到ACK后开始发送第一个数据字节;⑤从器件收到数据字节后发送一个ACK表示可以继续发送数据或进行其他操作;⑥主器件发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线.

读通讯过程:①主器件在检测到总线空闲的状况下,发送一个START信号掌管总线;②主器件发送一个地址字节(包括7位地址码和1位R/W);③当从器件检测到总器件发送的地址与自己的地址相同时,发送一个应答信号(ACK);④主器件收到ACK后释放数据总线,开始接收第一个数据字节;⑤从器件收到数据字节后发送一个ACK,表示可以继续传送数据或进行其他操作;⑥主器件接收完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线.

1.2 IIC控制器核设计

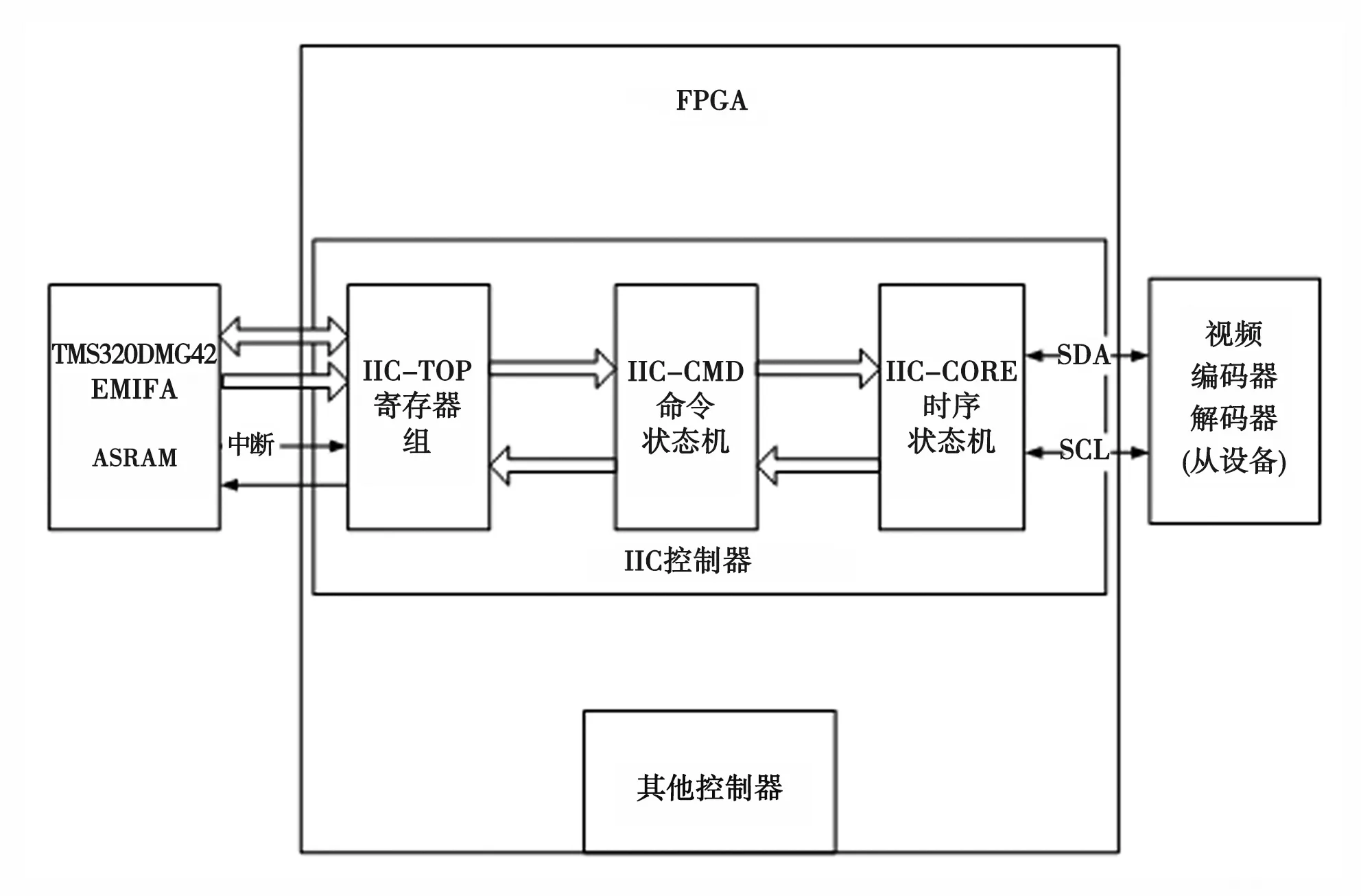

本文设计的IIC控制器核应用在基于DM642的图像采集与显示系统中,采用自顶向下设计方法.控制器核顶层设计分为3个模块:IIC_TOP模块、IIC_CMD模块和IIC_CORE模块.系统框图如图3所示.

图3 系统框图

IIC_TOP模块是顶层管理模块,主要任务是接收DSP发来的控制信号、命令及数据,发送从设备读出的数据和确认位到DSP,实现IIC控制器核与DSP的中断通信机制,并提供当前IIC控制器核的工作状态,把DSP发出的命令字信号送到IIC_CMD模块.IIC_CMD模块功能是把从IIC_TOP模块接收到的命令字信号传给IIC_CORE模块,IIC_CORE模块将这些命令字信号译码后,再将译码信号传回IIC_TOP模块.

2 IIC控制器状态机设计

本设计把控制器从逻辑上分为两个状态机,分别称为命令状态机和时序状态机,其中,命令状态机用于管理IIC总线上的命令状态,并实现IIC总线读、写操作命令状态的转移过程;时序状态机用于实现IIC总线启动、停止、读、写、确认等命令的具体时序关系.

2.1 命令状态机

命令状态机IIC_CMD模块的主要功能有两个:一是把IIC_TOP模块发送的开始(START)、写(WRITE)、读(READ)、停止(STOP)四个命令信号转化为命令码,发送到IIC_CORE模块;二是实现从器件接收到的数据串在DSP发出并转换.命令状态转移关系如图4所示.

图4 命令状态转移关系图

系统复位后,进入空闲状态IDLE,然后判别命令信号STARTREADWRITE:①若是START命令,则进入START状态,之后根据命令信号READWRITE分别转移到READ或WRITE状态进行数据的读或写,当8个字节传输完毕后,转移到应答状态ACK,之后根据命令转移到STOP或IDLE 状态;②若是READ命令,则进入READ状态,当8个字节传输完毕后,进入应答状态ACK,之后根据命令转移到STOP或IDLE 状态;③若是WRITE命令,则进入WRITE状态,当8个字节传输完毕后,进入应答状态ACK,之后根据命令转移到STOP或IDLE 状态.

2.2 时序状态机

时序状态机IIC_CORE模块负责与视频编码器、解码器的IIC接口进行连接,实现IIC总线信号SCL和SDA的开始(START)、停止(STOP)、读(WRITE)、写(READ)、应答(ACK)等具体操作的时序关系.根据时序,将它分成16个状态,时序状态转移关系如图5所示.

图5 时序状态转移关系图

时序状态机将命令状态作了细分,进入到各个命令状态后对各个子状态进行数据处理.每种操作包含 IDLE、a、b、c、d 等5个部分,其中 STOP 命令只包括 IDLE、a、b、c等4个部分.

3 系统仿真与测试

本设计采用Quartus II 9.0开发软件,对系统进行综合、适配、仿真.对IIC控制器进行仿真调试,图6所示是时序状态机仿真结果,图7所示是总线写数据过程的仿真结果.

将WRITE信号设为高电平,启动写数据传输,同时确定START信号是否为高,若为高,则进入开始状态,开始信号变为低电平时,开始写数据传输.

仿真结果为SDA~result、SCL~result.传输数据的开始信号到来后,在SCL~result为高电平期间,SDA~result出现一个下降沿,接着开始传输数据,到CMD_ACK有一个脉冲,结束一个字节的传输.当数据传输结束后,接收到STOP信号,这是通信停止和IIC总线传输数据的结束信号,此时SCL~result为高电平,SDA~result出现一个上升沿.结果显示了IIC总线的协议功能,证明了设计的正确性.

4 结 语

本文基于IIC控制器在DM642图像采集与显示系统中的应用,从状态机的角度出发,采用VHDL语言,设计完成了IIC总线控制器核,并进行了时序仿真和测试,结果表明本次设计的IIC控制器核满足接口协议的时序要求.

参考文献:

[1] 刘欲晓,方强,黄宛宁,等. EDA技术与VHDL电路开发应用实践[M]. 北京:电子工业出版社,2009.

[2] 杨峰. 基于SOC的IIC总线IP核设计[J]. 电脑知识与技术,2010,6(6):1511-1512.

[3] 王前,吴淑泉,刘喜英. 基于FPGA的IIC总线接口实现方法[J]. 微电子技术,2002,30(3):21-24.

[4] 俞伟,徐宁仪,罗飞,等. IIC总线控制器IP核设计[J]. 世界科技研究与发展,2005,27(1): 18-22.

[5] 王钰,潘仕彬,王卉. IIC在数据采集中的应用[J]. 科技广场,2008(8): 190-191.