基于LVDS的高速数字图像存储采集系统

2014-03-26崔永俊

刘 玮,崔永俊,张 昊

(中北大学,电子测试技术国家重点实验室,仪器科学与动态测试教育部重点实验室,山西太原 030051)

0 引言

弹载设备需要采集大量的数字图像信息,因此在弹载设备与地面测试台之间进行数据传输时,需要很高的传输速率[1]。而目前物理层接口无法满足数据的传输速率,常用的RS422接口,每百m双绞线的最高传输速度为1 MB/s[2],这样的传输速度和传输距离,已经无法满足现在对高速远距离传输的要求。LVDS技术的应用提供了解决快速远距离传输的方法。对NAND型FLASH存储器K9WBG08U1M,运用交叉双平面的编程方式,可以实现对数据的高速存储。LVDS技术与交叉双平面编程方式相结合,实现了数据的快速传输、存储以及准确回读,为大量图像数据的传输和存储提供了新的方法。

1 系统总体方案设计

该方案以LVDS技术和交叉双平面编程方式为基础。在系统设计中采用模块化的设计方法,各组成部分既在结构上相互独立,又在功能上相互配合。该设计主要突破数据的准确快速存储和高速传输,这两个困扰采集系统发展的技术瓶颈。数据采集存储系统的设计主要包括FPGA主控接口模块设计,USB通信接口及读写操作时序控制设计和一对并行FLASH模式操作的逻辑设计。

数字图像采集存储系统工作流程图如图1所示。具体工作流程为:一段视频或者一张完整的图片被上位机分割成具有连续帧的图片,USB芯片FT2232H将图片下传,下传的数据在FPGA的控制下存储在两片并联的FLASH芯片K9WBG08U1M中。当图像需要发送时,FPGA把3组存储在FLASH中的图像数据快速读出,通过MAX9247把16位的并行数据转化为串行数据,并以LVDS的方式发送到图像存储转发装置。在图像存储转发装置中保存一路,另一路以PCM码的形式转发到下游设备,供其采集,第三路同样以PCM码的形式回读给上位机。

图1 数字图像采集存储系统工作流程图

2 系统硬件组成

数字图像采集存储系统在硬件方面主要由电源模块、USB接口模块、FPGA主控模块、FLASH存储模块等4部分组成。

FPGA是数字图像采集和存储的控制核心,控制图像数据的接收、变换、存储及发送。数字图像数据采集接口采用PCM接口的形式,存储器和逻辑控制单元的数据接口采用TTL电平。利用PCM接口芯片SN65HVD10实现PCM接口电路的搭建,完成TTL→422及422→TTL的电平转换;用DS92LV18芯片构成采集存储系统回读接口,其内部既含有集成的解串器又有集成的串化器[3]。设计中的DS92LV18芯片起解串作用。当采集存储系统接收到串行差分信号时,差分信号通过DS92LV18芯片转换成16位并行数据传到FPGA,FPGA接收到数据后上传到上位机进行数据分析。

主控板和PC机之间的通信任务依靠USB通信接口完成。USB通信具有数据传输速率高、能够热插拔、应用灵活等优点[4]。在数字图像采集存储系统的设计中采用USB通信芯片FT2232H. 该芯片内部集成了固件库,不需要进行额外复杂的编程[5]。

3 关键逻辑设计

逻辑控制主要实现:USB读、写功能;利用交叉双平面页编程对下传的图像数据进行存储、读出及擦除功能;将图像存储转发装置所存储的图像数据回读至上位机等功能。

3.1 USB读写逻辑设计

FT2232H芯片的A通道能够被设置为FT245同步FIFO模式,在此工作模式下,数据在CLKOUT的上升沿被写入或读出,在同一时刻不能同时进行读和写的操作[6]。

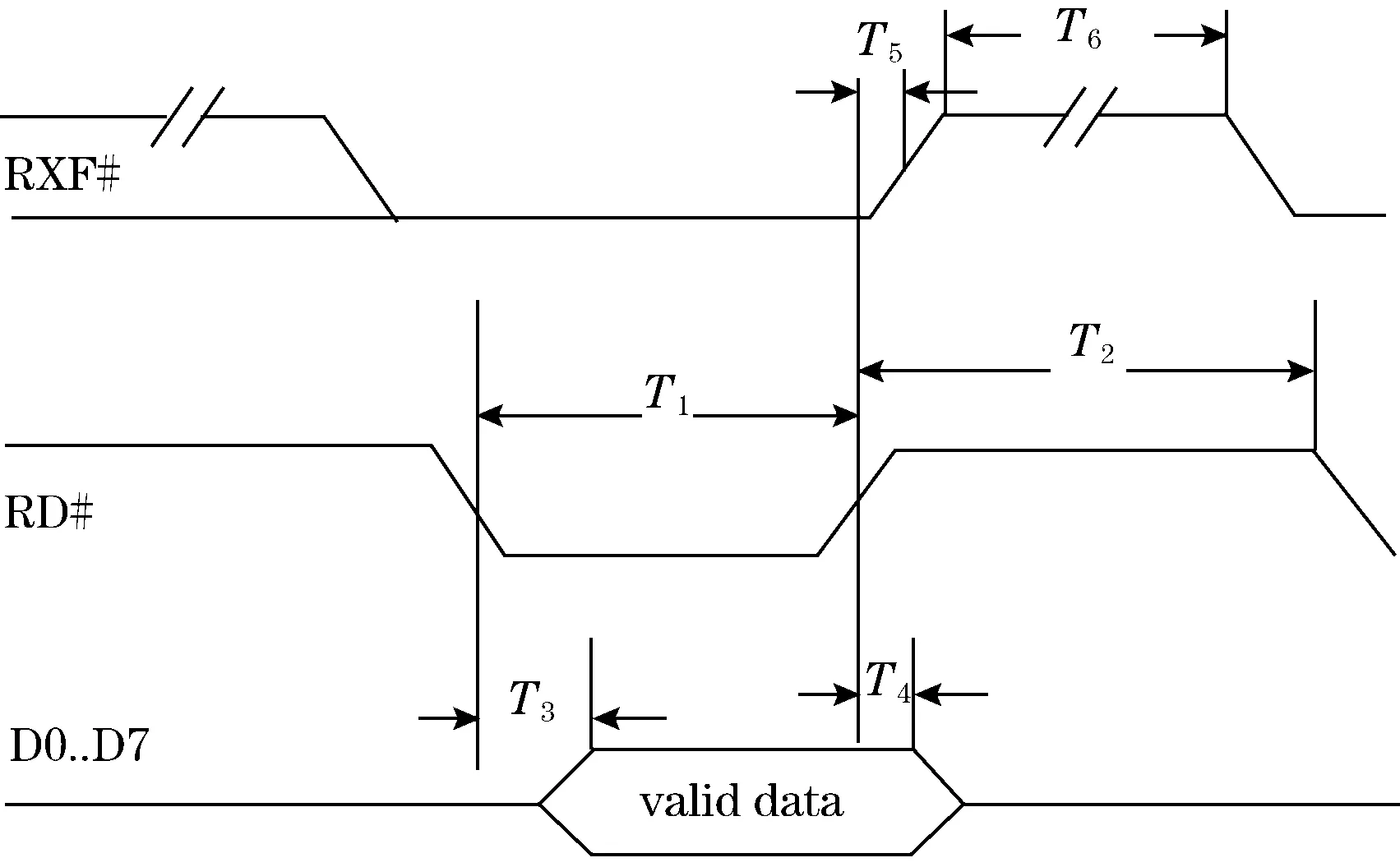

在FT2232H进行读操作时,RXF#的优先级最高,当FIFO中有要读出的数据时,RXF#为低,同时将输出使能信号OE#拉低,然后,再把读使能信号RD#拉低。在此工作模式下,只有在RXF#和RD#同时为低时数据才会被读出。来自FIFO的数据会在RD#的下降沿,输出到A通道的8位数据端口,RD#被拉高,这样就实现了1个字节的读操作;在进行写操作时,TXE#的优先级最高,所以首先判断TXE#的电平情况。若为低,不能进行写操作;若为高,则可以进行写数据操作。当TXE#为低后,把写使能信号WR置高,写入数据,然后把WR拉低,数据将被送到FIFO,完成1个字节的写操作[7]。USB内部FIFO读写时序如图2所示。

3.2 交叉双平面页编程逻辑设计

K9WBG08U1M是NAND型FLASH存储芯片,其数据宽度为8,而需要其实现16位数据的读写和存储。为达到这一要求,一般采用将数据分高低各8位,然后分2次存到1片K9WBG08U1M中的方法。这种方法可行,但存储一个16位的数据,需要执行2次存储过程,这大大制约存储速率,达不到快速存储的技术要求。该设计中采用2片FLASH并行的方式,即将K9WBG08U1M-1和K9WBG08U1M-2并联,以达到将8位存储器宽展为16位的目的。具体操作是将两芯片的片选管脚CE、命令使能管脚CLE、地址使能管脚ALE、读写使能管脚WE、RE分别串联,而各个芯片的R/B管脚相互独立。这样,两个芯片能够同时写入命令或地址,存储速度与普通方法相比,提高了1倍。相互独立的R/B管脚为交叉双平面页编程提供了控制依据。并行FLASH管脚连接图如图3所示。

K9WBG08U1芯片的内部被分为8 192个Block,每个Block共由64个Page组成,编号为0~63;每2 048个Block分为一个Plane,Block 0~4 095编号中的偶数编号Block组成Plane0,奇数编号Block组成Plane1;Block 4 096~8 191的划分方法同前,分为Plane2和Plane3。

(a)USB读时序

(b)USB写时序图2 USB内部FIFO读写时序

图3 并行FLASH管脚连接图

K9WBG08U1内部,数据的存储是一页一页(Page)进行的,这样的页编程可以分为命令、地址、数据的加载过程和自动编程的实现过程。加载过程就是通过控制外部的时钟,将命令、地址、数据等信息写入内部的寄存器;自动编程过程就是芯片按照加载的信息,将数据存储到相应的位置,这样就完成了一个数据的存储,所花费的时间即是一个页编程时间,一般在200~700 μs之间。由芯片资料知该FLASH芯片的读写速度是40 MB/s,所以读写一页所需的时间是:

Twr=1/(40 M)×4 K=102.4 μs

普通的页编程是顺序进行的,即先对某一单元进行命令、地址、数据的加载,完成后,再进行自动编程。若按照此速度计算,得到FLASH的写入速度为:

v=4 096 b/((200+1 024)μs)=13.54 MB/s

这样的速度无法满足任务书的要求。而选用交叉双平面页编程方式,则可使编程时间大大减少。交叉双平面页编程的操作过程如下:首先写入K9WBG08U1M-1中的Plane0的Block0的第0页,紧接着写入K9WBG08U1M-1中的Plane1的Block1的第0页。当再次回到K9WBG08U1M-1的Plane0时,已经过去了:

1/(40 M)×4 096×7=716.8 ns>tprog

式中tprog为编程所用时间。

tprog最大值为700 ns,所以不会对Plane0的Block0进行的第二次操作造成影响。这样对时间的复用,可以缩短加载过程的时间,大大提高存储速度。写FLASH过程如图4所示。

图4 写FLASH过程

在存储芯片并行操作模式中,数字图像采集存储系统上电后会立刻进行坏块监测。只要有一块是无效块,就会把整个存储块当作是无效块来处理。这种无效块地址的统筹管理,极大地方便了流水线式的交叉双平面页编程操作,降低了控制逻辑的复杂度,提升了存储速度。

3.3 下发和上传图像数据程序流程

图像数据的下发过程为:将要下发的图片或者视频转换成具有连续帧的格式;将帧图像进行编码,并加上自检标志和帧标志,然后将图像数据进行下发。

图像数据的回读过程为:上位机将采集或回读的图像数据通过USB接口传输到PC机;上位机对接收到的图像数据计算误码率,之后通过动画的形式,将帧图像播放,最后把数据分析的结果生成文件并保存在指定目录中。

4 实验结果

在系统的各模块单独测试顺利完成后,将各模块连接,进行整个系统的功能测试,实验结果表明系统将数据信息存储到FLASH中的速度是30 MB /s. 上位机将下传的图像数据经过一系列的变化后,从图像转发装置进行了回读。上位机的分析软件,可以将回读的数据和发送的原始数据进行对比,并且可以还原成图像进行显示。测试阶段,下发了一幅周期性良好的图片,并通过上位机软件显示了接收到的数据。数据比对结果显示,误码率为0。FAF300是数据的自检帧头,FAF400是数据的行头,原始数据截图如图5所示,将回读的数据解密后由上位机进行图形显示得到如图6所示的图片,该图片的形式更容易观察实验的结果。

图5 原始数据

图6 回读数据还原的图片

5 结束语

为实现大量数字图像信号的采集与存储,提出了一种基于LVDS和交叉双平面页编程的数字图像采集与存储设计方案。该系统在使用LVDS技术和一对并行FLASH交叉双平面页编程方式的基础上,实现了图像数据的快速存储、高速传输及准确回读。实际测试的结果也充分证明了文中所提出的数字图像采集存储设计方案的正确性和可靠性。

参考文献:

[1] 雷建胜,苏淑靖.多通道数据采集存储器.仪表技术与传感器,2013(1):16-18 .

[2] 崔中华,熊继军,沈三民.基于LVDS技术的实时图像测试装置的设计.电子技术应用,2010(4):84-86.

[3] 李娟 ,刘艳滢.基于FPGA的图像采集模块的设计.仪表技术与传感器,2012(10):27-31.

[4] 张威,苗克坚,陆寅.基于LVDS的多路SPI的PCI板卡设计与实现.计算机测量与控制,2012,20(3):790-793

[5] 安航行.基于LVDS的图像信号源设计与实现:[学位论文].太原:中北大学,2013

[6] 谭炜锋.高速LVDS发送器设计:[学位论文].成都:电子科技大学,2009.

[7] 梁永刚,张会新.基于LVDS的高速远程图像采集存储系统.科学技术与工程,2013,20(13):6001-6006.