NAND FLASH在车载数据采集存储系统中的应用

2014-03-21马良,翟涌

马 良,翟 涌

(北京理工大学机械与车辆学院,北京 100081)

0 引言

自动变速操纵是一个传感器多、控制复杂的机电液一体化的复杂系统。控制过程中信号不仅路数多,而且变化快,很难通过人工直接观测的方法分析研究[1-2]。因此对于变速控制系统的研发,高速的同步随车数据采集存储系统必不可少。虽然,随着电子技术新成果的不断引进,数据采集存储系统得到了很大的发展;但是,目前大多数存储系统不符合车辆控制研究的特色,实用性差、成本高、性价比低。因此针对变速控制系统的研究需求,充分考虑了实车运行过程中振动冲击强、温度变化范围大等特点,设计开发了满足要求的高速车载数据采集存储系统。由于NAND FLASH容量大、成本低、抗震动冲击能力强等特点,选用NAND FLASH为存储设备,运用流水线技术实现了数据的快速存储[3]。

1 系统整体设计方案

车辆自动变速控制系统中的传感器和执行器等相关信号,经过A/D转换电路存入电子控制单元ECU中,之后通过RS-232总线发送到系统下位机。为了满足数据实时采集存储的要求,系统的下位机内部预留了两块16KB的数据缓存。在数据采集过程中,下位机通过串口通信接收数据,并将数据存入预留好的第一块缓存中,当该缓存满之后,数据被存入第二块缓存中,同时将第一块缓存中的数据存入NAND FLASH。系统在每次开始数据采集之前,都会为本次采集的数据创建文件信息,并将文件信息存入NAND FLASH的相应数据块中。数据采集完毕之后,下位机通过内部的SPI模块,并根据保存的文件信息,将数据存入SD卡中。最后,将SD卡中的数据复制到上位机进行分析处理。系统移植了FAT32文件系统,可以将数据以二进制文件的形式存入SD卡,方便上位机直接识别和处理。系统结构框图如图1所示。

图1 系统结构框图

2 系统硬件实现

系统分为下位机和上位机2个部分,下位机采用了Freescale公司的32位微控制器MCF51JM128作为主要的控制器件,该控制器提供了128KB的FLASH存储区和16KB的RAM存储区,同时包含丰富的功能模块,可以满足系统使用要求[4]。系统的下位机通过RS232总线采集数据,并使用MAX232芯片实现电平转换。系统的存储芯片主要选用了512B的EEPROM和Samsung公司的2GB NAND FLASH芯片K9WAG08U1A,其中EEPROM由于读写灵活,主要用于存储NAND FLASH的坏块信息和一些基本的文件信息,NAND FLASH用于存储采集的数据。

根据K9WAG08U1A的芯片手册,该芯片的坏块个数不超过328块,一般出厂时只有30块左右的坏块。EEPROM中一条坏块信息占两个字节,可以至少存储200条坏块信息,实际使用过程中FLASH产生新坏块的情况并不多[5],所以可以满足系统的性能要求。

下位机中微控制器MCF51JM128的工作电压为5 V,而FLASH芯片的工作电压为2.7~3.6 V[3],所以系统选用了电压转换芯片74ALVC164245。74ALVC164245同时支持2个数据组,共16位数据的双向电压转换,其中每组8位数据,由各自的方向控制位控制电压的转换方向,在使用过程中需要动态修改方向控制位的值。为了保证系统的时间准确,下位机中采用了时钟芯片DS1302,当下位机断电后通过电池给该芯片供电。

系统的上位机主要用于数据的分析和处理,同时可以通过RS-232总线与下位机通信,设置下位机的一些参数。系统硬件结构图如图2所示。

图2 系统硬件结构图

3 系统存储原理

系统选用大容量NAND FLASH存储设备K9WAG08U1A作为主要的存储器件,其存储空间是按照块和页的概念来组织的。K9WAG08U1A共包含16384个数据块(Block),每块包含64页(Page),每一页有2048B数据区和64B备用区,备用区在页的末尾,主要用于存储坏块信息、ECC代码等数据。

K9WAG08U1A内部由两块容量为1GB的K9K8G08U0A组成,它们通过2个片选信号CE1和CE2分别使能。每一块K9K8G08U0A内部又由两块容量为512MB的K9F4G08U0A组成,虽然这两块K9F4G08U0A共用同一个片选信号,但它们的页地址范围不同,可以给定不同的页地址和数据内容,实现两块K9F4G08U0A之间的交错页编程。由此可知,K9WAG08U1A由四块容量为512MB的K9F4G08U0A组成,它们共用8个I/O引脚和CLE、ALE等引脚,通过指定片选信号和给定不同的页地址,可以实现四块K9F4G08U0A交错页编程。K9WAG08U1A的内部结构图如图3所示。

图3 K9WAG08U1A的内部结构图

NAND FLASH的读写操作通常是以页为单位的,当向FLASH中存入一页数据时,下位机先发送完页编程指令、存储地址和2 KB数据之后,FLASH芯片自动完成内部的页编程操作。在自动编程过程中,FLASH芯片通过内部程序将数据从数据寄存器保存到指定的存储空间,其R/B端口将被拉低,表示芯片正处于忙工作状态,该过程需要的典型时间为200 μs,最大时间为700 μs[6].通常情况下,下位机需要等待FLASH内部页编程结束后,才能继续向FLASH中存储数据。对于单片FLASH的单页编程操作,每次下位机要等待FLASH芯片的内部编程结束后,才能开始存储下一页数据,这样大量时间耗费在页编程过程中,很大程度上限制了系统存储速度的提高。

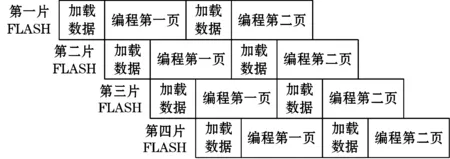

K9WAG08U1A内部由四块K9F4G08U0A组成,它们之间可以交互编程,互不干扰,而NAND FLASH的内部编程可以自动完成,不需要下位机干预,所以可以借鉴流水线技术,提高NAND FLASH的页编程速度[7]。具体实现过程如下:首先加载数据到第一片K9F4G08U0A,当该芯片开始自动编程后,下位机不再等待,而是继续加载数据到第二片K9F4G08U0A,当第二片芯片开始自动编程后,加载数据到第三片芯片,依次执行下去,当加载数据到第四片K9F4G08U0A完成之后,第一片芯片的自动编程已经执行完毕,可以循环继续加载新的数据,这样就可以将FLASH的内部自动编程时间等效为0,提高系统的数据存储速度。基于流水线技术的数据存储原理图如图4所示。

图4 基于流水线技术的数据存储原理图

4 系统坏块管理

NAND FLASH在生产及使用过程中都有可能产生坏块,这将使得系统变得不稳定[8]。文中设计的数据采集存储系统中,选用了512B的EEPROM作为存储FLASH坏块信息的设备。EEPROM读写灵活,同时支持单字节和多字节读写,有利于坏块信息的读取和更新。系统在用于实车实验之前,先要调用相应程序检测NAND FLASH在生产过程中产生的坏块,并将坏块信息存入EEPROM中。系统在实际使用过程中,根据FLASH的页编程和擦除操作结果,判断是否有坏块信息产生,如果页编程或擦除失败,表明当前数据块为坏块,并同时更新EEPROM中的坏块信息,如果为页编程失败,系统还得将数据备份到FLASH中的有效块中。

系统下位机在向FLASH中存入数据之前,首选要判断FLASH中将要存储数据的数据块是否为有效块,如果当前数据块为坏块,则系统将数据块地址加1,跳过当前数据块,然后判断下一数据块是否有效,直到找到有效的数据块为止。系统通过将数据块地址与坏块列表中的信息进行比较,来判断当前数据块是否有效。当跳过坏块后,系统会同时更新当前文件的文件信息的内容,记录跳过的坏块个数,保证文件能准确导入到SD卡中。

5 系统软件实现

系统的下位机程序采用C语言编写,主要包含数据采集、FLASH数据存储、EEPROM数据存储、SD卡文件存储、实时时钟读写等功能模块。系统的上位机软件采用Visual Basic编写,主要用于设置下位机的参数和分析处理采集到的数据。

在数据采集模块中,下位机通过SCI模块接收串口传输过来的数据,使用中断服务子程序将采集到的数据存入下位机的内部缓存中,同时更改数据缓存是否已满的标志,通知系统及时切换数据缓存和存储已采集的数据。

在FLASH数据存储模块中,系统主要通过循环结构实现了数据的流水线存储,为了支持多于8 KB的数据存储,在向各片K9F4G08U0A中加载数据之前,都要先读芯片的状态寄存器,判断上一次加载的数据是否保存成功,然后依次加载数据。所有数据都加载完毕后,系统会再次读芯片的状态寄存器,确保最后一次加载的数据成功保存。系统使用了交错页编程功能,无法通过读R/B信号来判断各片K9F4G08U0A内部页编程是否执行完毕,需要分别是用0xF1和0xF2指令,同时配合两个片选信号R/B1和R/B2,来读各片K9F4G08U0A的状态寄存器,根据返回值的第6位(I/O6)判断内部页编程是否执行完毕,根据第0位(I/O0)判断页编程是否成功。

如果FLASH在页编程过程中,出现了编程失败的情况,为了不影响数据的采集过程,下位机会先将数据备份到FLASH中的数据备份区,同时更新坏块信息和文件信息,等待数据采集完毕之后,再重新处理备份的数据。NAND FLASH的制造厂商保证FLASH第0块为有效块,所以系统选择FLASH的第0块的前30页用于存储文件信息,后34页作为数据备份区。该系统有2片K9K8G08U0A,所以有两个物理地址为0的块,可以选择两个数据块,用于存储文件信息和备份数据。为了防止第0块在使用过程中变为坏块,第0块中的所有数据都得在第1块中备份,系统每次上电都要比较两块中的数据。系统的FLASH数据存储流程图如图5所示。

在SD卡文件存储模块中,系统通过下位机的SPI模块实现了对SD的初始化及读写等操作[4,9-10]。同时,系统移植了FatFs文件系统,支持Fat32文件系统格式,使得下位机创建的文件可以直接被上位机识别,方便了上位机的数据处理过程。

6 系统验证

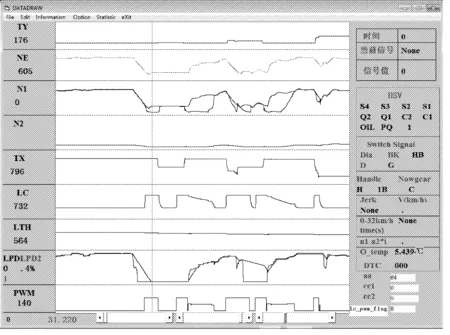

该车载数据采集处理系统应用在某型号AMT重型车辆上,通过与自动变速器ECU的串口通讯,进行了自动变速器控制参数的数据采集。在采集过程中,通过下位机的定时器测得,采用流水线存储技术后,FLASH的单页平均编程时间可以至少缩短200 μs.某次采集所得的数据经过文件格式转换后,根据数据采集的通讯协议,在上位机软件中显示如图6所示。TY为变速器选位行程;TX为换档行程;NE为发动机转速;N1为变速箱输入轴转速;N2为变速箱输出轴转速;LC为离合器行程;LTH为油压;LPH为油门踏板位置;PWM为占空比。

图6 数据显示与分析界面

7 结束语

文中设计了基于NAND FLASH的车载数据采集存储系统,认真分析了K9WAG08U1A的内部结构,运用了流水线技术实现了数据的快速存储。通过大量随车实用表明,系统硬件合理、可靠,软件功能丰富、实用,满足车辆变速控制系统对数据采集存储系统的使用要求。

参考文献:

[1]陈慧岩,席军强,丁华龙.装甲车辆自动变速操纵系统的数据采集与分析系统技术的研究.兵工学报,2001,22(3) :388-392.

[2]董玉梁,陈慧岩.车辆AMT数据采集分析及系统.工业仪表与自动化装置,2003(4):46-48.

[3]朱建江,余世明,林鑫.NAND FLASH在嵌入式袜机提花系统中的研究及应用.计算机应用于软件,2012,29(10):287-290.

[4]安冬.基于MCF51JM128的SD卡读写系统设计与实现:[学位论文],沈阳东北大学,2009.

[5]尹蕾.NAND FLASH固态存储卡的设计与实现.西安电子科技大学学报,2012,44(2):300-304.

[6]郑文静,李明强,舒继武.Flash存储技术.计算机研究与发展,2010(4):716-724.

[7]赵榉云,张敬帅.基于NAND Flash的数据存储系统设计.单片机与嵌入式系统应用,2012(1):71-73.

[8]舒文丽,吴云峰,赵启义,等.NAND Flash存储的坏块管理方法.电子器件,2011,34(5):580~583.

[9]李世奇,董浩斌,李荣生.基于FatFs 文件系统的SD卡存储器设计.测控技术,2011,30(12):9-81.

[10]郭丹丹,任德志,葛南燕.基于CAN总线和SD卡的车载嵌入式系统.仪表技术与传感器,2007(4):29-33.