用于计算机体系结构教学的哈佛体系结构模拟器

2014-03-17张前贤莫毓昌潘竹生

张前贤+莫毓昌+潘竹生

摘要:已有的计算机体系结构教学模拟器主要是面向冯诺依曼体系结构。针对缺乏面向哈佛体系结构模拟器这一问题,本文提出并设计了基于开源软件包Multimedia Logic(MML)[1]哈佛体系结构模拟器。该模拟器不仅具有软件的易动态运行、易修改、易二次开发的优点,同时还实现了硬件结构的逻辑门级映射[2],从而在课程教学和实验设计方面对哈佛体系结构教学提供了很好的支持。

关键词:模拟器;哈佛体系结构;MML

在计算机体系结构课程教学过程中,冯诺依曼体系结构和哈佛体系结构是重点教授的两种体系结构类型。[3]冯诺依曼结构,又称为普林斯顿结构,是一种经典的体系结构,由CPU,存储设备,I/O设备组成。[4]这种体系结构采用指令与数据合并存储的方式,程序指令宽度与数据宽度一样。随着CPU设计技术的发展,片内数据传输路径的增加,指令和数据的互斥读取很大程度上影响了CPU运行效率。为此,哈佛大学提出一种新的体系结构,在这种结构中数据存储器与程序代码存储器分开,各自有自己的数据总线与地址总线,实现指令和数据的并行读取。由于哈佛结构需要CPU提供大量的数据线,因而很少作为CPU外部构架来使用。但是对于CPU内部,通过使用不同的数据和指令缓存,可以有效地提高指令执行的效率,因而目前大部分计算机体系结构都是CPU内部的哈佛结构和CPU外部的冯诺依曼结构并存。

在冯诺依曼体系结构教学方面,许多大学已经开始研发各种基于软件和硬件模拟器来辅助课程教学和实验教学。[5]但在哈佛体系结构教学方面仍然缺乏有效的模拟器。[6]针对这一问题,本文介绍了我们基于开源软件包Multimedia Logic(MML)所开发的用于哈佛体系结构教学的模拟器。

● 模拟器结构和指令

1.总体结构

哈佛体系结构具有程序与数据物理上分开存储的特点,从而提供了较大的数据存储器带宽。哈佛体系结构的工作原理是:CPU控制器首先到程序指令存储器中读取程序指令内容,根据指令中操作数的地址,再到相应的数据存储器中读取数据,并进行下一步的运算。

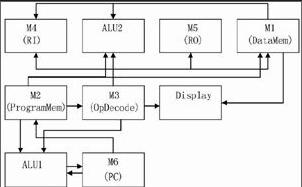

图1给出了我们所开发的哈佛体系结构模拟器框图。其中M1(DataMem)作为数据存储器,其主要功能是用于存放执行的中间结果和过程数据。M2(ProgramMem)作为程序存储器,其主要功能是用于存储程序指令。M3(OpDecode)作为指令译码器,其主要功能是将操作码信号翻译成机器能够识别的控制信号。M4(RI)作为输入寄存器,其主要功能是用于暂时存放数据存储器输出的数据。M5(RO)作为输出寄存器,其主要功能是用于暂时存放运算结果。M6(PC)作为程序计数器,其主要功能是用于存放下一条指令所在单元的地址。ALU1和ALU2是算术逻辑单元,其功能分别是控制程序计数器的地址和执行相关的逻辑运算。Display作为显示器,其主要功能是输出相关的结果。

2.指令系统

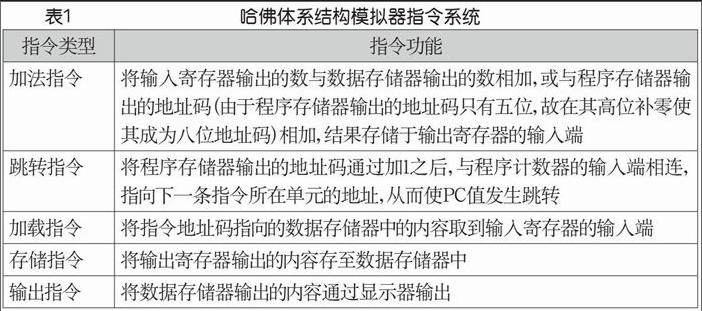

在哈佛体系结构模拟器设计中涉及的指令有5条[7],分别是加法指令、跳转指令、加载指令、存储指令和输出指令。这些指令的具体说明详见下页表1。在这些指令中,涉及寻址方式有立即寻址和直接寻址。

● 模拟器设计

1.数据寄存器设计

在哈佛体系结构模拟器设计中涉及的数据寄存器有输入寄存器M4和输出寄存器M5。

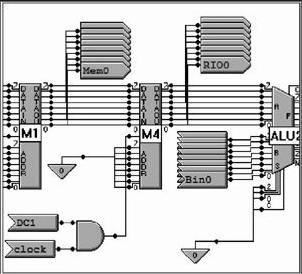

其中输入寄存器M4的数据输入端与数据存储器的输出端相连;地址输入端与低电平相连;将控制信号DC1和时钟信号作为与门的两个输入端,再与输入寄存器的读写控制端相连;将输入寄存器的输出端与ALU2的其中一个输入端相连。图2给出了输入寄存器的设计图。[8]

输出寄存器M5的数据输入端与ALU2的输出端相连;地址输入端与低电平相连;将控制信号DC2和时钟信号作为与门的两个输入端,再与输入寄存器的读写控制端相连;将输出寄存器的输出端通过信号I-Mem与数据存储器的输入端相连。图3给出了输出寄存器的设计图。

2.存储器设计

在哈佛体系结构模拟器设计中涉及的存储器有数据存储器M1和程序存储器M2。

图4给出了数据存储器的设计图。数据存储器M1的数据输入端通过信号I-Mem与输出寄存器的输出端相连;地址输入端通过信号Imm与程序存储器的指令地址码(由于程序存储器M2输出的地址码Imm只有五位,故在其高位补零使其成为八位Imm)相连;将控制信号DC5和时钟信号作为与门的两个输入端,再与数据存储器的读写控制端相连;将数据存储器的输出端通过信号Mem与输入寄存器的输入端相连。

图5给出了程序存储器的设计图。程序存储器的数据输入端与低电平相连;地址输入端与程序计数器的输出端相连;将读写控制端直接与低电平相连;将程序存储器输出端的高三位作为指令译码器的操作码与指令译码器相连,低五位作为地址码与数据存储器的地址输入端相连。

3.指令设计

哈佛体系结构模拟器采用的指令格式为:每条指令长度为11位,其中操作码长度为三位,地址码长度为八位。三位操作码在经过指令译码器之后,可以形成8个八位的控制信号DC0~DC7。由于程序存储器M2的高位输出端有三位操作码,低位输出端的地址码只有五位,故在其高位补零使其成为八位地址码。表2给出各条指令的操作码和控制码分配方案。

● 应用

我们以计算y=x+1为例说明模拟器应用操作过程。在应用操作过程中,程序存储器中存储的内容既和程序的操作码有关,同时与地址码也有一定关系,所以在设计程序存储器相关程序时,要考虑到操作码和地址码两部分。在设计程序存储器时,需要注意一点:由于程序存储器输出端只有3位操作码,故在设置时,当程序指令为“0*”时,操作码指向指令译码器的第0位;当程序指令为“2*”时,操作码指向指令译码器的第1位;当程序指令为“4*”时,操作码指向指令译码器的第2位;当程序指令为“6*”时,操作码指向指令译码器的第3位;余下几位,以此类推。以上所用“*”表示指令的地址码。endprint

在设计数据存储器时,需要事先在数据存储器的地址端存入十六进制数“79,3D,78,2B,31,0D,78,3D,34,0D,79,3D”,其所对应的ASCII值为“y=x+1_x=4_y=”,其中“_”代表回车。这样的数据安排,能够使指令顺序执行,使显示器依次输出想要的结果。十六进制数“34”所对应的ASCII码值为4,其值可以修改为30~38中的任意值,最终的输出结果也会随之改变。

在整个程序的执行过程中,前12个周期是按照指令存储的顺序依次执行,其功能是为了实现“y=x+1_x=4_y=”,其中“_”表示回车。第13个周期是一条跳转指令,其功能是将第9条指令输出的数据取来,也就是输出“4”;第14个周期是一条跳转指令,其功能是将第4条指令输出的数据取来,也就是输出“+”;第15个周期是采用立即寻址的方式,通过指针PC指向程序存储器所在的位置,使信号Imm成为00000001,并通过信号Bin传输到ALU的输入端,最终使显示器输出“1”;第16个周期是一条跳转指令,其功能是将第2条指令输出的数据取来,也就是输出“=”;接下来的几个周期,使DC6为低电平,使显示器无法输出,将信号RIO中的内容与信号Bin中的内容相加,并在经过两个周期后,传输至信号Mem,此时再将DC6设为高电平,使下一个时钟信号由低电平变为高电平时,将信号Mem中的内容输出至显示器。

● 结论

面向本科生“计算机体系结构”课程教学的模拟器有很多,但由于MML一方面具有软件的易动态运行、易修改、易二次开发的优点,同时实现了硬件结构的逻辑门级映射,弥补了其他计算机组成结构模拟器的不足之处,因而,本文推荐使用MML模拟器来进行教学活动。同时,计算机体系结构主要有两类:冯诺依曼体系结构和哈佛体系结构。由于笔者近期已经提出了基于开源软件包Multimedia Logic (MML)·冯诺依曼模拟器ARCH,因而,笔者在本文中提出了另一种想法——用于计算机体系结构教学的哈佛体系结构模拟器。这样就弥补了MML模拟器在哈佛体系结构教学方面的不足,从而使MML模拟器能够更好地用于计算机体系结构的教学工作。

通过本文设计的用于计算机体系结构教学的哈佛体系结构模拟器,学生能够更加轻松且深刻地理解哈佛体系结构,从而为以后步入社会打下坚实的基础。

参考文献:

[1]Multimedia Logic(Version 1.4)Emulator Program. http://www.softronix.comllogic.html.

[2]莫毓昌,张前贤,陈荣根.ARCH:用于计算机组成与结构课程教学的模拟器[J].计算机教育,2013(10):56-61.

[3]W.Stallings.Computer Organization and Architecture[M].5th edition NJ: Prentice Hall, 2000:1-98.

[4]A. Tanenbaum. Structured Computer Organization[M].4th edition, NJ: Prentice Hall, 1999:1-320.

[5]C Yehezkel, W. Yurcik, M. Pearson, and D. Armstrong. Three Simulator Tools For Teaching Computer Architecture: EasyCPU, Little Man Computer, and RTLSim [J]. Journal on Educational Resources in Computing, 2001,1(4):60-80.

[6]D.Colton, G.Embrey, L.Fife, S.Mikolyski, D.Prigmore, and T.D.Stanley. From Architecture to Architecture: Undergraduate Students Design and Implement Computers Using the Multimedia Logic Emulator [J].Computer Science Education, 2007, 17(2):141-152.

[7]H.Oztekin, F.Temurtas1, A.Gulbag. BZK.SAU Implementing a Hardware and Software-based Computer Architecture Simulator for Educational Purpose [C].Proceedings of the 201O International Conference On Computer Design And Appliations (ICCDA 2010), 2010:90-97.

[8]T.D.Stanley, T.Q.Xuan, L.Fife, D.Colton, Simple Eight Bit, Emulated Computers for IllustratingComputer Architecture Concepts and Providing a Starting Point for Student Designs [R].Ballarat, Victoria, Australia, January 2007.endprint