基于W5100芯片的网络通信电路设计

2014-03-14孙立功张立文孙孟方

王 勇 孙立功 张立文 李 娜 刘 博 孙孟方

(1.河南科技大学电气工程学院,河南 洛阳 471023;2.中国航空工业集团公司洛阳电光设备研究所,河南 洛阳 471009)

基于W5100芯片的网络通信电路设计

王 勇1孙立功1张立文1李 娜1刘 博1孙孟方2

(1.河南科技大学电气工程学院,河南 洛阳 471023;2.中国航空工业集团公司洛阳电光设备研究所,河南 洛阳 471009)

W5100芯片是一种高集成度的网络接口芯片,内部集成有10/100M以太网控制器,经过简单的接口操作,可以实现没有操作系统的internet连接,主要应用于成本较低、稳定性较高的嵌入式系统中。本文介绍了W5100的内部构成、引脚分布、接口方式及硬件电路设计。

W5100芯片;TCP/IP协议;网络通信;嵌入式系统

1.引言

在工业控制领域,设备间的通信常采用串行接口。随着技术的进步,对提高生产效率、控制质量和降低成本的要求越来越高,串行通信方式传输速率低、传输距离短、布线复杂等缺点逐渐展现。而以太网可以方便地接入现有网络,数据传输率高,兼容性好,因此基于TCP/IP协议的以太网已经发展成为IT产品的主要通讯手段。在嵌入式领域,为了能跟上网路自动化的潮流,以太网的应用越来越普遍。嵌入式系统实现接入Internet的关键是对TCP/IP协议的支持,目前常采用内含TCP/IP协议栈的W5100网络通信芯片进行接口设计,这种方法所涉的硬件电路简洁、开发工具成熟。

2.W5100芯片功能及引脚分布

W5100芯片内部主要由四部分构成:与微处理器接口单元、以太网物理层单元、TCP/IP硬件内核单元以及发送/接收数据缓冲区单元。内含端口寄存器、公共寄存器、发送存储器和接收存储器,共占用32kB的存储空间。预留有与微处理器接口的并行总线接口,增加了SPI串行总线接口,线路传输率可达25Mbps。端口寄存器用于控制4个通路在网络连接后的数据收发,各个通路均有独立的寄存器设置。其中,端口状态寄存器用于显示端口相应状况;端口中断寄存器用于通报通路连接状况;端口命令寄存器用于控制端口的初始化、关断、建立连接和终止、数据传输、命令接收等,对该位写入不同的参数值,即可实现相应的控制。公共寄存器包括1个模式寄存器、4个网关地址寄存器、4个子网掩码寄存器、6个本机硬件地址寄存器、4个本机IP地址寄存器、1个中断寄存器、1个中断屏蔽寄存器、2个重发时间寄存器、1个重发计数寄存器等。W5100采用薄型四方扁平式封装,共有80个引脚,按照功能分为6大类[1]:

(1)以太网物理层类信号:1脚为物理层片外电阻端RSET_BG,使用时需要连接一个12.3 kΩ的电阻到地。运行模式控制线3根,63~65引脚为OPMODE[0..2],这3条控制线输入不同的数字信号,将使以太网物理层工作在8种不同的模式下。差分信号对输入线2根,用于接收从介质传输来的差分数据信号,5脚为信号线对的正极RXIP,6脚为信号线对的负极RXIN。差分信号线对输出线2根,用于向介质传输差分数据信号,8脚为信号线对的正极RXOP,9脚为信号线对的负极RXON。

(2)与微处理器接口类信号:控制线5根,59脚为RESET端,低电平有效,用于初始化W5100芯片;55脚为CS端,低电平有效,用于片选W5100芯片;57、58引脚为读写控制端WR、RD,在对W5100进行数据读写时由微处理器发出相应控制时序;56脚为中断输出INT端,W5100内部产生中断时,该引脚进行低电平输出。数据线8根,数据位从高到低分别对应引脚l9~26,微处理器通过这些引脚对W5100进行数据操作。地址线15根,地址线从高到低分别对应38~42、45~54引脚,通过对它们的设置来选择W5100内部的存储器和寄存器。SPI接口功能线5根,30脚为SPI功能使能引脚SEN端,高电平有效;29脚为SCLK端,作为SPI的时钟输入;28脚为SPI从模式选择端SCS,低电平有效;27、28脚为MOSI、MISO端,它们是SPI通信方式的2根数据线。

(3)电源:电源引脚20根,2脚用于模拟系统3.3V供电,12、18、44脚用于数字系统3.3V供电,7、74脚用于模拟系统1.8V供电,15、16、33、69脚用于数字系统1.8V供电,4、10、77脚用于接模拟电源地,13、14、17、32、43、68脚用于接数字电源地,11脚用于输出1.8V电压。

(4)工作状态指示信号:66、67、70~73脚分别连接一个LED灯,分别用于指示连接状态、连接速度、全双工模式、IP地址是否冲突、接收数据状态及发送数据状态,低电平有效。

(5)时钟信号:75脚为XTLN端,76脚为XTLP端,使用时外接25MHz的晶振。如果使用外部振荡信号,信号连接到XTLP端,而XTLN端保持断开。

(6)其它:37~34脚为TEST-MODE[0..3],用于选择芯片的工作模式,通用模式为“0000”,其它模式作为内部测试使用。3、60~62、78~80脚为NC端,供厂家测试用,用户不能使用。

3.W5100芯片接口方式

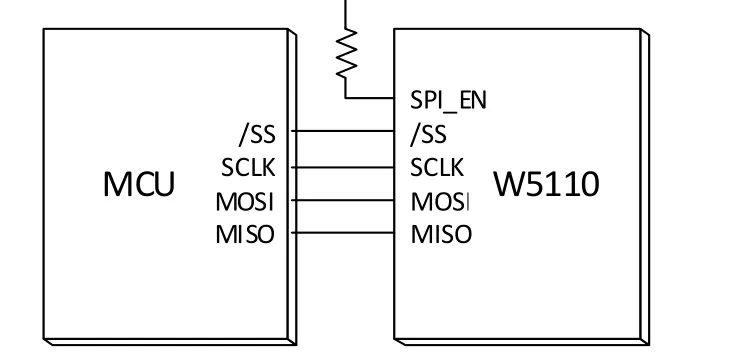

W5100提供3种接口:直接并行总线、间接并行总线和SPI总线。直接并行总线将15根地址线,8根数据线与微处理器直连,并连接片选信号、写使能、读使能及中断信号4根控制线。间接并行总线方式中地址自增加,这样地址线只需要2根,其余不用的地址线接下拉电阻,这种方式下数据传输速度要比直接并行总线方式慢。SPI总线接口只需要4个引脚(/SS、CLK、MOSI、MISO)和微处理器连接即可,当SPI_EN引脚接上拉电阻,则SPI通信模式有效,具体接口方式如图1所示。在SPI接口方式下,W5100作为从设备,主控制器发出一系列指令控制其运行。以上三种接口方式各有优缺点,在实际开发过程中,设计者可根据数据传输速率、I/ O口线占用情况等实际需要来选取[1,2]。

图1SPI接口方式

4.硬件电路设计

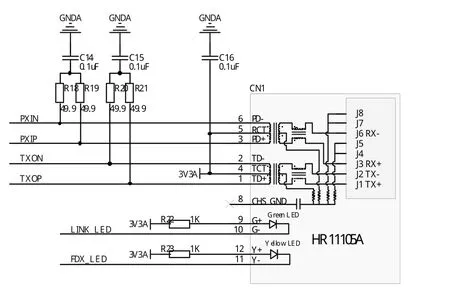

在微处理器接口数量有限且对数据传输速率要求相对不高的情况下,SPI接口方式是首选。在W5100中,SPI_EN为SPI接口使能引脚,将其经10K电阻上拉到高电平以允许SPI模式;RSET_BG是物理层片外电阻引脚,在使用时需要外接一个12.3kΩ±1%的电阻到地,在电路设计中可采用一个12KΩ电阻和300Ω电阻串联实现;时钟电路由1个25MHz晶振、2个22pF电容和1个1MΩ电阻组成;RESET为复位输入引脚,它直接与微处理器复位引脚复用,这样可以使它们同步复位,提高系统稳定性;用9个电容对芯片电源进行去耦,使芯片工作更加稳定。W5100提供6个LED指示引脚,用于显示W5100工作情况,可以让用户直观地看到系统工作状况。W5100最终通过RJ45连接口与外界连通,RJ45中以太网隔离变压电路如图2所示,隔离变压器采用HR911105A,可以实现对2kV以上电压隔离作用,防止静态干扰,两个隔离变压器都需要外接一个0.1uF的电容和两个49.9Ω电阻。

图2 以太网隔离变压电路

5.结束语

由于W5100芯片内部集成了以太网物理层单元,因此设计中可以省去该层电路设计,从而简化了电路,节约了成本,提高了电路的可靠性。将嵌入式设备接入网络是科技发展的必然趋势,网口通信是所有设备网络化的基础,具有广阔的应用范围和市场潜力。

[1]王计元.单片网络接口芯片W5100的原理与应用[J].上海电力学院学报,2011,27(2):153-159.

[2]陈实,王琪,张铁军等.一种基于W5100的数据传输系统[J].电子技术应用,2013,39(9):54-60.

Design of Network Communication Circuit Based on W5100 Chip

Wang Yong1Sun Ligong1Zhang Liwen1Li Na1Liu Bo1Sun Mengfang2

(1.Electrical Engineering College,Henan University of Science and Technology,Luoyang 471023,Henan; 2.Luoyang Research Institute of Electro-Optical Equipment ofAVIC,Luoyang 471009,Henan)

W5100 is a network interface chip with high integration density.10/100M ethernet controller is integrated in this chip. By a simple interface operation,W5100 chip can realize internet connection without operating system.It is mainly used in the embedded system of lower cost and high stability.Internal structure,pins distribution,interface mode and hardware circuit design of W5100 chip are introduced.

W5100 chip;TCP/IP protocol;network communication;embedded system

王勇,男,河南淮滨人,硕士,讲师。研究方向:应用电子电路开发与设计。

河南省教育厅科学技术研究重点项目,项目编号:14A510003。