自适应动态延时调整的SERDES技术在宽带数据传输中的应用*

2014-03-05张峰

张 峰

(中国西南电子技术研究所,成都 610036)

1 引言

串行器/解串器(SERDES)传输技术广泛应用于机载通信终端高速数传系统中。传统设计方法为采用外置DS92LV16芯片[1],实现并/串转换后进行板间数据传输,这种方法需占用宝贵的嵌入式管脚资源,1片DS92LV16至少需要24根信号线来传输16 b位宽信号,即采用DS92LV16芯片无法实现多路间数传,故基于FPGA片内的SERDES传输技术成为研究的热点。SERDES作为FPGA中嵌入的一种原语(Primitive)结构,可代替传统的外置并/串转换芯片,但受其固有的传输相位漂移影响,通常不能多路并行使用,限制了SERDES技术在宽带链中的应用。笔者通过对SERDES及Idelay的工作原理进行研究,提出了一种能够进行自适应动态延时调整的方法,克服了SERDES传输中的相位漂移问题,成功实现了60个SERDES通路、每路850Mb/s的多路SERDES并行传输,且经过项目验证。

文中第2节简单介绍SERDES原语(Primitive)结构;第3节针对项目需求,提出基于SERDES传输的具体实现方案及自适应动态延时调整方法;第4节为实验结果,最后是结束语,给出结论及应用展望。

2 SERDES原语简介

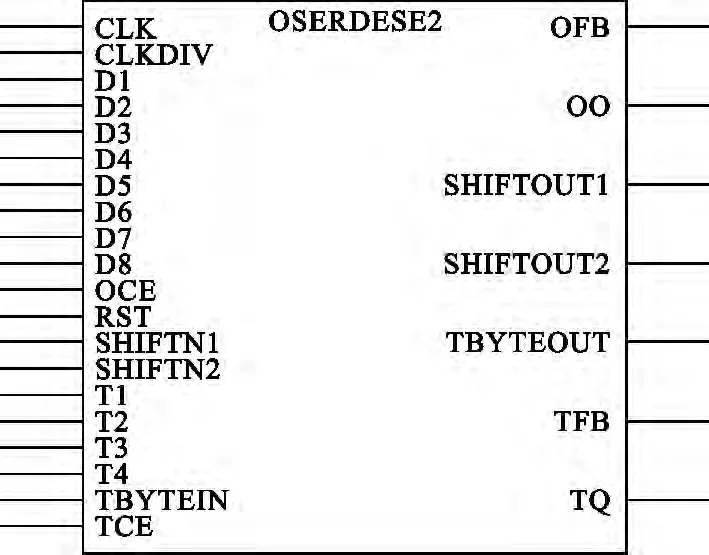

SERDES原语为FPGA内的一种新型并/串转换技术,基于LVDS电平,利用FPGA的普通用户IO即可实现约1 Gb/s的高速传输,以代替传统的外置并/串转换芯片。K7(Kintex-7)系列FPGA中SERDES的发、收端分别称为OSERDESE2、ISERDESE2,其原语结构分别如图1和图2所示。

图1 OSERDESE2原语结构Fig.1 The structure of OSERDESE2 primitives

图2 ISERDESE2原语结构Fig.2 The structure of ISERDESE2 primitives

SERDES传输参数属性如表1表示。

表1 OSERDESE2/ISERDESE2传输属性Table 1 The transmission attribute of OSERDESE2/ISERDESE

3 能够进行自适应动态延时调整的SERDES传输技术实现方案及难点分析

3.1 项目需求

宽带链某机载通信终端中,AD采样子卡需要将DDC下变频后数据送给信号处理板,提出以下要求:一是传输通路分为I/Q二路,共60路;二是每路速率为384 Mb/s(12 b×32 MHz);

3.2 硬件方案

若采用传统的 DS92LV16芯片实现,1片DS92LV16至少需要24根信号线来传输16 b位宽信号,即I路或Q路,则60路数据共需要信号线数量为60×24=1440。鉴于目前FPGA最大管脚数目为1736,无法提供1440个用户 IO,故采用DS92LV16芯片的方式行不通。

与DS92LV16芯片方式占用1440个管脚不同,若采用SERDES原语传输下变频后60路I/Q基带数据,只需要60对普通用户IO即可,降低了FPGA的管脚压力,减少了PCB板面积需求(至少减少了60片DS92LV16芯片的面积),有利于在空间受限的机载环境中应用。

基于SERDES传输技术的系统架构如图3所示,其中发射端OSERDESE2位于AD子卡,而接收端ISERDESE2位于信号处理板内。

图3 基于SERDES技术传输的系统框图Fig.3 The structure of SERDES transmission system

3.3 软件实现

3.3.1 时钟速率分析

DDC下变频后数据速率为32 MHz,即OSER-DESE2的并行时钟为32 MHz,数据位宽为12 b。根据表1可知,必须将12 b数据低2位补0后,拼成14 b进行数据传输,采用 DDR(Double Data Rate)双沿方式进行传输,则OSERDESE2的数据率为448 Mb/s(14 b×32 MHz),相应的 ISERDESE2的串行时钟、并行时钟分别为224 MHz和32MHz。

3.3.2 数据同步实现

假设发送端OSERDESE2连续发出4 b数据(ABCDABCD……),接收端如何进行边界定位,确定4 b数据是ABCD,而不是BCDA、CDAB、DABC?

引入同步判决机制。在进行SERDES数据传输时,必须先建立链路同步,确定数据边界后,再发送正常数据。

假设接收端ISERDESE2接收到的数据为BCDA,在FPGA中通过逻辑实现移位bitslip功能,其时序要求如图4所示。使ISERDESE2的并行数据输出端产生循环移位,则通过3次移位后,可正确接收数据ABCD,移位过程如表2所示。

图4 bitslip时序要求Fig.4 The timing requirement of bitslip

表2 Bitslip与数据移位关系Table 2 The relationship between bitslip and data-shifting

待60路的I/Q数据都完成边界定位后,接收端发送同步完成信号给发送端后,发送端可正常发送DDC数据。

3.3.3 基于Idelay的自适应动态延时调整技术

由于I路及Q路基带数据传输所用的60个SERDES通路,分布在FPGA内不同的Bank,其传输必然存在时序差异(time skew),接收端恢复出原始数据时,会出现毛刺,如图5所示(正确数据为光滑的锯齿波)。

在经过多种时序约束及优化后,仍有少数SERDES不能正确接收数据,必须采用基于Idelay的延时调整,以消除时序差异。

Idelay是FPGA中一种原语结构,用于调整接收数据的时延。K7系列FPGA中每个Idelay分为32个时钟间隔(tap),如图6所示,每个间隔的周期长度为78 ps,故其能调整的接收时延为2.496 ns。

图6 Idelay时隙间隔结构Fig.6 Idelay tap structure

采用Idelay调整时延,传统方式为通过实验手动调整Tap的数值,重新编译后下载,通过Chipscope观测数据与时钟的相位关系后,再进行反复修正,直至数据采样点刚好位于数据的中间,费时费力。为此,笔者提出了一种能够进行自适应的动态延时调整技术,它可以自动根据时钟和数据的相位关系,调整Tap的数值,最终将数据采样点放到数据的中间,避免了繁琐的手动调整Tap值,其原理如图7所示。

图7 自适应动态延时调整原理Fig.7 The adaptive dynamic delay adjustment

基本原理步骤如下:

(1)设Idelay中的Tap的初始值为0;

(2)通过步进为1,增加Tap的值,增加 ISERDESE2接收的时延,当检测到数据变化时(从data0变为data1),记录此时Tap的数值为A;

(3)继续增加tap的值,再次检测到数据变化时(从data1变为data2),记录此时Tap的数值为B;

(4)设定Tap的数值为(A+B)/2,此时在采样点X时,对应数据即为Data1,且在data1的中间。

这是软件实现的难点。

在采用了基于Idelay的自适应动态延时调整技术后,ISERDESE2能够正确接收下变频后的60路的I路及Q路数据。

4 实验结果及分析

实验条件:PC机配置为Windows SP3,i5-2400CPU@3.10GHz,3.2 GB 内存;ISE 版本为 14.5。

利用FPGA调试工具chipsope,观测60路数据,接收端ISERDESE2可以448 Mb/s速度正确接收自OSERDESE2发出的数据,完全消除了图5中的毛刺现象,如图8所示。

图8 SERDES正确数据接收Fig.8 The correct data received by SERDES

实验中,采用基于Idelay的自适应动态延时调整技术后,实测SERDES的传输速度进一步提高到了850Mb/s,工程中所用K7系列FPGA,其速度均为-1等级,基本达到Xilinx公司标称的900Mb/s,若采用-3速度等级的FPGA,则SERDES的传输速度将达到1.2 Gb/s,可满足绝大部分数据传输要求,验证了笔者提出的自适应动态延时调整的SERDES传输技术的可行性及优越性。

5 结束语

SERDES传输技术因其用FPGA普通的用户IO管脚实现了高速串行数据传输(速度可达1 Gb/s),非常适用于数据位宽14位以下的并/串转换、串/并转换,避免了对传统并/串转换芯片如DS92LV16芯片的依赖。笔者提出的基于Idelay的自适应动态延时调整技术能动态调整ISERDESE2接收的时延,使数据采样点恰好在数据中间,解决了多路SERDES传输时固有的相位漂移问题,增强了SERDES传输的稳定性。由于目前尚未发现运用基于Idelay的自适应动态延时调整技术实现多路SERDES传输的案例,故进一步验证笔者提出的这种传输方案在苛刻环境的可靠性是下一步的研究工作。

[1]马红艳,张福欣,尹哲春,等.LVDS技术在数字视频传输系统中的应用[J].电子设计工程,2010,18(7):24-26.MA Hong-yan,ZHANG Fu-xin,YIN Zhe-chun,et al.Application of LVDS in digital video transmission system[J].Electronic Design Engineering,2010,18(7):24-26.(in Chinese)