采用DSP+FPGA的三轴运动控制器设计

2014-03-03何远松谢明红

何远松,谢明红

(华侨大学 机电及自动化学院,福建 厦门361021)

运动控制器是上位机与驱动器之间的一座桥梁,它的性能很大程度上决定了整个数控系统的性能.“PC+运动控制器”的开放式数控技术已成为运动控制领域的主流方向[1],它由通用PC机发出控制指令,专用运动控制器接收指令完成具体功能.随着数控技术的飞速发展,运动控制器的处理单元由单片机、专用芯片(ASIC),发展到了数字信号处理器(DSP)和现场可编程门阵列(FPGA)组成的高性能处理器[2-4].DSP的哈佛总线结构、多流水线指令结构,特别适合数据量大、计数复杂、实时性要求高的场合;FPGA的硬件可重构性强、设计灵活、I/O口众多,可方便接口模块扩展,减轻了DSP负担.DSP+FPGA结构已成为大多数高性能开放式运动控制器的主流设计方向 .本文设计了一种以浮点型数字信号处理器TMS320F28335为主控制器和EP2C8F256C6为协处理器的通用三轴运动控制器.

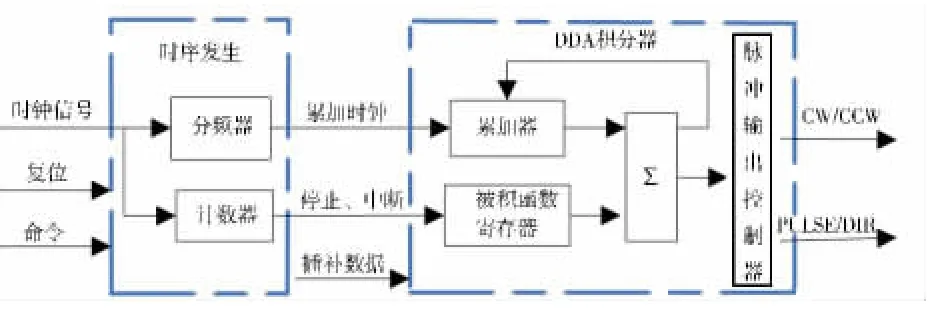

图1 三轴运动控制器的系统框图Fig.1 System block diagram of three-axis motion controller

1 整体结构设计

图1为三轴运动控制器的系统框图.PC机作为上位机,运动控制器作为下位机,二者通过PCI接口芯片和双口RAM进行通讯.PC机发送控制命令,通过PCI接口芯片传送到公共存储器——双口RAM中;然后,DSP程序从双口RAM中读取指令或数据,结合FPGA反馈的编码器信号对电机的速度和位置进行规划(包括伺服滤波、速度曲线规划、粗插补运算等);最后,FPGA根据DSP传送来的数据完成精插补后,经D/A模块发送模拟量信号或经变频脉冲发生模块输出脉冲/方向信号到各个电机轴的伺服驱动单元,从而实现电机的速度模式控制和位置模式控制.

8路通用数字输入、输出信号,3个驱动器的控制信号以及限位、报警信号都通过FPGA的I/O口设计完成,以减轻DSP开销.同时,FPGA还承担PCI接口芯片的数据扩展,以及双口RAM的端口仲裁功能.整个控制器的输入输出信号(模拟电压输出部分除外)都采用光电隔离,以增强抗干扰能力,提高系统稳定性.DSP和FPGA的I/O电平都为3.3 V,通过DSP的I/O对FPGA内部的各模块地址空间进行统一编址,采用SN75174芯片完成单极性信号转差分信号,采用SN75175芯片完成差分信号转单极性信号.SN74LVTH16254完成3.3~5.0 V电平转换,高速光耦6N137实现输入与输出隔离.

2 硬件设计

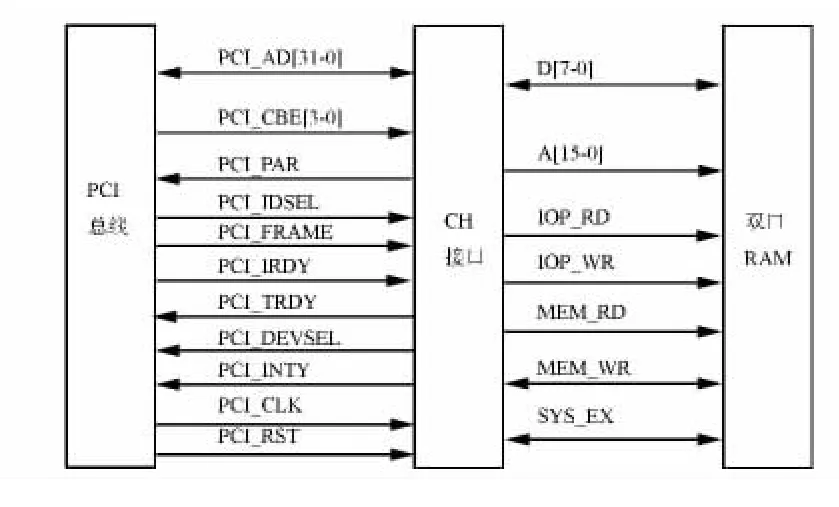

2.1 PCI接口

连接PCI总线的接口芯片采用江苏南京沁恒电子有限公司的CH365.它将32位PCI总线转换为类似于ISA总线的8位主动并行接口,使用方法简单,非常适合用于短周期PCI接口卡制作.CH365支持以字节、字或双字为单位的I/O段口或存储器读写,存取速度高达7 MB,其接口框图如图2所示.

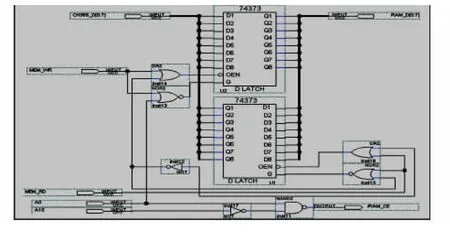

由于CH365地址总线为16位、数据总线为8位,而IDT70V25地址总线为13位、数据总线为16位,所以需对CH365进行数据总线扩展.其基本思想:CH365对IDT70V25进行读数据时,双口RAM的高8位数据直接读入CH365中,低8位数据锁存在FPGA中,下一时序再将低8位数据从FPGA中读入CH365;CH365对IDT70V25进行写操作时,低8位数据先锁存在FPGA中,下一时序写高8位数据时,使能FPGA中的低8位数据输出信号,将16位数据一起写入IDT70V25中,如图3所示.

用FPGA实现锁存器,CH365的地址线A0用作使能信号,完成16位数据分时读写.CH365读时,A0为高电平,高8位数据直接读取,低8位锁存到U1;CH365再读一次时,A0变为低电平,RAM_CE为高电平(无效),U1中锁存的低8位数据送入CH365.CH365写时,A0为低电平,低8位数据锁存到U2;CH365再写一次时,A0变成高电平,RAM_CE、U2使能及OEN信号同时有效,高8位数据连同U2中锁存的低8位数据一起写入双口RAM.U1用于读时的低8位数据锁存,U2用于写时的低8数据位锁存;先读高8位再读低8位,先写低8位再写高8位.

图2 CH365接口框图Fig.2 Interface block diagram of CH365

图3 CH365数据总线扩展配置图Fig.3 Data bus extension configuration diagram of CH365

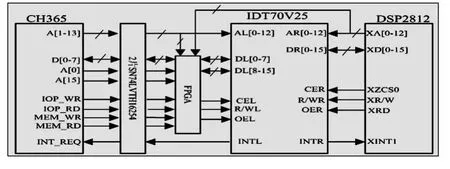

2.2 双口RAM

双口RAM具有两路完全独立的端口,每个端口都有独立的地址、数据和控制线,允许两个端口同时读/写数据,但不允许2端口同时写或一读一写同一地址单元,否则会发生竞争现象[5].本设计选用8 k B×16 B的IDT70V25高速双口RAM,工作电压3.3 V,数据存取时间高达20 ns.

图4 双口RAM硬件原理图Fig.4 Hardware schematics of dual-port RAM

由于CH365没有READY信号线,需要引入仲裁逻辑控制模块解决地址竞争问题.常用的方法有:令牌传递法、基于邮箱机制的INT中断法和插入等待周期的BUSY法等[6].本设计采用基于邮箱机制的INT中断法解决双口RAM地址的竞争问题 .基本原理:在IDT70V25中定义存储单元0000 H为双口RAM与CH365通信端口的中断标志邮箱,8000 H为双口RAM与DSP通信端口的中断标志邮箱,其硬件原理如图4所示.当CH365向左端口写地址单元0000 H时(CEL=R/WL=VIL),通过FPGA逻辑实现INTR(DSP中断)为低,可向DSP发送中断清求;当DSP访问0000H时(CER=OER=VIL),无论读写都可以清除中断标志INTR.同理,当DSP写地址单元8000 H时,INTL(CH365中断)为低,可向CH365发送中断请求;当左端口访问8000 H时,INTL为高,复位DSP发出的中断请求.申请中断时向邮箱写入1,清除中断时向邮箱写0;当信箱内容为1时,表示正在使用该方端口;当信箱内容为0时,表示该端口使用结束.

2.3 DSP系统及其外围电路

DSP采用美国TI公司生产的32位浮点型处理器TMS320F28335.该处理器采用高性能静态CMOS技术,最高主频150 MHz,2个独立的正交编码电路(QEP),12个可配置外部中断[7].

表1 TMS320F28335芯片外存储空间分配表Tab.1 External memory space allocation table of TMS320F28335

2.4 FPGA模块及相关电路

FPGA选择美国Altera公司的CycloneⅡ系列的EP2C8F256C6,包含2个锁相环(PLL)、8个全局时钟、8 256个逻辑单元、182个I/O口.

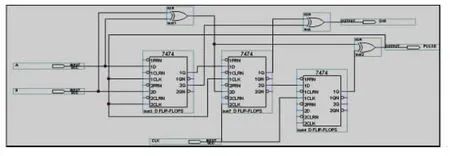

图5 变频脉冲发生模块原理图Fig.5 Module schematic of frequency pulse

2.4.1 变频脉冲发生模块 变频脉冲发生模块主要产生脉冲控制信号,完成精插补功能.该电路模块由时序发生电路和数值分析法(DDA)积分器电路组成,如图5所示.时序发生电路包括分频器和计数器两个部分,分频器根据DSP提供的分频系数对FPGA时钟信号进行分频,分频后的信号送给DDA积分电路,作为DDA积分器的累积时钟信号;计数器对累加时钟进行计数,用于当前插补周期插补终点的判断,当前插补周期的各轴进给脉冲溢出时,计数器会向DSP发送一个中断请求信号,停止本次精插补并加载下一周期精插补数据[9].DDA积分器电路主要由累加器、被积函数寄存器和脉冲输出控制器组成.被积函数寄存器存放终点坐标,累加器存放累加值,累加器每溢出一次产生一个脉冲信号,脉冲输出控制器控制脉冲信号以脉冲/方向或者正/反转方式输出;累加器溢出的频率,即为电机驱动脉冲的频率.每一个进给轴对应一个DDA积分器,每个DDA积分器的原理相同.

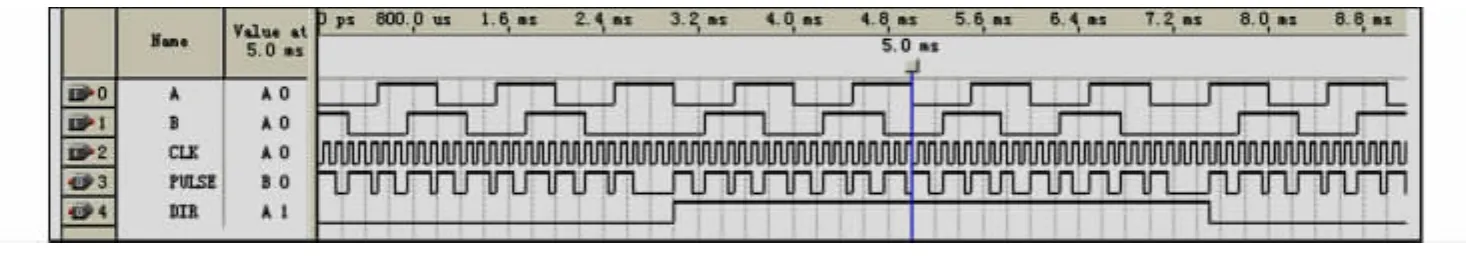

2.4.2 编码器接口模块 采用增量式光电编码器作为检测反馈元件,根据其旋转方向由可逆计数器对脉冲进行加减计数.FPGA的编码器接口模块主要由4倍频及鉴相电路、可逆计数器和位置寄存器组成,可逆计数器根据4倍频及鉴相电路的方向信号对计数脉冲进行加计数或减计数,计数结果保存在位置寄存器中,以供DSP读取或清零.4倍频细分及鉴相电路的原理和时序仿真,分别如图6,7所示.

图6 4倍频细分及鉴相电路原理图Fig.6 Schematics of four interpolated and phase circuit

由于FPGA不能直接处理差分信号,所以编码器的反馈信号需经SN75175将差分信号转换为单极性信号,再经光电隔离和电平转换后输入到FPGA中.编码器反馈的差分信号1A+,1A-转换为单极信号1A,经光耦6N137隔离输出Fback_M1A信号到电平转换芯片(图7).

图7 4倍频细分及鉴相电路时序仿真图Fig.7 Timing simulation diagram of four interpolated and phase circuit

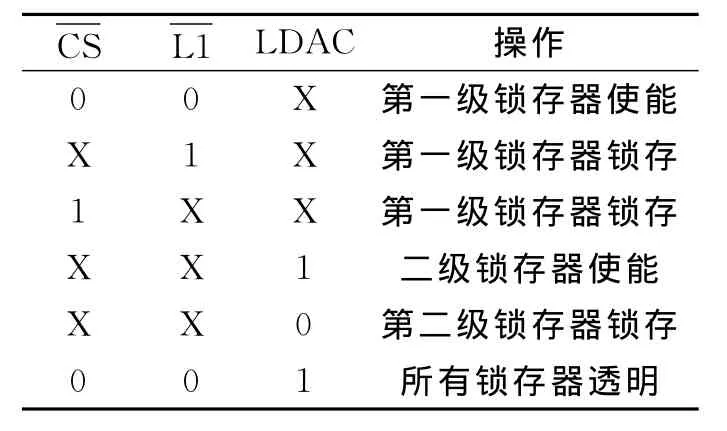

2.4.3 DA转换电路 FPGA输出的是数字信号,为实现模拟电压输出,需要DA转换芯片.DA选用美国AD公司推出的16位并行高性能模数转换器AD669,它在单片芯片上包含双缓冲锁存,转换锁存的脉冲宽度为40 ns,输出电压极性有0~10 V或-10~+10 V可选,且电压幅值可编程,在整个工作温度区域内具有±1 LSB的最大线性误差,总的谐波失真加噪声为0.009%.

表2 AD669的控制逻辑真值表Tab.2 Logic control truth table of AD669

3 软件设计

3.1 插补算法

插补是实现运动轨迹控制的核心,常用的插补方法有两类:脉冲增量插补法和数据采样插补法.常用的脉冲增量插补算法有逐点比较法、DDA等.DDA插补算法运算速度快,脉冲分配均匀,易于实现多轴联动控制,应用比较广泛[11].数据采样插补法的过程一般分两步完成.第一步是粗插补,在给定曲线的起点与终点间插入若干个点,首尾连接这些点,用这些微小直线段来逼近给定曲线;第二步为精插补,对粗插补中的每个微小直线段进行密化,相当于直线的脉冲增量插补[12].

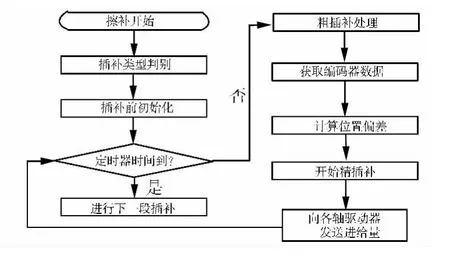

本设计采用时间分割法完成粗插补,DDA完成精插补,粗插补在DSP中实现,精插补在FPGA中实现.时间分割法插补算法的具体实现是根据工件的进给速度F,以插补周期T为时间单位,将整段加工过程L分割成许多小段ΔL,并将其分解到各个坐标轴,得到本周期内各轴方向的进给量;然后,根据不同插补类型和已知插补点坐标,计算出下一个插补周期的插补点坐标.FPGA接收DSP运算的各轴进给量,采用DDA插补算法转换为正负进给脉冲信号或者脉冲/方向信号,完成各轴进给量也即小段直线ΔL插补完成.如此循环,直到整段加工过程L完成后,开始下一过程加工 .整个插补软件流程,如图8所示.

3.2 上位机与控制器通讯

图8 运动控制器插补软件流程图Fig.8 Software flow chart of motion controller interpolation

CH365芯片提供了基于DOS的开源驱动函数库(CH365dos.c和CH365dos.h)和基于 Windows的驱动程序及动态链接库.在DOS和 Windows 9X操作系统下,采用VC++6.0开发程序时可直接调用CH365dos.c中的函数,实现对控制器的驱动和控制.在 Windows 2000/XP系统下,首先安装CH365驱动程序CH365WMD.INF,正确安装好驱动后,在程序中添加CH365DLL.H头文件,并把CH365DLL.H文件拷贝到程序的工程目录下,调用CH365DLL中封装的相应函数库即可实现PC机与运动控制器的通信.

4 结束语

设计一种基于DSP和FPGA的通用三轴运动控制器硬件平台,并完成了相应软件的设计与实现,并在研华610G工控机、安川Σ-V驱动器、安川SGMJV-08ADD6S伺服电机得到应用.该控制器采用高性能浮点DSP提高了数控加工精度;结合时间分割法和数值积分法插补算法,缩短了伺服周期,提高了加工速度和多轴联动控制难度;采用FPGA模块化设计增加了系统设计的灵活性和开发性.此外,由于选用了国产CH365接口芯片,在满足PCI高速通讯的同时,也降低了设计成本.

[1] XU Xiao-ming,LI Yi,SUN Ji-hong,et al.Research and development of open CNC system based on PC and motion controller[J].Procedia Engineering,2012,29:1845-1850.

[2] 张崇巍,李汉强.运动控制系统[M].武汉:武汉理工大学出版社,2002:85-98.

[3] KEMAL M C.TOMIZUKA M.Friction modelling and compensation for motion control using hybrid neural network models[J].Engineering Applications of Artificial Intelligence,2007,20(7):898-911.

[4] 舒志兵.交流伺服运动控制系统[M].北京:清华大学出版社,2006:144-145.

[5] 李新建.基于PCI总线的多轴运动控制卡的设计[D].南京:南京航空航天大学,2007:20-21.

[6] 李新建,薛重德,张志林.用CH365实现PCI总线与DSP的通信[J].单片机与嵌入式系统应用,2006(12):25-28.

[7] Texas Instruments.Literature number:SPRZ272E TMS320F2833X,TMS320F2823X digital signal controllers(DSCs)data manual[S].Texas:Texas Instruments Incorporated,2007:35-45.

[8] 申子星,冯丽辉.基于DSP的供电电源电路设计[J].昆明理工大学学报:理工版,2005,30(5A):219-221.

[9] 张宇.基于DSP和FPGA的运动控制卡的研究与设计[D].南京:南京航空航天大学,2007:44-46.

[10] 石江华.基于DSP与FPGA的四轴运动控制器设计与研究[D].北京:北京邮电大学,2012:30-31.

[11] 李恩林.数控系统插补原理通论[M].北京:国防工业出版社,2008:75-78.

[12] 李斌,李曦.数控技术[M].武汉:华中科技大学出版社,2011:104-105.