一种用于12位250MSPS流水线ADC的中频采样前端

2014-02-06钱宏文陈珍海于宗光

钱宏文,陈珍海,于宗光

(中国电子科技集团第58研究所,无锡 214035)

0 引 言

近年来,高速高精度的模数转换器(ADC,analog to digital converter)在高清视频、3G通信、医疗器械,以及雷达等领域得到了广泛的应用,在流水线ADC的诸多实现技术中,开关电容技术一直是应用最为广泛的实现方式。随着CMOS工艺技术的不断进步,通过采用各类新颖的设计技术,基于传统开关电容技术的流水线ADC已经可以达到16位160 MSPS以上[1,2]。

采样保持电路处于流水线ADC的最前端,用于完成对模拟信号由连续到离散的转换过程。其性能是整个转换器的最高性能,并且具有不可修正性,是制约Pipeline ADC系统速度、精度和线性度指标优势的瓶颈[3]。根据奈奎斯特采样定理,随着输入信号频率与采样时钟频率的大幅度提高,采样保持电路的响应速度也需要进行相对应地提高;而其响应速度提升的核心工作和限制就是开关电容技术所依赖的高增益带宽积运算放大器的响应速度和精度的提高。在标准的CMOS工艺条件下,该类运算放大器的性能的提升遇到了越来越多的限制。采用中频欠采样技术可以极大降低采样保持电路的响应速度要求[4,5]。

1 采样保持电路结构

采样保持电路是流水线ADC的与片外模拟信号联系的最前端模块,是流水线ADC设计过程中至关重要的环节,其性能将会很大程度上限制整体ADC动态特性。目前高速、高精度的采样/保持电路主要有电荷重分配型和电容翻转型两种结构。

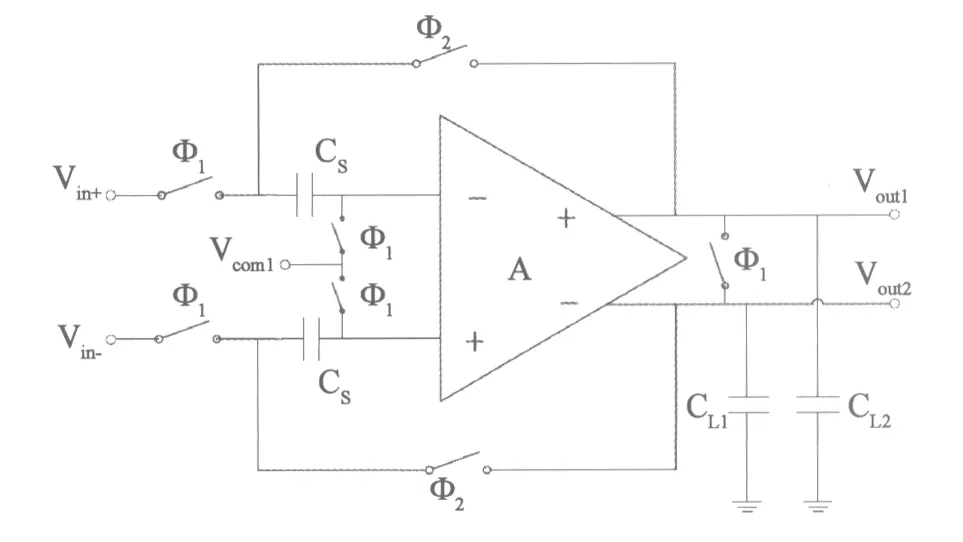

电荷重分配型采样/保持电路一共需要4个电容来完成工作:2个采样电容和2个反馈电容。在输入和输出端各有一个共模电压,因此可以设计让输入和输出端的共模不同,这样减轻了对运算放大器共模电平设计的难度。但电荷重新分配式采样/保持电路需要四个大电容才能获得足够的线性度要求,这样,将会占用很大的面积,并增加成本。还需要将采样电容与反馈电容的值设计为相等,为使反馈系数很小,还对运算放大器频率参数特性的要求更加苛刻。而电容翻转型采样/保持电路只需电荷重新分配式一半的电容,且反馈系数接近于1,减小了运算放大器单位增益带宽的要求。设计中采样前端的速率达到250 MSPS,对于运算放大器的带宽要求极高,为降低运算放大器单位增益带宽要求,因此采样前端采用的设计方案是采用全差分底板采样的电容翻转式结构[7],如图1所示。

图1 采样保持SH电路的结构

图1中Φ1和Φ2是两相互不交叠时钟。实际的开关不能完全消除时钟馈通效应和沟道电荷注入对电路的影响,所以当开关断开和闭合时,开关电路就会产生电荷的注入或抽取。当采样电容较小的时候,电荷的注入和抽取会影响采样精度。为解决这个问题,研究中通过引入辅助时钟Φ1’来配合主时钟进行采样保持,以消除由于电荷的注入或抽取给电路带来的影响。

2 关键电路实现

2.1 SHA

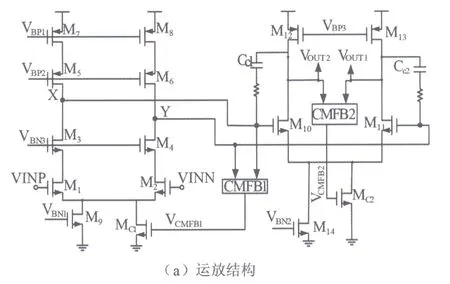

对于开关电容型流水线ADC电路来说,采样保持电路与MDAC电路最核心的模块是高性能的运算放大器,运算放大器的设计主要是在精度、速度和功耗三方面指标的折中设计和考虑。所设计的12位流水线ADC采样时钟为250 MHz,故其转换周期为4 ns。由于双向非交叠时钟的因素,实际中留给信号保持的时间小于2 ns,要获得12位的精度运算放大器需达到80 dB增益和2.5 GHz的单位增益带宽。

为获得足够的增益指标,同时最大化模拟信号摆幅,该研究所用运放采用两级全差分结构,如图2所示。第一级采用套筒式结构,为了获得足够的相位裕度,第一级与第二级之间采用米勒补偿技术。图2(a)为设计的两级式运算放大器结构图。为了获得大带宽,采用NMOS管作为输入对管。第一级和第二级电路分别采用了各自的共模反馈电路,共模反馈形式为连续时间方式,以取得最快速度。图2(b)为该运放的仿真结果,可以看出增益为80 dB,单位增益带宽达到了3 GHz。

图2 采样保持运放

2.2 中频采样开关

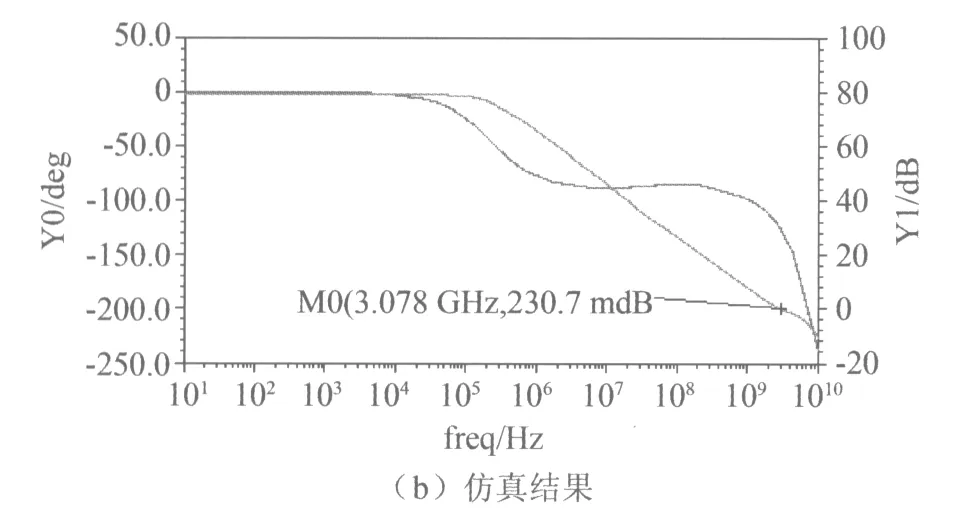

对于采样开关的实现通常采用栅压自举开关,栅压自举开关电路,如图3所示。

图3 栅压自举开关电路

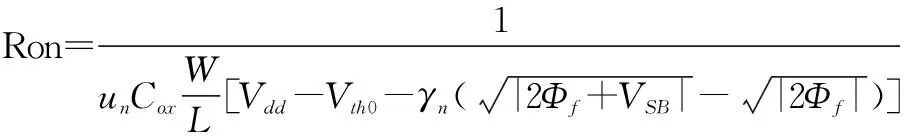

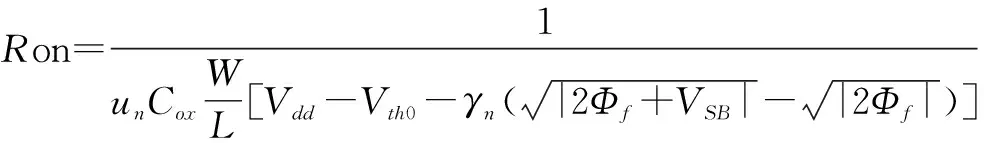

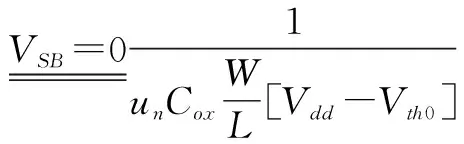

图3(a)为基本栅压自举开关,该开关的导通电阻可表示为

从暴雨发生的风场背景来看,苍南地区8日20时(图2a)850 hPa仍为偏东气流,流场速度<12 m/s,到9日08时(图2b),研究区域上空已转为东南气流,风速>12 m/s,低空急流轴压至,说明东南风急流在8日20后开始逐渐建立,苍南位于低空急流出口区的右侧,十分有利于上升运动。到9日20时(图2c)虽风速所有减弱,但仍维持东南气流,与实况中降水仍持续相符合。到10日08时(图2d),急流形势维持但对应的风向已转为偏南风,说明水汽输送渠道变弱,对应的降水实况为间歇性小的阵性降水。

(1)

研究中采用的高线性度CMOS自举开关电路如图3(b)所示,其对图3(a)所示基本自举开关的主要改进是:保持图3(a)所示开关连接方式不变,增加了一个由MOS管M11和M12构成的采样MOS开关管衬底电压切换电路,消除了衬底偏置电压VSB相关的非线性特性,以进一步提高线性度。

电路工作原理如下:时钟CK为高电平时, M2、M6导通,M7截止,M4导通,使得M1也导通;电路通过M1和M2对电容C1充电,使得电容C1两端的电压接近电源电压VDD,从而在电容Cl上存储了VDD*C1的电量;同时,M11截止,M12导通,采样开关MOS管Ms截止,Ms衬底接地。当时钟CK从高变低时, M2、M6截止,M7导通,M4导通;电源通过M4、M7对结点G的对地寄生电容充电,使得结点G电压升高,MOS管M1截止,M5、M3导通;输入信号通过M3抬升电容C1下极板电压直到其值等于输入电压Vin;由于电容C1上存储的电荷在时钟CK变化过程中没有放电回路,存储在其上的电荷保持不变,电容Cl上极板的电压就会同步上升,直到其值等于VDD+Vin,开关管Ms栅源电压为电源电压VDD;同时,M12截止,M11导通,采样开关MOS管Ms导通,Ms衬底接输入节点Vin,这样MOS管Ms的衬偏电压对其阈值电压的影响被消除(VSB=0)。

根据式(2),此时导通电阻为

(2)

比较式(2)和式(1),可以看出改进的自举开关的导通电阻Ron只与电源电压Vdd、MOS管载流子迁移率un、单位面积栅氧化层电容Cox、MOS管宽长比W/L和MOS管衬偏电压为0时阈值电压Vth0有关,因此具有更高的线性度。

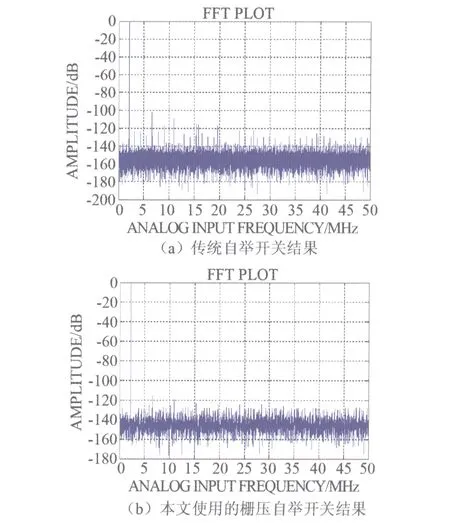

将图3(b)和图3(a)所示自举开关分别作为采样开关应用于图1所示采样电路进行仿真,仿真条件、输入信号和采样信号保持不变。两个开关对应的MOS管取相同的尺寸。对两种开关采样结果做FFT频谱分析得到输出频谱,如图4所示。可以看出图3(b)开关的SFDR为116.7 dB,比图3(a)开关的101.5 dB高了约15 dB,说明本文改进的自举开关比传统的白举开关有更好的线性度。

图4 FFT结果对比

3 测试结果

一个12位250MSPS流水线ADC芯片电路的实物放大照片,如图5所示,电路采用0.18 μm 1P5M 1.8 V CMOS工艺,具体关键模块的布局如图中所示。所设计的SHA电路运用于该ADC电路的最前端,整个ADC电路功耗为320 mW,而SHA电路的功耗为58 mW。

图5 流水线ADC芯片照片

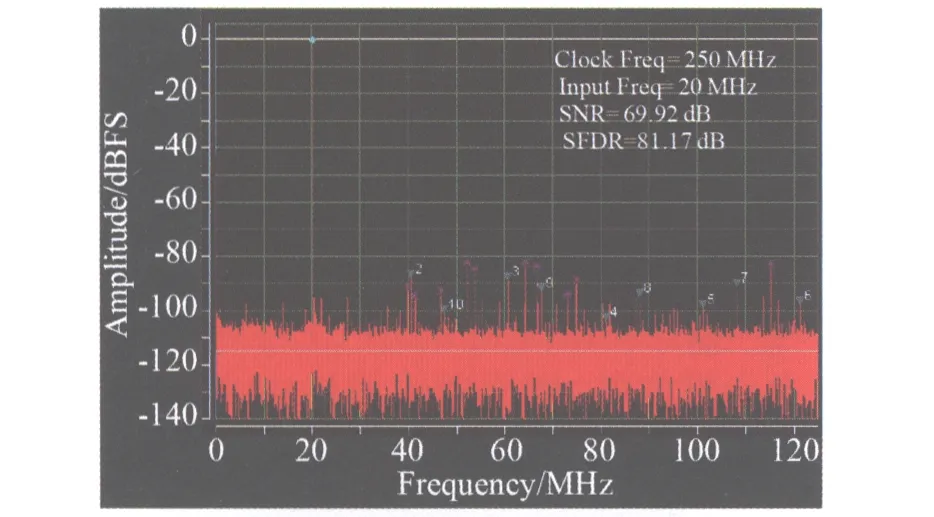

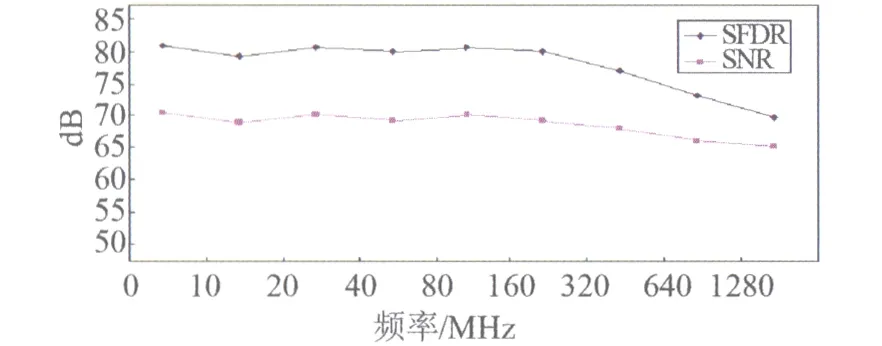

运用了所设计的12位250MSPS流水线ADC的典型FFT测试结果,如图6所示,输入为20 MHz正弦信号,峰峰值为2 V,幅度为-1 dBm,测得SNR为69.92 dB,SFDR为81.17 dB。ADC在250 MHz全速采样条件下模拟输入带宽特性,如图7所示,可以看出ADC模拟-3 dB带宽达700 MHz以上。可以看出,所设计的ADC在未采用数字校准技术条件下达到了非常不错的动态性能。

图6 ADC性能FFT测试曲线

图7 ADC动态性能随输入信号频率变化曲线

4 结 语

设计了一种基于标准CMOS工艺的具有欠采样功能的高速采样保持电路。此电路可以完成信号频率高于时钟频率的采样过程,同时,其输出可以直接应用在高速的模数转换器中。对于固定带宽的输入信号,采用的欠采样技术极大地提高了模数转换器的输入信号频率的范围,可以广泛应用在中频采样系统中。

[1] AHMED M A ALI,MORGAN A,DILLON C.,et al.A 16-bit 250-MS/s IF Sampling Pipelined ADC with Back-ground Calibration[J].IEEE J.Solid-State Circuits,2010,45(12):2612-2613.

[2] PAYNE R,CORSI M,SMITH D,et al.A 16-Bit 100 to 160 MS/s SiGe BiCMOS Pipelined ADC With 100 dBFS SFDR[J].IEEE J.Solid-State Circuits,2010,45(12):2613-2622.

[3] CENTURELLI F,MONSURR6 P,PENNISI S,et al.Design solutions for sample-and-hold circuits in CMOS nanometer technologies[J].IEEE Transactions on Circuits and Systems-II:Express Briefs,2009,56(6):459-463.

[4] SUMANEN L.Pipeline Analog-to-Digital Converters for Wide-Band Wireless Communications[D].Finland:Helsinki University of Technology,2002.

[5] HISTORY R G.Trends in Analog Circuit Challenges at the System Level[C]//2010 International Symposium on Electronic System Design(ISED),2010:24-24.

[6] CHEN ZHENHAI,QIAN HONGWEN,HUANG SONGREN,et al.A 68mW 10-bit 250MSPS Time-Interleaved Charge Domain Pipelined ADC[J].Journal of Semiconductors,2013,34(6):035006-1.

[7] HAITAO WANG,HUI HONG,LINGLING SUN,et a1.A sample-and-hold circuit for 10-bit 100MS/s pipelined ADC[C]∥IEEE International Conference on ASIC(ASICON).Xia Men,China:IEEE,2011:480-483.