基于FPGA双路EnDat2.2编码器的接口设计

2014-02-05孙大海

孙大海,艾 华

(1. 中国科学院 长春光学精密机械与物理研究所,吉林 长春 130033;2. 中国科学院大学,北京 100049)

1 引 言

光电编码器是一种光、机、电紧密结合的精密数字位移传感器,已经广泛应用于数控机床、回转台、伺服传动、机器人、雷达、军事目标测定等装置和设备中,并在工业、国防、航天等部门起着关键作用[1-2]。光电编码器主要分为增量式和绝对式2种。增量式编码器通过计数设备确定其位置,而绝对式编码器的每个机械位置对应于一个惟一的绝对编码,所以它无需记忆。绝对式编码器在抗干扰和可靠性方面大大优于增量式编码器, 所以绝对式编码器在测量系统中的应用更广泛。但是绝对式编码器每一次输出的数据量较增量式编码器多而复杂,由于精度高、位数多的特点决定绝对式编码器通信方式只能采取串行传输方式,而且还要遵循一定的通信协议。目前世界上几大主要的编码器生产厂商都有自己的一套通信协议,如Heidenhain公司的EnDat协议,Danaher公司的Biss协议,SICK|STE- GMANN公司的HIPERACE协议等等[3]。其中Heid enhain公司推出的EnDat接口因其高可靠性、低成本而得到世界各大数控厂商的认同,现在EnDat2.2接口已经发展成为绝对式编码器的标准协议。

Heidenhain公司为其编码器配套了相应的接收板卡,自动完成串行编码到并行编码的转换,方便了控制器的读取操做。但该板卡价格昂贵,大约占绝对式编码器价格的四分之一。为满足了对EnDat2.2接口的需要和代替价格高昂的专业接口板卡,本文先是分析了EnDat2.2协议的传输格式,基于FPGA(现场可编程逻辑器件)设计了双通道EnDat2.2接口电路,可以同时对两个支持EnDat2.2协议的绝对式光电编码器进行控制和读取。

2 Endat2.2协议简介

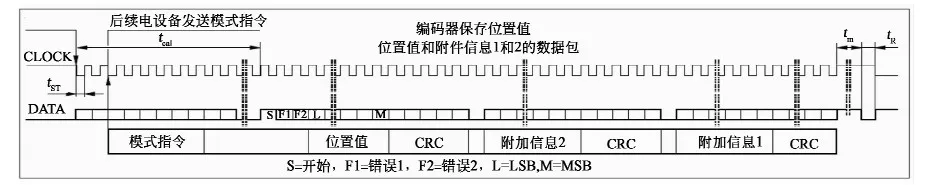

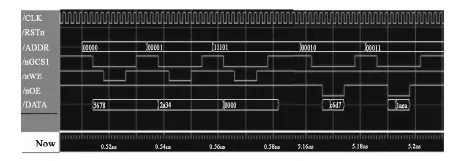

海德汉公司的EnDat数据接口是用于编码器的数字式、全双工同步串行接口。电气连接需要一对电源线,一对差分的数据线,一对差分的时钟线,数据传输与FPGA发出的时钟信号保持同步[4],采用“一问一答”的主从通信方式。图1是Endat2.2的典型时序图。

图1 包括附加信息的位置值数据包Fig.1 Packet including position values with additional information

传输周期从第一个时钟下降沿处开始启动,编码器开始计算位置值并保存测量值。两个时钟脉冲(2T) 后,FPGA开始发送模式指令。编码器的绝对位置值成功计算完后,编码器从起始位开始向FPGA传送数据。紧接着的错误位,“F1”和“F2”是监测信号,用于监测故障。这两位信号是相互独立产生的,它显示编码器是否发生了可导致不正确位置值的故障。然后绝对位置值从最低有效位(LSB) 开始传送。它的长度取决于所用的编码器。每次传输位置值均以CRC 结束,在附加信息1 和2的数据传输结束后也进行循环冗余检查。存储区域码( MRS码) 决定了附加信息的内容。在数据传输结尾处,时钟信号必须置为高电平。10~30 μs后或1.25~3.75 μs后数据线返回低电平。当检测到时钟信号的下降沿时,将启动下一次的数据传输[4]。

3 EnDat2.2接口电路的设计方案

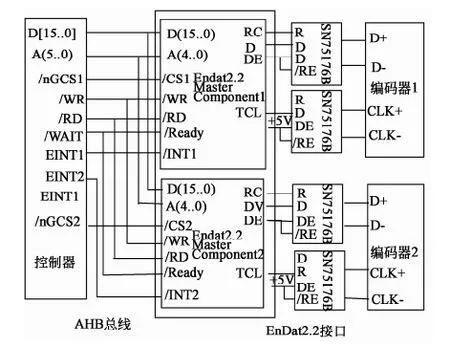

系统电路原理图如图2所示,其中使用FPGA开发的双路独立EnDat2.2译码模块,可以连接两个编码器,而且两个模块彼此独立,互不占用对方资源,可以同时工作,保证了编码器的通信速度和可靠性。用FPGA实现接口电路功能,不但可以使控制器只专注于相关的控制算法运算而且接口电路本身也具有很好的独立性。

图2 接口电路原理图Fig.2 Interface circuit diagram

编码器与FPGA的收发电路采用RS485电气接口标准规范,RS-485接口是采用平衡驱动器和差分接收器的组合,具有抗干扰能力强,通信速率快,传输距离长等优点。本文使用专门用于RS485接口的SN75176B芯片,如图2所示,该芯片是一种半双工的器件。每一路编码器使用2个SN75176B芯片,一个用于向编码器传输同步的差分时钟信号CLOCK,该SN75176B芯片只工作在发送模式;另一个用于编码器和FPGA之间的数据信号(DATA)传输,该SN75176B芯片处在半双工工作模式。

4 FPGA接口模块的数据读取原理

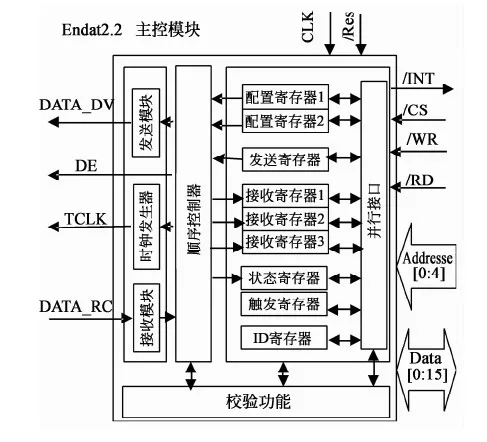

图3 接口电路功能框Fig.3 Function block of interface circuit

如图3所示,为了方便FPGA程序的设计和调试,将整个接口电路按照功能进行模块化,主要由发送模块、接收模块、时钟发生器、校验模块、各种功能寄存器及并行接口、顺序控制器等功能模块组成[5]。发送模块、接收模块和时钟发生器主要负责与编码器的通信,框图的左侧是EnDat接口的4根通信引脚,产生符合Endat2.2协议的数据传输时序和波特率。顺序控制器是顶层模块,用于协调各个模块的工作流程,使得负责不同功能的模块按照一定顺序和条件工作,该模块既要实现配置寄存器对发送模块和接收模块的配置,又要将接收模块接收的数据经过CRC校验后送到相应的接收寄存器中。接下来从3个方面介绍FPGA的程序设计。

4.1 Endat2.2串行接口在FPGA上的设计

在上电或复位后,时钟线TCLK为保持高电平,当顺序控制器启动数据传输后,首先使能时钟发生器产生0.5 μs的方波信号作为通讯的同步时钟信号。对于每一次数据传输,在时钟的第二个下降沿激活FPGA内发送模块,按照时钟的下降沿通过引脚DATA_DV依次发送6位模式指令,或6位模式指令和24位参数,在紧接着的下一个时钟下降沿发送模块被关闭,接收模块被激活,开始检测输入引脚DATA_RC的上升沿,当检测到起始位S的上升沿后,开始接收2个“错误位”F1、F2,25个位置值和5位CRC校验码,或接收24位参数和5位CRC校验码,并在时钟的下降沿保存输入的数据。最后关闭时钟发生器,但时钟线和数据线仍要维持高电平,经过恢复时间3 μs后数据线返回低电平,时钟线的高电平一直持续到下一次数据传输。接收到的位置值经过校验模块检测后,从A端口写入双口RAM中,从而FPGA与编码器的一次通讯过程就结束了。

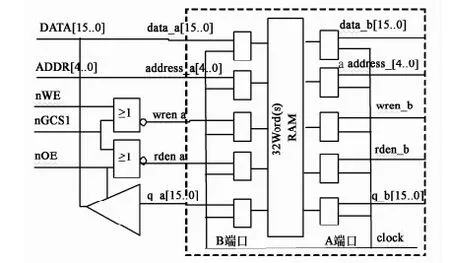

4.2 并行接口在FPGA上的设计

图4 AHB总线读写操作时序图Fig.4 AHB bus timing diagram for read and write operations

图4为并行总线的读、写操作时序图。并行总线时序的设计就是并行接口的设计,使FPGA内部寄存器能被控制器访问到。在FPGA内部实现了64个字节的双口RAM空间,本文采用了对双口RAM的A端口进行封装实现并行总线接口的设计,设计方法如图5所示,在图5的左侧是并行接口的通信控制信号,它提供5位地址信号和16位数据信号与控制器进行16位的数据传输。图6为该端口的ModelSim读和写时序仿真图,由图可知该端口的读写符合并行总线的时序。

图5 AHB接口设计图Fig.5 AHB interface design schematics

图6 AHB接口的ModelSim仿真波形图Fig.6 AHB interface’s ModelSim simulation waveform

4.3 CRC校验在FPGA上的算法设计

为了提高数据传输的可靠性,EnDat2.2在传输数据时,其后面还跟随着5位CRC校验码,接收端通过校验码,判断数据在传输过程中是否由于干扰等原因而出现误码。

图7 循环冗余码编码原理Fig.7 Coding theory of cyclic redundancy code

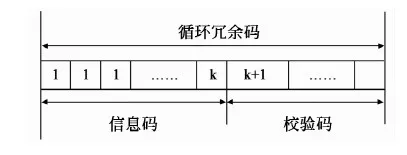

循环冗余码原理:

编码器输出的循环冗余码分为信息码和校验码两个部分,如图7所示。设K(X)为信息码多项式,R(X)为校验码多项式,G(X)为预先约定的生成多项式。信息码长为k位,校验码长为r位,则循环冗余码长为n=k+r位。

(1)发送端的编码过程:

通过xr-1K(X)/G(X)=Q(X)+R(X)/G(X),求得R(X)的值,令T(X)=xr-1K(X)+R(X)作为循环冗余码发送出去。

(2)接收端的校验过程:

接收方收到循环冗余码后,做如下处理:

T(X)/G(X) =xr-1K(X)/G(X)+R(X)/G(X)=

Q(X)+R(X)/G(X)+R(X)/G(X)=Q(X)

此时T(X)/G(X)余数为0。所以判断数据在传输过程是否出错依据就是判断T(X)/G(X)的余数是否为0。如果T(X)/G(X)的余数为0,则T(X)传输正确,若不为0,T(X)传输时出错了。

下面是用 Verilog HDL代码实现接收端循环冗余校验的主要源程序,生成多项式为G(x)=x5+x2。

……

always @(posedge CLK)

begin

data=input;

if(data[25])data[25:20]=data[25:20]^6'b100100;

……

if(data[6])data[6:1]=data[6:1]^6'b100100;

if(data[5])data[5:0]=data[5:0]^6'b100100;

if(data[4:0]^crc5) begin error<=1;end

else begin error<=0;end

end

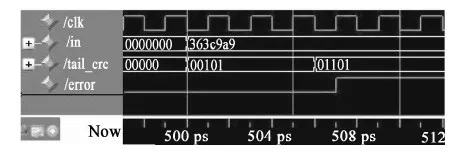

利用ModelSim仿真工具对程序进行了仿真, 如图8所示,输入26位信息码0x363c9a9和5位校验码00101,通过error=0显示该信息码是准确的,这与理论计算的结果一致,当校验码为01101时,error=1提示信息码是错误的。

图8 CRC校验程序的仿真图Fig.8 Simulation diagram for procedure of CRC checksum

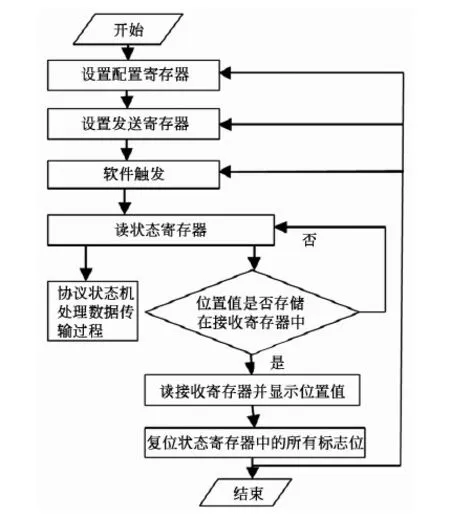

4.4 接口工作流程

一次完整的接口电路工作流程如图9所示,首先控制器对配置寄存器进行配置,设置串口传输速率和编码器的位数;向发送寄存器写入模式指令及参数,然后通过软件触发方式(向触发寄存

图9 EnDat接口工作流程图Fig.9 Flow chart of EnDat interface

器写入任意数),FPGA开始向编码器发送指令及参数,接下来等待接收编码器反馈回来的位置值或参数值,该值经过CRC校验后存入接收寄存器中,并更新状态寄存器,使相应的状态位置位,控制器通过查询状态寄存器查看是否接收到编码器的位置值或参数,接收到后控制器从接收寄存器中读取并显示,最后复位状态寄存器准备下一次的数据传输。

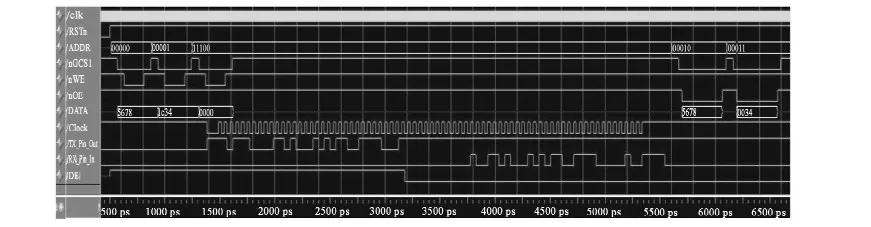

5 实验比对

本文从软件仿真、准确性对比、传输速度3个方面对该接口进行了测试。由于两路接口功能一样,所以只列出FPGA接口中的一路接口的Modelsim软件仿真图,图10为FPGA的工作时序波形图。由图可知,首先是通过AHB总线向发送寄存器发送模式指令(编码器接收参数011100)及参数(0x345678),然后向触发寄存器写入任意数来启动FPGA,使之按照EnDat2.2的时序传输指令及参数,最后从接收寄存器中读出编码器反馈回来参数值。如图可知此参数值与写入参数值一致,说明FPGA的AHB接口和EnDat2.2接口设计达到了通信目的。

图10 FPGA的ModelSim仿真波形图 Fig.10 ModelSim simulation waveform of FPGA

本文设计的接口在海德汉公司生产的支持EnDat2.2协议的绝对式光栅尺LC181上进行了应用,LC181是一种测量线性位移的25位编码器,测量步距从1~0.1 μm,量程为2 040 mm,最大移动速度120 m/min。海德汉公司制作的IK220是一个借助个人计算机进行直线和角度测量用的计数卡。可连接两个海德汉EnDat2.2接口的编码器。用它与本论文设计的接口电路同时测量绝对式光栅尺LC181的位置值,当游标拉到不同位置时,观察两个测量装置的测量值,经过随机测量对比后,除了最末位数字由于扰动等原因发生跳变外,整个测量结果基本一致,说明本文的接口电路达到了准确传输数据的目的。

图11为用示波器捕捉到的波形图,中间的图是一帧完整的测量波形图,左右两边是放大后的图形,左图为接口发送的模式指令(编码器发送位置值000111),右图为编码器发送的位置值和5位CRC校验码。在测量中,波特率最大可以达到2 Mbit/s,1 s中平均可以传输40个位置值,足可以满足一般应用的需求。这个测试证明了此编码器接口的可行性、可靠性和实时性。

图11 实际应用中的通信时序图Fig.11 Communication timing diagram in the practical application

6 结 论

绝对式编码器和光栅尺作为位移传感器,在自动化领域中应用越来越广泛,它们的发展也向着高精度、高速度,高可靠性发展。系统的实时性的提高,对数据采集、传输和处理带来更高的要求。EDA技术和DSP技术的发展足可以满足这个要求,在本文数据接口设计中,FPGA使电路设计小型化和集成化,大幅减少了电路板的尺寸,降低了成本[6]。在功能上适合于不同位数的编码器,因此具有通用性,具有CRC校验功能,提高了系统的可靠性。如今海德汉公司的EnDat2.2接口的时钟频率最高可达到16 MHz,带有电缆长度补偿,优化了时间条件,提高了对编码器的数据传输速率,使其能用于高精度、高性能的数控领域中[7]。因此,可以看出EnDa2.2协议在高实时性领域里的应用将更受关注。

[1] 刘琳,陈建平.通过ENDAT接口获取绝对编码器位置[J].微电机,2009,42(12):77-79.

Liu L,Chen J P. Access absolute encoder position values via ENDAT interface based on DSP [J].MicromotorsServoTechnique,2009,42(12): 77-79.(in Chinese)

[2] 左洋,龙科慧,乔克,等.航天编码器调试系统显示功能设计[J].液晶与显示,2012,27(6):795-799.

Zuo Y, Long K H, Qiao K,etal.The design of display of debugging system of space encoder [J].ChineseJournalofLiquidCrystalsandDisplays,2012,27(6):795-799. (in Chinese)

[3] 彭雨.基于FPGA的绝对式光电编码器通信接口研究[D]. 武汉:华中科技大学, 2008.

Peng Y. Research about absolute optical encoder communication interface based on FPGA [D]. Wuhan: Huazhong University of Science and Technology, 2008.(in Chinese)

[4] EnDat2.2-bidirectional interface for position encoders [R].Dr.Johannes Heidenhain GmbH,2008.

[5] EnDat2.2-Softmacro For Master Component [R].MAZeT GmbH,2008.

[6] 熊文彬,蒋泉,曲建军,等.基于FPGA实现的视频显示系统[J].液晶与显示,2011,26(1):92-95.

Xiong W B, Jiang Q, Qu J J,etal.Realization of the video display system based on FPGA [J].ChineseJournalofLiquidCrystalsandDisplays,2011,26(1):92-95..(in Chinese)

[7] 谢礼忠.EnDat接口编码器数据采集设计方案[J].金属加工(冷加工),2009(2):59-60.

Xie L Z. Design of data collection about EnDat interface encoder [J].MachinistMetalCutting,2009(2):59-60.(in Chinese)