基于CPLD的继电器测试系统设计

2014-02-03高同辉

高同辉, 王 键

(平顶山工业职业技术学院 自动化与信息工程系, 河南 平顶山 467001)

0 引 言

电磁继电器是一种广泛应用于自动控制系统的控制器件。继电器性能的好坏直接影响统能否正常运行,同时继电器的研制与改进都需要对其参数进行准确的测试[1]。但目前继电器测试产品造价昂贵且测试过程复杂,因此需要设计出具有操作方便、界面友好、处理精度较高的电磁继电器自动测试系统。

1 系统设计方案

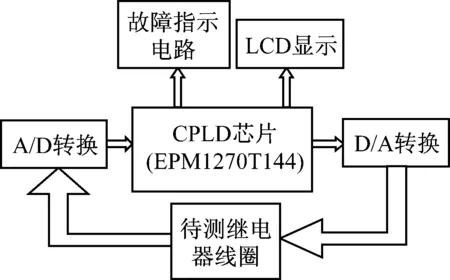

继电器测试系统是针对继电器的动作电压、时间参数以及触点电阻等参数进行测试,测试系统原理结构框图如图1所示,共分为六个部分[2-4]:CPLD芯片、A/D转换、D/A转换、LCD显示、故障指示、电源模块等。

图1 系统原理结构框图

2 硬件设计

2.1 电源模块电路

本设计采用LM7815和LM7915产生±15 V电压,LM7815输出的+15 V又经过LM7805后输出5 V,LM7805输出的5 V又输入到AMS1117-2.5 V和AMS1117-3.3 V芯片[5],产生2.5 V和3.3 V电压提供给CPLD芯片。

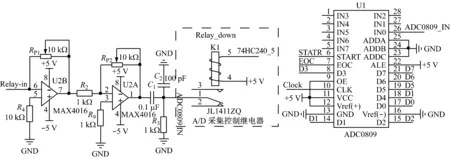

2.2 A/D采集电路

本设计采用ADC0809芯片构成A/D信号采集电路。在测量待测继电器触点电阻时候,施加了一个1 A恒流源,通过ADC0809采集触点两端的电压来计算触点接触电阻。通过一个继电器开关允许触点的电压信号进入A/D转换器的模拟通道IN0。ADC0809时钟来源于50 MHz晶振分频,采用500 kHz的采样频率;CPLD采集ADC0809的EOC信号来判断A/D采集是否已经结束[6-7],A/D采集电路原理图如图2所示。

图2 A/D采集电路原理图

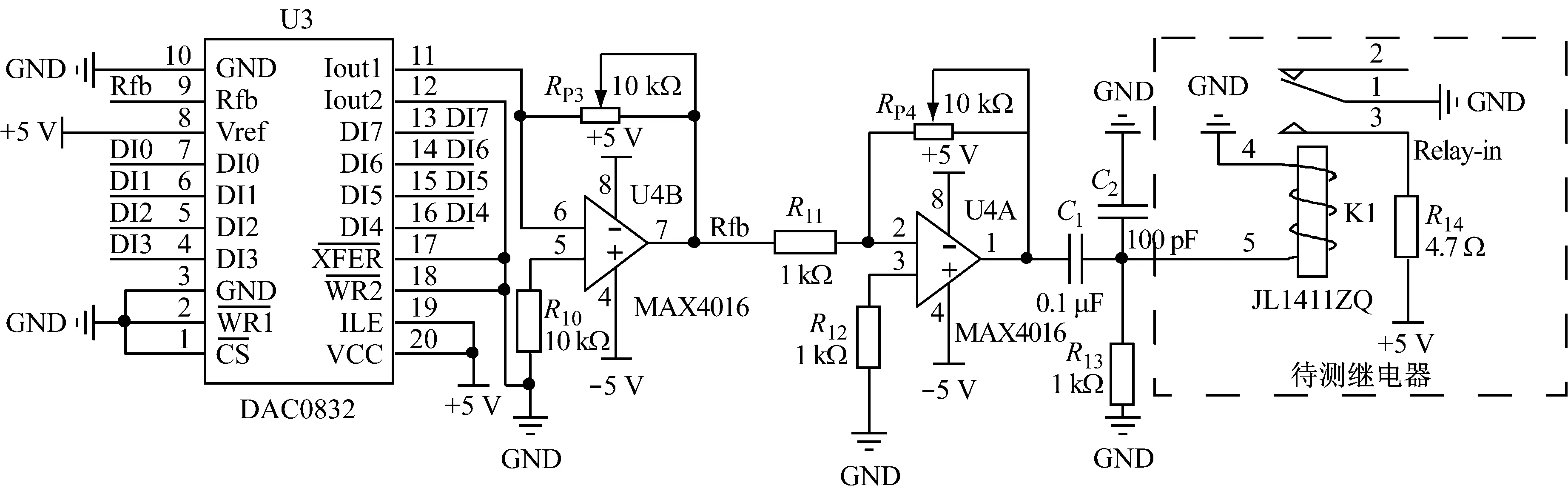

2.3 D/A数据转换电路

采用DAC0832构成D/A转换电路,单极性输出。FPGA直接输出二进制数送到DAC0832上,经过直通方式直接转换成模拟量并通过MAX4016运算放大器[8-9]放大后,施加到待测继电器的线圈上,以达到控制待测继电器的功能,D/A数据转换电路原理图如图3所示。

图3 D/A数据转换电路原理图

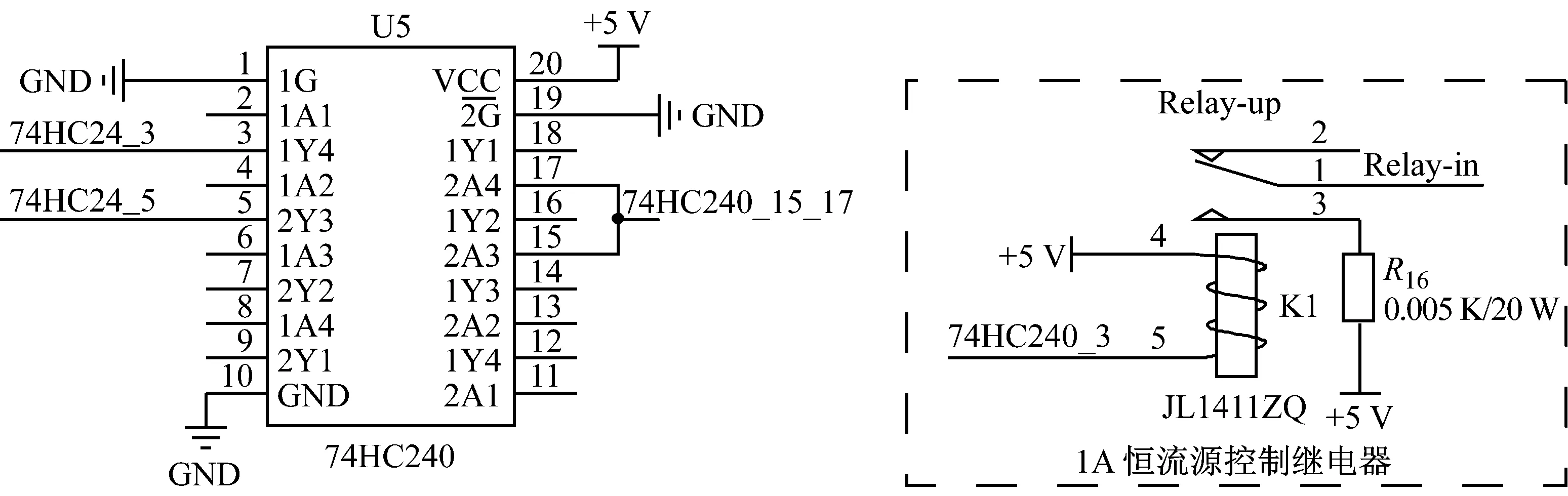

2.4 触点电阻测量电路

在测量触点电阻时,通过外部电源箱的5 V和一个5 Ω/20 W的电阻构成一个接近1 A的恒流源,通过一个继电器开关来控制这个1 A电流是否允许施加到触点上。并通过74HC240缓冲放大器[10]作用,连接至CPLD芯片88脚,待测继电器触点电阻测量电路如图4所示。

2.5 CPLD核心电路

采用Altera公司的CPLD芯片EPM1270T144C5[11]作为核心控制芯片。芯片与外围器件的连接关系见图5所示。继电器各个参数测量原理如下:

测量吸合电压和释放电压时,通过CPLD直接输出0~5 V和5~0 V连续变化的电压数字量,并通过D/A转换电路及放大电路后施加到线圈上,一旦检测到触点闭合或者释放后,CPLD将锁存此时的电压数字值,即相对应的吸合电压和释放电压。

测量吸合时间时,CPLD直接输出12 V电压数字量,经D/A转换及放大电路后直接施加到线圈上,使继电器触点闭合,CPLD记录从输出12 V电平数字量到检测到继电器触点闭合的时间,就是吸合时间。

测量释放时间时,在测量吸合时间后,CPLD则直接输出0 V电压数字量,经D/A和放大电路后施加到线圈上,使继电器触点直接断开。CPLD将记录从送出0 V电平数字量到检测到触点断开的时间,即释放时间。

图4 待测继电器触点电阻测量电路

测量触点接触电阻时,通过外部5 V电源及5 Ω/20 W水泥电阻模拟一个接近1 A的恒流源。CPLD直接输出12 V电压数字量经D/A电路和放大电路后直接施加到线圈上,使继电器触点闭合。一旦CPLD检测到继电器闭合后,分别允许1 A电流进入触点和允许A/D采集触点的电压。采集电压时候,由于触点电压在mV级,需要放大后再进入A/D通道。最后将采集到的电压数字值直接送给CPLD处理计算[12]。

2.6 LCD1602显示电路

LCD1602主要实现电磁继电器的动作电压、时间参数以及触点电阻的显示[13],LCD1602的第15引脚用于控制背光源电源的,设计中是通过CPLD直接控制的,控制电路如图5所示,其中Cont引脚直接接到CPLD上控制其背景亮度。

图5 LCD1602显示电路

3 系统软件设计

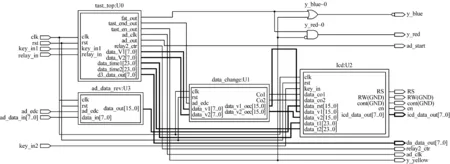

CPLD软件设计采用Verilog HDL[14]硬件描述语言进行设计,程序主要包括系统时钟分频模块、A/D数据采集和处理、D/A数字量输出、LCD1602显示以及按键处理。本设计的RTL级(寄存器传输级)功能模块图[15]如图6所示。

图6 RTL级功能模块图

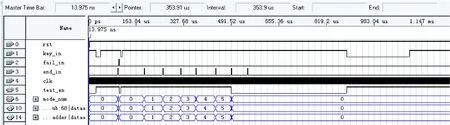

测试状态仿真图如图7所示,mode_num=0表示正在测量继电器的释放时间,此状态下CPLD直接先输出8 bit全1的数字量,后又输出8 bit全0的数字量送给DAC0832。mode_num=1表示正在测量继电器的吸合时间,此时CPLD直接输出8位全1的数字量给DAC0832。mode_num=5时,CPLD输出一个从0V到12V变化的电压数字量给DAC0832,用于测量吸合电压。mode_num=6时,CPLD输出一个从12~0 V变化的电压量给DAC0832,用于测量释放电压。

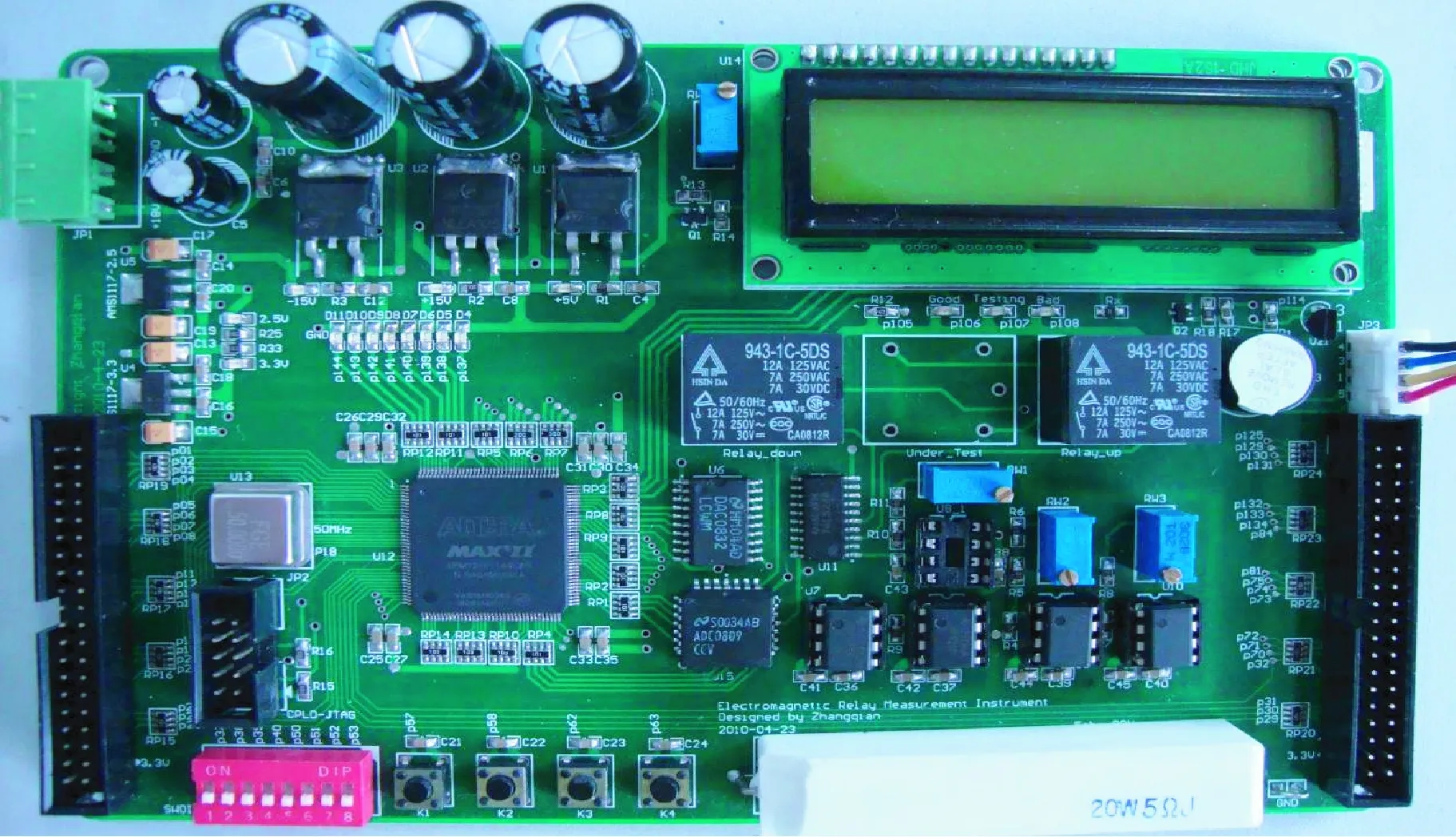

4 实验测试

首先依据硬件电路设计绘制PCB四层电路板,组装焊接调试,本设计的硬件实物如图8所示。其次在QuartusII环境下编译Verilog HDL语言源程序[16],先对EPM1270T144C5进行引脚分配,再进行综合生成可以下载到CPLD的*.pof文件,通过JTAG口将程序下载到芯片中。

图7 测试状态仿真图

图8 硬件实物图

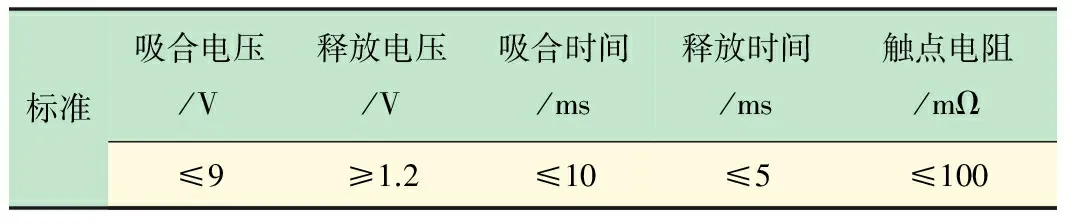

本系统测量的继电器型号为943-1C-12DS。表1是该继电器datasheet上所列出的参数范围。

表1 继电器标称参数

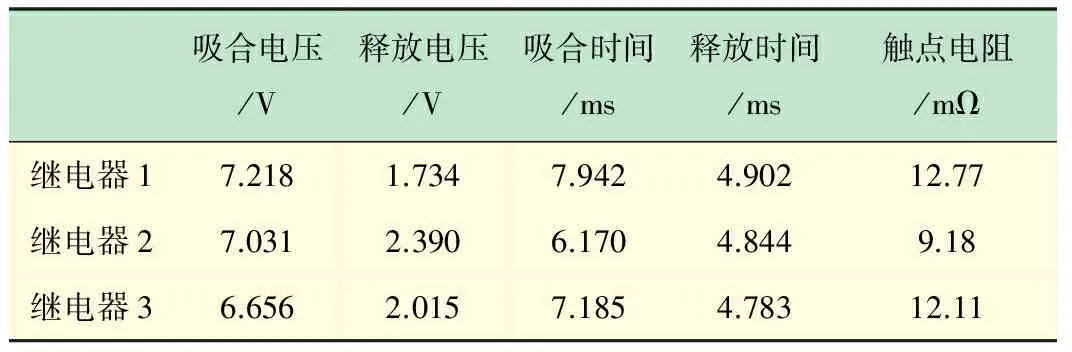

使用本系统测量三个943-1C-12DS型号的继电器的参数如表2所示。

表2 继电器测试参数

测量触点电阻时,PCB板本身回路的电阻为4.1 mΩ。以上数据已经减去了PCB板本身回路电阻。

5 结 语

本文设计的继电器参数测试系统以CPLD芯片为核心,实现整个参数测试仪的信号控制、数据处理、人性化显示功能。对实际测量的参数结果表明,本设计的单刀继电器参数测量仪所测量出的数据完全符合所测继电器的参数指标。

[1] 黄 凯.小型继电器检测装置及其远程控制方法的研究[D].天津:河北工业大学,2007,5.

HUANG Kai. The Study on Testing Apparatus of Mini Relay and Method for Its Remote Control [D]. ??Tianjin: Hebei University, 2007,5.

[2] 郑争兵,魏 瑞,陈正涛.一种基于FPGA的高速数据通道的实验方法[J].实验室研究与探索,2012,31(12):78-81.

ZHENG Zheng- bing, WEI Rui,CHEN Zheng- tao.An Experimental Method for High- speed Data Channel Based on FPGA[J]. Research and Exploration in Laboratory,2012,31(12):78-81.

[3] 袁广超,田旭东.基于CPLD的振弦式传感器的频率测量技术[J].自动化仪表,2009,30(11):63-66.

YUAN Guang-chao,TIAN Xu-dong.Frequency Vibrating Wire Sensor Measurement Technology Based on CPLD[J], Automation Instrumentation,2009,30(11):63-66.

[4] 董振龙,董 惠,吴 锦.基于FPGA的高速ADC测试平台的设计[J].计算机测量与控制,2012,20(9):2372-2374.

DONG Zhen-long,DONG Hui,WU Jin,Design of High-speed ADC Test System Based on FPGA[J].Computer Measurement & Control,2012,20(9):2372-2374.

[5] 彭春燕,曹志辉.基于双DSP与CPLD的继电保护测试仪设计[J].电测与仪表,2009,46(11):40-45.

PENG Chun-yan,CAO Zhi-hui.Design Relay Tester Based on Dual-DSP and CPLD[J],Electrical Easurement & Instrumentation, 2009,46(11):40-45.

[6] 封世领,刘 强,李志强.基于FPGA的超级电容器均衡充电电路设计与实现[J].电源技术,2011,35(5):540-542.

FENG Shi-jie,LIU Qiang,LI Zhi-Qiang.Supercapacitor Charging Circuit Design and Implementation of Balanced Based on FPGA[J]. Power Technology,2011,35(5):540-542.

[7] 肖闽进,何一鸣,鲍玉军.基于CPLD的风光互补发电阀控蓄电池监测系统[J].电子技术应用,2012,38(9):93-95.

XIAO Min-jin,HE Yi-ming,BAO Yu-jun.Design of ValVe Regulated Battery Monitor System in Wind and Solar PhotoVoltaic Generation Based on CPLD[J]. Application of Electronic Technique,2012,38(9):93-95.

[8] 段广云.基于CPLD的数据采集系统[J].仪表技术与传感器,2008,47(6):73-75.

DUAN Guang-yun. Data Acquisition System Based on CPLD [J]. Instrument Technique and Sensor, 2008,47 (6) :73-75.

[9] 宋佳莹,叶树亮.基于CPLD的多参数室内环境实时监测仪[J].传感器与微系统,2011,30(12):133-135.

SONG Jia-ying,YE Shu-liang.Multi-parameter Indoor Environment Real-time Monitor Based on CPLD[J]. Transducer and Microsystem Technologies, 2011,30(12):133-135.

[10] 张春燕,马其华.基于FPGA的中型足球机器人运动控制系统设计[J].实验室研究与探索,2012,31(12):86-88.

ZHANG Chun-yan,MA Qi-hua.Design of a On- board FPGA Control System for RoboCup Based on FPGA[J]. Research and Exploration in Laboratory, 2012,31(12):86-88.

[11] 魏占永.基于CPLD芯片EPM7128设计的数据合并转换器[J].电子技术应用,2002,27(11):56-58.

WEI Zhan-yong. Chip Design EPM7128 Data Combined Converter Based on CPLD [J]. Application of Electronic Technique, 2002,27(11) :56-58.

[12] 刘 谆,崔建明.基于FPGA的煤矿突水监测数据采集系统的设计[J].工矿自动化,2011,34(2):84-87.

LIU Zhun, CUI Jian-ming. Coal Mine Water Inrush Monitoring Data Acquisition System Based on FPGA[J]. Industry and Mine Automation, 2011,34 (2) :84-87.

[13] 辛君君,黄松岭,刘 立,等.基于FPGA的超多通道高速数据采集系统设计[J].电测与仪表,2008,45(10):33-36.

XIN Jun-jun, HUANG Song-ling, LIU Li-li,etal. Design of Super Multi-channel and High-speed Data Acquisition System Based on FPGA[J]. Electrical Measurement &Instrumentation,2008,45(10):33-36.

[14] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社.2008.

[15] 王 艳,韩 啸.基于FPGA的数字超声轮轴探伤仪硬件设计与实现[J].自动化与仪器仪表,2011,12(2):65-67.

WANG Yan, HAN Xiao. Digital Ultrasonic Flaw Detector Axle Hardware Design and Implementation Based on FPGA [J]. Automation & Instrumentation, 2011,12(2) :65-67.

[16] 孙宏国.CPLD在旋转电极电解槽控制系统中的应用[J].实验室研究与探索,2005,24(5):43-45.

SUN Hong-guo.Application of CPLD in the Control System of Rotating Pole of Electro Bath [J]. Research and Exploration in Laboratory,2005,24(5):43-45.