基于模拟IC测试的任意波形发生器设计与实现

2014-01-16陈芳

陈芳

(电子科技大学 微电子与固体电子学院,四川 成都 610054)

集成电路(Integrated Circuit,IC)在国防、工业、日常生活和高新技术等领域有着广泛应用。但是实际的制造过程所带来的以及材料本身存在的缺陷,会导致不良个体的产生,因此,集成电路测试成为保证集成电路产品性能的关键手段之一。目前国内集成电路的测试技术还相对落后,国内各单位在科研、生产和应用测试等领域对集成电路自动测试仪(Automatic Test Equipment,ATE)的需求主要依靠进口来解决。这些进口的测试系统设备昂贵,操作复杂,使芯片测试企业增加了巨大的成本,因此研究具有自主知识产权的高性能集成电路测试系统对促进我国集成电路产业的发展具有十分重要的现实意义[1]。

为了真实地反映待测模拟IC的功能和参数特性,需要保证为待测模拟IC所提供的测试激励的准确性,因此面向模拟IC测试机设计并实现了高精度任意波形发生器用来为待测芯片提供测试激励。本文所阐述的任意波形发生器可以产生不同幅度、不同频率以及不同偏置的各类规则及不规则信号。

1 AWG硬件结构设计

测试效率是模拟IC自动测试仪主要的性能之一,为了满足客户对测试平台高速、高集成度和多通道并行测试能力的要求,本次设计的任意信号发生器为四通道单端输出模式/两通道差分输出模式。图1是一个通道的实现原理框图。

AWG完成一次波形输出首先是用户通过PCI总线由上位机发出指令给测试仪系统,AWG板上的控制器FPGA识别指令,然后FPGA从波形数据存储器中读取相应的波形数据并将数据传递给波形产生DAC,DAC产生的两个差分模拟信号经由滤波模块后再通过差分转单端电路转换为单端信号,单端信号再通过幅度的精调和粗调模块后送入幅度偏移模块,之后便将此信号反馈回信号调理电路,信号调理电路将信号进行适当的衰减或放大使其满足ADC的输入范围要求,ADC对处理过的反馈信号采样并将采样数据送给FPGA,FPGA依据采样数据对反馈信号进行软件检测峰峰值,如果峰峰值与用户设定值相等或者满足误差要求就进行输出阻抗选择并将信号输出到ARB_OUT端,如果不满足误差要求就调节精调系数后再将信号反馈回FPGA重新检测峰峰值直到输出满足用户设定要求。本次设计采用了闭环控制的方法,可以保证AWG输出波形的高精度。

图1 AWG单个通道系统框图Fig.1 Structure diagram of the AWG single channel

2 AWG硬件设计与实现

AWG硬件部分主要包括FPGA、波形存储、波形产生DAC、滤波电路、差分转单端电路、幅度精调电路、幅度粗调电路、幅度偏移电路、输出阻抗选择电路、同步输出电路、继电器驱动电路和信号调理电路;其中,信号调理电路又包括偏置、衰减放大、过压保护、ADC几个电路模块。本论文中对几个关键设计模块进行讨论。

2.1 波形产生模块的设计与实现

波形产生DAC选用的是ADI公司的AD9777,它有两个输入输出通道,两个通道可以完全独立地工作,每个通道都是差分电流输出。AD9777的主要性能指标如下:16位采样精度,160/400MSPSInput/Output Data Rate,Selectable 2×/4×/8×Interpolating Filter,Programmable Channel Gain and Offset Adjustment,On-Chip 1.2 V Reference。 AD9777 的功能框图如图2所示。AD9777的输出电流计算公式如下:

图2 AD9777功能框图Fig.2 Functional structure diagram of AD9777

其中,COARSE为增益粗调,FINE为增益精调,OFFSET为偏置调节。AD9777有两种工作模式:双端模式和单端模式。在2R Mode下IDAC和QDAC的参考电流IREF是分别通过FSADJ1和FSADJ2管脚上的电阻RSET和AD9777的参考电压来进行设置的;在1R模式下IDAC和QDAC的参考电流IREF是2R Mode下的一半。

AD9777的工作模式以及COARSE、FINE和OFFSET的值可以通过串口端向内部控制寄存器写入数据来实现,AD9777可以采用内部参考电压1.2 V也能采用外部参考电0.1~1.25 V。

本次设计AD9777采用内部1.2 V参考电压,双端工作模式,如果设置 COARSE=15、FINE=0、OFFSET=0、RSET=2 kΩ,根据上述公式可以计算出AD9777的满幅输出电流为20 mA,IOUTA和IOUTB的范围为0~20 mA。AD9777的输出端负载为50Ω,所以波形产生模块最终的输出为两个范围为0~1 V的差分信号。

2.2 幅度调节模块的设计与实现

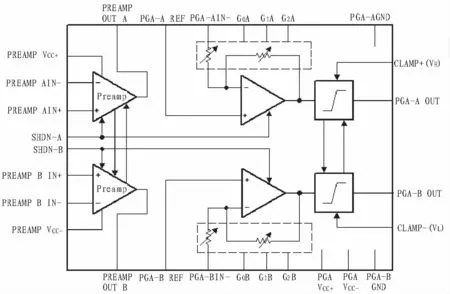

设计要求AWG输出信号峰峰值范围为20 mV~20 V,而差分转单端后的信号幅度为±1 V,因此要对信号进行适当的放大或衰减来满足输出要求。本次设计采用一款可编程增益放大器(Programmable-Gain Amplifiers,PGA)THS7002,THS7002功能框图如图3所示。

图3 THS7002功能框图Fig.3 Functional structure diagram of THS7002

THS7002为双通道PGA,每个通道由低噪声输入前置放大器和可变增益放大器组成。前置运放可以配置增益为-1或2,输入阻抗为1 MΩ,开环输出阻抗为13Ω,起到隔离和阻抗匹配的作用。可变增益运放的由低失调运放和增益电阻组成,可变增益范围-22~20 dB,步进精度为6 dB,通过FPGA控制3位数字位G2G1G0来调节增益。在设计中采用两个通道级联的方式,两个前置运放都设置增益为-1,实现了-44~40 dB的可变增益范围,差分输入范围为±4 V,-3 dB带宽为70 MHz,满足设计要求。使用Tektronix TDS2024C型号的示波器得到的1 MHz信号的测试数据如表1所示。由测试结果可以看出实际值与理论值由些出入,这其中也存在示波器精度造成的误差,所以整体测试结果可以满足设计要求。

2.3 峰峰值检测的设计与实现

设计采用的是软件检测峰值的方法,ADC对反馈信号进行采样,采样结果送入FPGA进行算法处理以此得到信号峰峰值。ADC选用的是AD9245,AD9245配置为单端模式,此时AD9245输入信号范围为0~2 V,因此信号调理电路中要先对VOUT_FB进行适当的衰减放大和偏移使其能够满足AD9245的输入要求。由Verilog实现的峰峰值检测代码如下:

if(DATAIN[13]==1'b0)

begin

DATA_REG2<=DATA_REG2;

表1 THS7002测试结果Tab.1 Test result of THS7002

if(DATAIN>=DATA_REG1) DATA_REG1<=DATAIN;

else if (DATAIN <DATA_REG1) DATA_REG1 <=

DATA_REG1;

end

else if(DATAIN[13]==1'b1)

begin

DATA_REG1<=DATA_REG1;

if(DATAIN<=DATA_REG2) DATA_REG2<=DATAIN;

else if (DATAIN >DATA_REG2) DATA_REG2 <=DATA_REG2;

end

assign P_PEAK=DATA_REG1;

assign N_PEAK=DATA_REG2;

其中DATAIN[13:0]为AD9245的14位补码输出,P_PEAK为检测的正峰值,N_PEAK为检测的负峰值。AD9245输入为0.5~1.5的正弦波时,由ChipScope抓取DATAIN[13:0],采样65 536个点绘制成的波形如图4所示。可以看出采样结果精确,基本没有噪声干扰。

3 测试结果

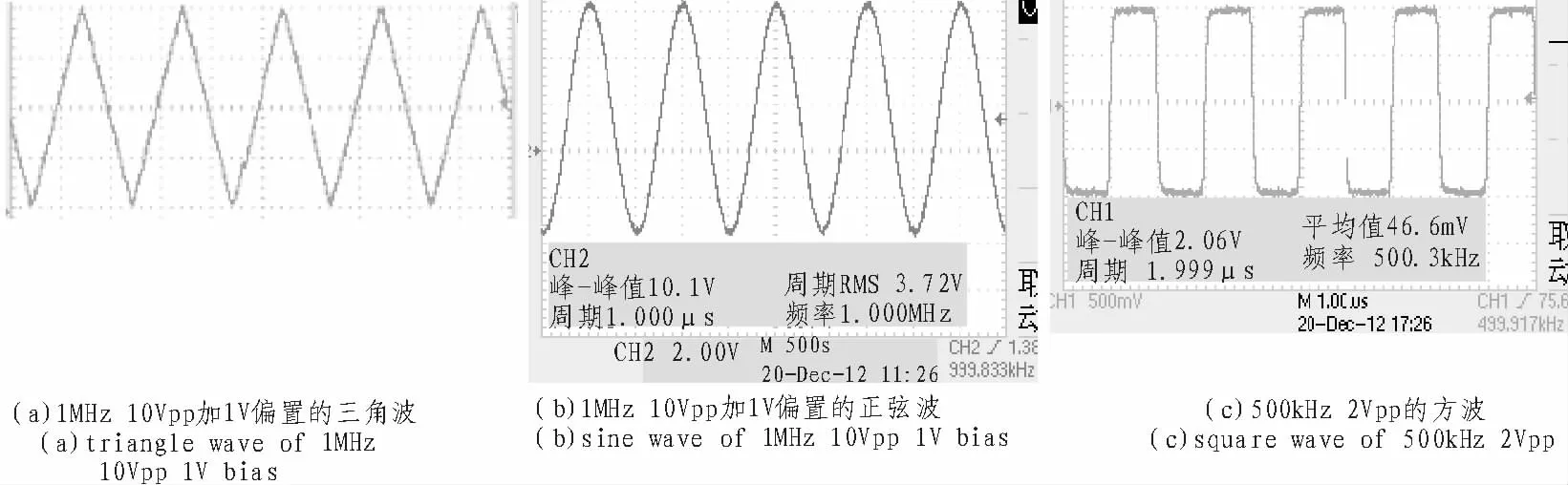

利用Tektronix TDS2024C型号的示波器测量得到AWG系统产生的正弦波、方波、三角波3种基本波形如图5所示。

图4 AD9245的补码输出Fig.4 AD9245 complement output

测试结果波形比较理想,可以满足设计要求。

4 结束语

图5 AWG系统的输出信号Fig.5 Output signal of AWGsystem

AWG是模拟IC自动测试仪项目重要组成部分,通过测试结果来看,输出波形可以达到输出频率1 Hz~1 MHz、峰峰值范围20 mV~20 V,幅度偏移范围为±2.5 V,精度可达到±0.1dB。能够满足项目的要求,可以用于相关模拟IC测试设备以及其他相关仪器。闭环控制的概念可以保证输出波形的准确性,利用FPGA作为控制器具有控制简单、可靠性高等优点。

[1]俞建峰,陈翔,杨雪英.我国集成电路测试技术现状及发展策略[J].中国测试,2009,5(35):1-3 YU Jian-feng,CHEN Xiang,YANG Xue-ying.Current status on Chinese integrated circuit testing technology and its development strategies[J].China Measurement&Test,2009,5(35):1-3.

[2]王文梁.100MSa/S任意波形发生器硬件设计[D].成都:电子科技大学,2007:33-39.

[3]乐春峡,王艳平.基于FPGA的任意波形发生器的设计[J].现代电子技术,2008(1):52.LE Chun-xia,WANG Yan-ping.Design of FPGA-based arbitrary waveformgenerator[J].Modern Electronics Technique,2008(1):52.

[4]易先军,叶春生.基于FPGA的高速数字峰值保持器设计[J].现代机械,2005(4):9-10.YI Xian-jun,YE Chun-sheng.Design of high-speed digital peak holding circuit based on FPGA[J].Modern Machinery,2005(4):9-10.

[5]Paul Horowitz,Winfield Hill.吴利民,余国文,欧阳华等.电子学[M].北京:电子工业出版社,2005.

[6]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[7]史强强,孟新新,赵乾坤,等.数字SPWM调制信号截尾误差的补偿方法研究[J].陕西电力,2013(12):61-65.SHI Qiang-qiang,MENG Xin-xin,ZHAOQian-kun,et al.Compensation Method for Modulation Signal Truncation Error of Digital SPWM[J].Shaanxi Electric Power,2013(12):61-65.

[8]杨建安,李健,徐志强,等.基于互补滤波器的大型定转速风力发电机组有效风速信号测量方法[J].陕西电力,2011(11):22-25,72.YANG Jian-an,LI Jian,XU Zhi-qiang,et al.Probe into the measurement method of effective wind speed signal for fixedspeed wind turbinesbased on complementary filters[J].Shaanxi Electric Power,2011(11):22-25,72.