OpenRISC处理器片上监控系统设计

2014-01-16王宇刘宏伟

王宇,刘宏伟

(哈尔滨工业大学计算机科学与技术学院,哈尔滨 150001)

OpenRISC处理器片上监控系统设计

王宇,刘宏伟*

(哈尔滨工业大学计算机科学与技术学院,哈尔滨 150001)

文章介绍OpenRISC软核处理器基本架构,阐述使用开源软核处理器实现工作在FPGA上的片上处理器监控系统的具体方案,设计片上双核系统,实现软核关键技术监控的软硬件系统,通过仿真及试验验证该技术效果。

OpenRISC;FPGA;片上系统

计算机处理器性能指标研究大部分局限于理论分析和模型仿真,基于硬件处理器监控系统成本极高。为解决这一问题,本文提出一种在FPGA芯片上实现的处理器监控系统。相对于常规处理器,FPGA具有可重构优势,适合多任务切换场合,节约系统资源,实现功能复用,提高整个系统性能。

研究选用完全开源32位软核处理器OpenRISC且作为被监控处理器和监控处理器。该处理器由开源社区OpenCores提供并维护,适合于网络及嵌入式应用[1]。该处理器拥有外围接口等资源,用户可根据需要自由选择。由于其源代码完全开放,使用者可根据应用场合的不同修改处理器的硬件描述语言源代码,针对系统功能对处理器作出相应优化。

1 软核处理器分类

1.1 非开源软核处理器

Altera公司开发的NoisⅡ处理器是一种通用RISC处理器核,提供全32位指令集,集成Altera嵌入式逻辑分析仪,可实时分析FPGA设计中的指令及数据信号[2]。

MicroBlaze嵌入式处理器是一种针对Xilinx FP⁃GA优化的32位软核处理器。同时,用户可根据需要对MicroBlaze软核处理器进行功能配置[3]。

1.2 开源软核处理器

LEON系列中LEON3处理器是一款使用VHDL语言编写的32位SPARC V8结构的处理器。LEON3处理器的全部源代码公开,提供片上指令和数据跟踪调试功能,支持多处理器工作[4]。

OpenRISC是一款完全开放源代码的32位RISC处理器,使用Verilog HDL实现。该体系结构最为显著的特性是指令扩展,可配置数量的通用寄存器,可配置的高速缓存以及直接映射快表,动态能量管理的支持,以及为用户指令提供空间[5]。

2 OpenRISC关键技术仿真跟踪

ModelSim是一种常用的硬件描述语言仿真软件,可以方便跟踪处理器内部的各个信号,结果也可以用波形方式很直观地显示。其结果可以和实际运行取得的信号相比较,作为验证。

2.1 ModelSim仿真跟踪流水线

使用如下的一段代码:

其中,第3条和第4条指令会发生数据相关。为解决这一问题,OR1200采用前向通路技术[10]。

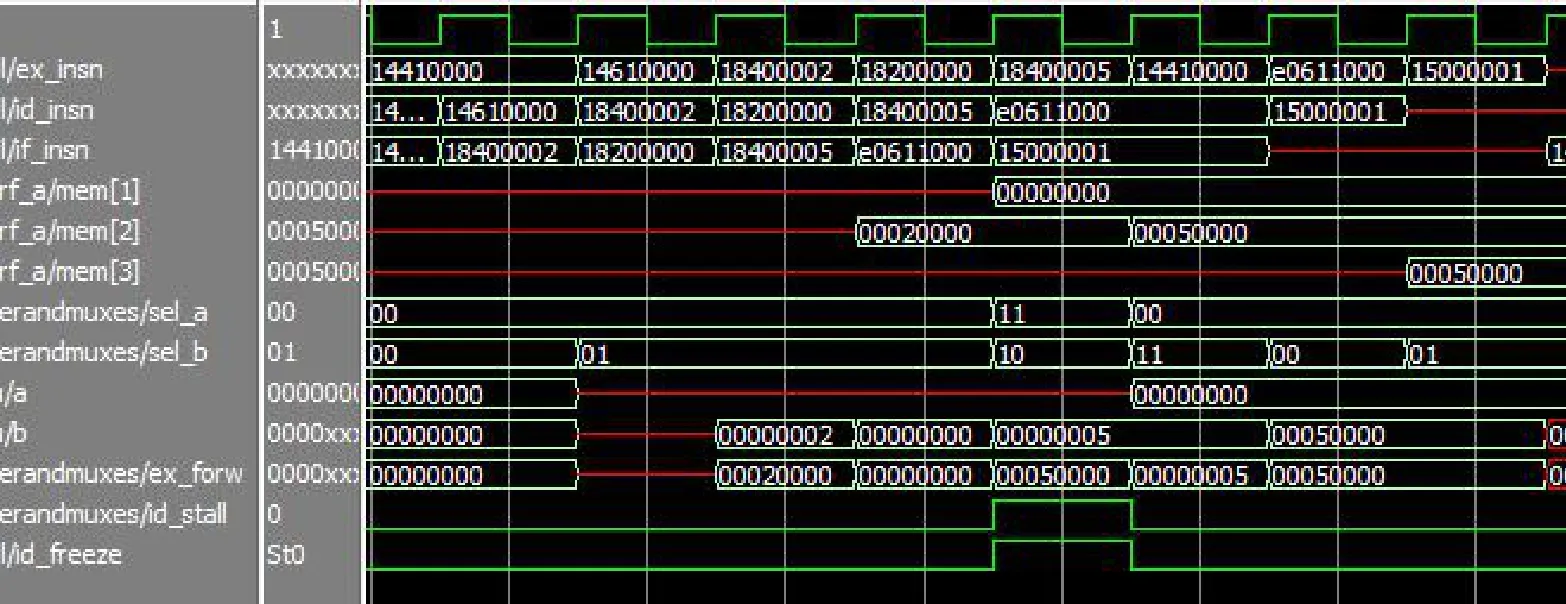

通过修改OR1200源代码方式禁止前向通路。具体做法是关闭从ex_forw到ALU的数据通路,如图1所示。

由图1可知,在禁止前向通路的情况下,在第4条指令执行周期,ALU的数据输入端b的数据为0x00020000,即寄存器r2在第3条指令执行之前的值,最终参与运算也是这个值,最终,r3寄存器的值是0x0002000,是错误结果。

另一种解决方法是在流水线中加入空周期以实现流水线的延迟执行,如图2所示。

图1 ModelSim仿真跟踪禁止前向通路技术Fig.1 Tracking the situation when forward path is disabled through simulation by ModelSim

图2 ModelSim仿真跟踪加入空周期Fig.2 Tracking the empty cycle through simulation by ModelSim

由图2可知,当出现数据相关时,使流水线的特定功能段空转,直到能够避免该数据相关。具体到上述程序涉及的先写后读数据相关,可采用暂停流水线中的译码功能段方法解决。本文通过修改OR1200源代码方式实现加入空周期。首先,在OR1200检测到数据相关发生后,产生一个周期脉冲信号,作为暂停信号,发送到OR1200处理器的CTRL模块,连接到id_freeze接口。该信号使译码流水段延长到两个周期。在流水线空转1个周期内,第3条指令运行结果已存入寄存器r2。因此,在空周期结束之后,第4条指令执行时,ALU的数据输入端输入的数据正确,最终结果是寄存器r3的值为0x00050000,数据正确。可见,使用加入空周期方法能解决数据相关问题,但是这种方法延长程序执行时间,降低流水线工作效率。

2.2 ModelSim仿真跟踪Cache的命中与非命中

OR1200的Cache分为指令Cache和数据Cache,其中,对于指令Cache来说,指令在Cache中被访问到称作命中,反之为非命中,当一条指令,第一次在程序中被使用,则会发生非命中。该条指令所在的块被调入Cache,块的大小为4个字节,此条指令之后的3条指令也同时被送入Cache,三条指令运行时会发生命中。通过ModelSim可观察这一过程中Cache相关单元变化,比较Cache命中与非命中情况下,每条指令执行的不同时钟周期。

综上,通过ModelSim对OR1200软核处理器进行仿真跟踪可观察到各种需要信号而不必在硬件电路上显示,提高分析设计效率,为后续设计工作奠定基础。软件仿真存在固有弊端,无法完全替代真实监控系统。因此,通过ModelSim仿真对软核处理器流水线跟踪分析只能作为硬件监控系统补充。

3 基于Wishbone总线的OpenRISC最小系统实现

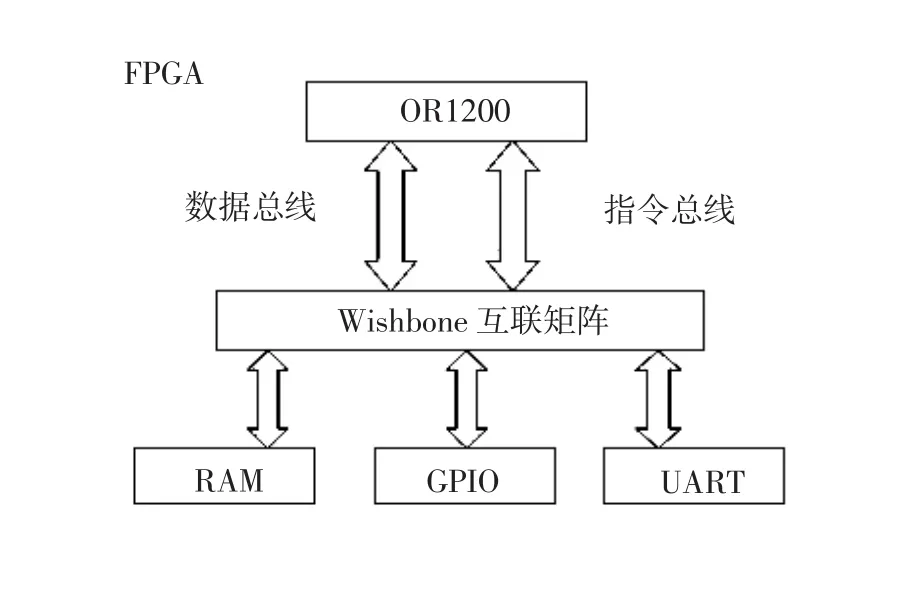

OpenRISC最小系统以OpenRISC系列处理器中的OR1200为核心,通过wb_conmax模块挂接存储器(RAM)、通用输入输出单元(GPIO)、串行接口(UART)。OpenRISC处理器采用Wishbone总线技术,Wishbone是一种免费开放的总线规范。wb_conmax是一种Wishbone互联矩阵。

OR1200的指令总线和数据总线分别连接wb_conmax的0号和1号主接口,存储器(RAM)、通用输入输出单元(GPIO)和串行接口(UART)在分别连接了0号、1号和2号从接口,如图3所示。

图3 基于Wishbone总线的OpenRISC最小系统Fig.3 OpenRISC minimum system based on Wishbone bus

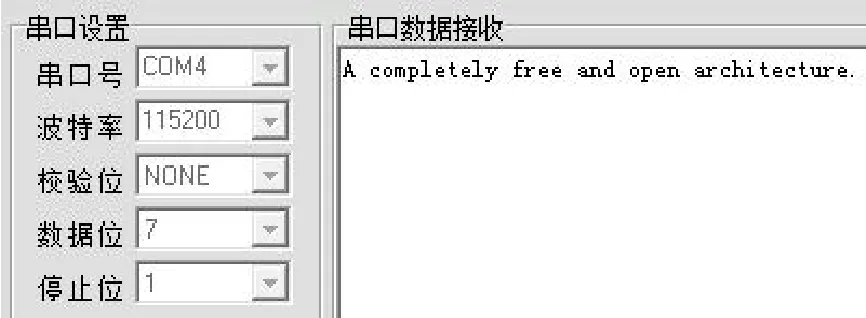

对该最小系统进行编译,下载到FPGA开发板上,运行测试程序,结果如图4所示。通过在PC机上运行的串口助手接收到由OR1200经由Wish⁃bone总线和串行接口发来的数据。

图4 OR1200处理器通过串行接口发送的数据Fig.4 Data sent through the serial interface by OR1200

4 开源软核处理器FPGA片上监控系统的设计

4.1 片上双核监控系统的设计

4.1.1 片上双核系统的实现

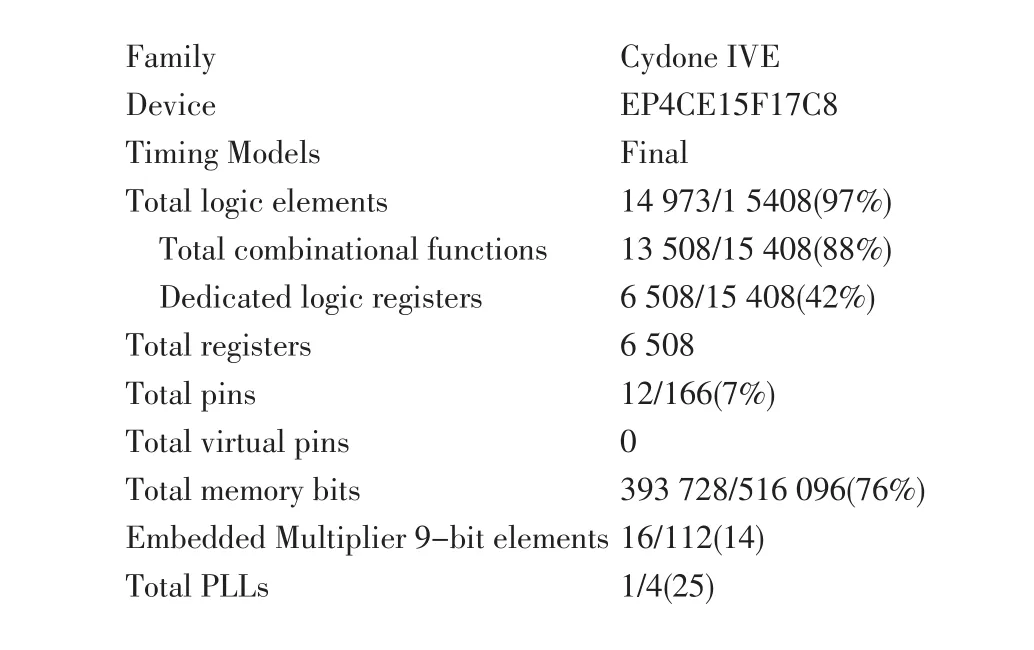

在同一片FPGA芯片上实现两个OR1200系统,这两个系统除共享时钟与复位信号之外,其他资源完全独立,这两个系统拥有独立的RAM、GPIO和wb_conmax,其程序可在同一时钟下独立运行。这里选用的FPGA是Altera公司的EP4CE15 F17C8,通过Quartus软件进行逻辑综合,得到该系统占用片上资源情况,如图5所示。

通过在开发板上进行验证试验,编写通过GPIO输出控制LED灯闪烁的程序,观察试验结果,两组LED灯可同步正常工作,证明两个处理器可同步正确工作。

图5 片上双核系统占用的资源Fig.5 Resources occupied by the dual core system on a chip

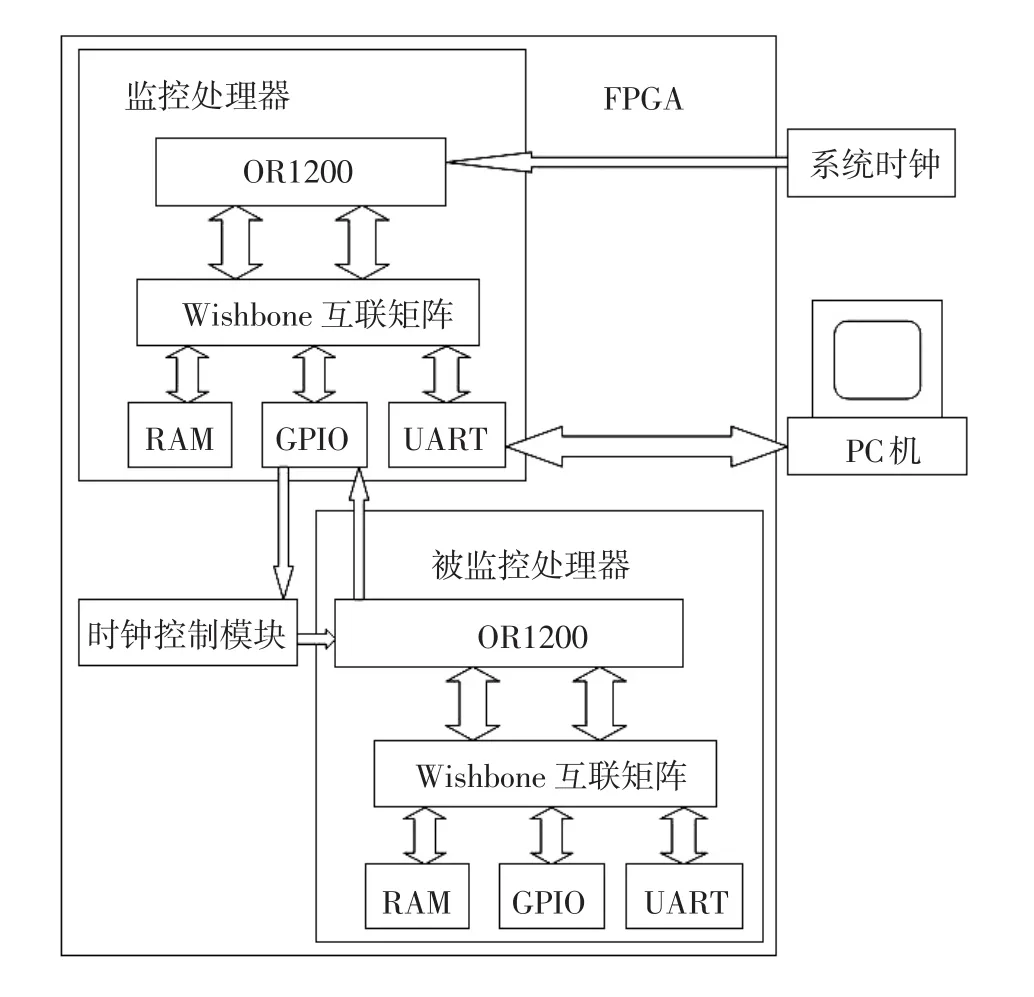

4.1.2 双核监控系统设计

为通过硬件平台实时监控开源软核处理器的关键技术指标,设计基于FPGA芯片的片上双核监控系统。该系统在上述片上双核系统的基础上实现。其中,两个处理器核分别作为监控处理器和被监控处理器。重点监控的信号有流水线功能段相关信号、Cache命中率统计相关信号。

在系统结构设计上,被监控处理器采用常规系统配置,正常工作;监控处理器则采用最小系统以节约系统资源并且通过控制系统时钟信号控制被监控处理器的工作。信号采集通过监控处理器的GPIO单元实现,该单元与被监控处理器待测试信号直接相连,通过运行在监控处理器上的程序实现数据采集、暂存、处理等功能,最后通过串行接口发送到系统计算机。在系统计算机端,通过串口助手接收到数据并显示。监控系统结构如图6所示。

4.2 独立监控模块设计

为实现对软核处理器的跟踪监控,使用Verilog硬件描述语言在FPGA上开发独立监控模块。该模块功能包括:接收上位机从串行接口传送的单步运行指令,每接收一个单步运行指令,监控模块控制微处理器工作一个时钟周期,同时,采集上位机需要监控的各个流水线功能段寄存器状态,通过串行接口再发送给上位机,每一个时钟周期都要进行一次状态采集。

如图7所示,该模块内部又分为串行通信单元、单节拍发生器单元、四位环形计数器单元、系统时钟分频器单元,寄存器信息采集单元、寄存器数据缓冲单元、寄存器数据转换单元等单元。

图6 片上监控系统结构Fig.6 Structure of monitoring system on a chip

图7 监控模块结构Fig.7 Structure of the monitor unit

在监控模块工作时,串行通信单元首先接收到由上位机串行口发送的一个字节数据,在接收过程中串行通信单元的输出信号rxint为高电平,接收结束转为低电平,该信号被传送给单节拍发生器单元,单节拍发生器单元据此产生一个固定宽度的单脉冲,送给CPU的时钟输入引脚,同时rx⁃int信号触发一个四位环形计数器,该计数器的输出连接到寄存器信息采集单元的寄存器选择端口,计数器不同的输出代表不同的寄存器,寄存器信息采集单元据此依次采集各个寄存器的值,采集到的32位寄存器数据经过寄存器数据缓冲单元、寄存器数据转换单元被分成4个字节的数据,从串行通信单元依次发送回上位机。该模块使用Verilog HDL硬件描述语言编写,在FPGA上实现。

4.2.1 串行通信单元

在本设计中,上位机发送端和FPGA上的监控模块的波特率均采用9 600 bps。重点在于波特率确定、数据格式约定及确保时序上正确性。标准的串行通信协议中,每次最多只能传送8位二进制数据,而OR1200中需要采集信息的寄存器均为32位,因此,无法将采集到的寄存器数据直接发送给串行通信模块,需进行数据转换。

4.2.2 单节拍发生器单元

要实现用户可通过上位机软件控制OR1200软核处理器单步运行,需提供给CPU一个单脉冲信号,在串行通信单元中,每接收到一个数据,就产生一个正脉冲,但是这个正脉冲宽度不确定无法满足为处理器提供时钟信号需要。因此,设计单节拍发生器单元。该单元可实现忽略输入信号周期与占空比,可输出一个稳定的固定宽度的单脉冲信号,用以控制处理器单拍工作。

4.2.3 四位环形计数信息的获取

FPGA可进行多个寄存器数据同时采集;但串行通信单元只有一个,所以需要对寄存器数据信息进行排序,以实现依次发送。本文采用四位环形计数器,最多可进行16个数据的选择,满足开发验证平台需求。四位环形计数器不同输出与不同寄存器相对应,被选中寄存器的值从寄存器信息采集单元输出到下一单元。

四位环形计数器工作需要自己时钟信号,单脉冲无法满足要求,每个单脉冲到来后,需采集若干个寄存器信息,需一个连续时钟脉冲信号(所采用时钟脉冲信号为50 MHz),与串行发送的速率相比速度过高,需要分频器降低频率操作,给计数器提供合适时钟信号。

4.2.4 寄存器信息采集单元

寄存器信息采集单元的数据输入端直接与CPU内部各等待采集信号相连,而选择端被四位环形计数器所控制,被选中的数据输出到寄存器数据缓冲单元。

4.2.5 寄存器数据的转换

由于各个寄存器均为32位,而串行通信每次最多只能发送8位数据,因此要进行数据的暂存与转换,需要将32位的数据转换为4个8位数据按照合适的时间间隔依次发送给串行通信单元。每个数据发送完毕后,串行通信模块会反馈回一个信号,数据转换单元据此信号,发送下一字节的数据给串行通信模块。

通过该监控模块进行流水线的单步跟踪控制实验。通过上位机的串行接口发送指令,每次发出一个脉冲到CPU的时钟输入接口,控制微处理器单拍运行。上位机软件界面上显示的取指寄存器数据if、译码寄存器id、执行寄存器ex分别显示正位于本功能段的指令的值,通过连续发送单步运行指令,可观察到流水线的流动。

5 结论

本文介绍开源软核处理器的体系结构,论述该处理器关键技术,阐述微处理器流水线功能段跟踪。提出可进行流水线跟踪监控方案,对监控模块的方案功能、结构和实现方式进行描述。通过开源软核处理器实现的监控系统结构简单、成本较低,可于单片FPGA上实现,节约系统资源;开源软核处理器的可裁减可修改的特性则使该系统易于实现特定功能,可根据需要随时重构,适合于计算机体系结构设计与研究。

[1]曹慧渊,郏辉,胡浩.基于Openrisc的TPCM架构设计[J].信息工程大学学报,2011,12(2):246-250.

[2]Hasamnis M A,Limaye S S.Custom hardware interface using NIOS II processor through GPIO[C].2012 7th IEEE Conference on Industrial Electronics and Applications(ICIEA),Singapore: IEEE,2012:1381-1385.

[3]Muralikrishna B,Gnana D K.Input/output peripheral devices con⁃trol through serial communication using microblaze processor[C]. 2012 International Conference on Devices,Circuits and Systems (ICDCS),Coimbatore:IEEE,2012:532-536.

[4]Abbasitabar H,Zarandi H R,Salamat R.Susceptibility analysis of LEON3 embedded processor against multiple event transients and upsets[C].2012 IEEE 15th International Conference on Computa⁃tional Science andEngineering,Nicosia:IEEE,2012:548-553.

[5]Wang B S,Lv S W,Yang D K,et al.A new solution to GNSS re⁃ceiver baseband signal processing SOC platform based on open⁃RISC processor[C].2011 7th International Conference on Wire⁃less Communications,Networking and Mobile Computing(WiC⁃OM).Wuhan:IEEE,2011:1-4.

Design of OpenRISC monitoring system on a chip

WANG Yu,LIU Hongwei (School of Computer Science and Technology,Harbin Institute of Technology,Harbin 150001,China)

The paper introduces the basic architecture of the OpenRISC soft core processor, expounds the specific solutions of using open source soft core processor to realize the on-chip processor monitoring system working on FPGA,designed the dual core system on a chip,realized the software and hardware of the key technology monitoring system,verified the effect of the technology through simulation and experiment.

OpenRISC;FPGA;system on a chip

TP391.41

A

1005-9369(2014)09-0111-05

2014-06-06

国家863重大项目(2013AA01A215)

王宇(1982-),男,工程师,硕士研究生,研究方向为计算机体系结构。E-mail:snowcity@hit.edu.cn

*通讯作者:刘宏伟,教授,博士生导师,研究方向为容错计算、移动计算等。E-mail:liuhw@hit.edu.cn

时间2014-9-18 10:44:12[URL]http://www.cnki.net/kcms/detail/23.1391.S.20140918.1044.007.html

王宇,刘宏伟.OpenRISC处理器片上监控系统设计[J].东北农业大学学报,2014,45(9):111-115.

Wang Yu,Liu Hongwei.Design of OpenRISC monitoring system on a chip[J].Journal of Northeast Agricultural University, 2014,45(9):111-115.(in Chinese with English abstract)