基于CPS1848的SRIO总线交换模块设计

2014-01-01马友科

马友科

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

随着多种处理器协同处理数字信号的要求不断增加,处理器间数据交换的带宽不断扩大,数据交换能力的强弱直接影响着数字信号处理的能力。近年来,新兴的高性能互连交换技术相继涌现,其中专为嵌入式系统提出的串行RapidIO总线(SRIO)被认为是最佳的选择之一[1],为了适应信号并行处理技术发展的趋势,有必要设计一种SRIO总线交换模块。

在相关研究方面,文献[2]采用FPGA芯片来实现SRIO交换,可靠性和兼容性没有经过充分的验证和测试,可能会存在一定问题,同时成本也比较大;文献[3]和文献[4]分别采用 TSI568和 TSI578作为接口芯片来实现SRIO交换,但是这2款芯片只支持到RapidIO协议1.3版本,存在传输带宽小,端口个数少等问题,越来越不能够满足宽带传输与交换的需求;文献[5]采用CPS1848设计了一种基于光纤的SRIO交换模块,交换模块的单对差分线的最高数据传输速率为3.125 Gbit/s,与 CPS1848可以支持的最高速率6.25 Gbit/s相比,还有一定的提升空间。

本文基于CPS1848芯片设计了一种SRIO总线交换模块,该交换模块单对差分线工作在5 Gbit/s,传输带宽最高可达192 Gbit/s,为需要进行数据高速传输和交换的工程应用奠定了坚实的基础。

1 SRIO交换模块总体结构

SRIO交换模块的解决方案框图如图1所示,它由时钟模块、交换芯片、电源模块、配置模块和节点设备5部分组成。电源模块为所有其他芯片提供需要的各种电压,交换芯片的初始化配置主要由C8051F单片机或EEPROM来完成,交换芯片连接到系统中的各种节点设备或用于管理系统各节点设备的主设备,例如:DSP、FPGA和PowerPC等,交换芯片根据系统的规模可以单片使用或几片级联使用,时钟模块为一片或多片交换芯片提供高精度的稳定时钟。

图1 SRIO总线交换模块总体结构

2 SRIO交换模块的设计

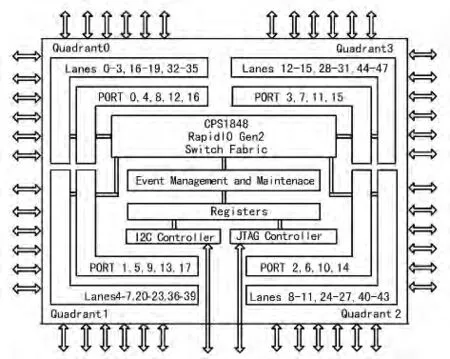

SRIO交换模块的核心器件SRIO交换芯片选用IDT公司的CPS1848,其原理如2所示。

图2 CPS1848原理

CPS1848是IDT公司最新推出的支持SRIO2.1标准的交换芯片[6],有48个双向的数据差分对(lane),可以配置成1x、2x和4x三种端口模式,最多可以配置成18个1x或12个4x端口,每个lane的速 率 可 以 设 置 为 1.25 Gbit/s、2.5 Gbit/s、3.125 Gbit/s、5 Gbit/s或 6.25 Gbit/s。CPS1848 还有一个标准I2C接口,I2C接口可以用来完成对CPS1848的初始化配置,也可以通过读取CPS1848内部寄存器来监视它的工作状态。CPS1848的应用面向大型处理器集群或背板,支持多种拓扑结构,可以采用灵活的方式进行配置,可选的配置方案也非常丰富。

2.1 CPS1848外围电路设计

2.1.1 I2C接口电路设计

因为I2C接口中的SCL、SDA是漏极开路的,所以必须各加10 K上拉电阻,否则I2C总线是不能正常工作的。CPS1848在I2C总线上分配的地址,是由引脚ID0-ID9的高低电平来决定的。ADS引脚上的高低电平决定是采用7 bit还是10 bit的地址。引脚MM_n决定I2C总线是主模式还是从模式。

2.1.2 复位设计

CPS1848的复位有上电复位、硬复位、软复位和寄存器复位4种方式。上电复位对参考时钟稳定度和电源的上电顺序是有特定要求的。硬复位引脚RST_n连接到FPGA,由FPGA来完成CPS1848的硬复位,硬复位完成后,CPS1848和所连接的节点设备间立刻开始链接。CPS1848的芯片到目前有A、B和C三个版本,其中A版本的硬件复位不一定能成功复位芯片,需要在初始化CPS1848的程序开始时加上软复位。寄存器复位可以复位指定的PORT和PLL,与上述3种复位不同的是,它不能复位已配置的寄存器。

2.1.3 端口设计

使用多个不同宽度端口的时候要通过设置QCFG来进行规划,lane组合成不同宽度的端口是有约束的,例如配置成2x模式的端口 PORT3由lane12和lane13组成,当PORT3连接到1x的节点设备时,PORT3会降级使用,此时只有lane12可以当成 1x使用,而 lane13不能当成 1x的端口。CPS1848只支持AC耦合,lane上的耦合电容要尽量靠近接收端放置。为了得到更大的数据传输带宽,SRIO交换模块中CPS1848配置引脚QCFG[0∶7]都设置为低电平,即48条lane配置成12个4x的端口。受所连接的节点设备的限制,速度引脚SPD[2∶0]配置成010,即每条lane的数据传输速率为5 Gbit/s。

JTAG电路等比较简单,不再赘述。

2.2 CPS1848配置模块的设计

CPS1848有多种配置方式,非常灵活。EEPROM配置模式主要用于在芯片上电复位后,对CPS1848进行初始化配置。通过JTAG口可以直接对片内寄存器进行配置,这种方式一般在调试时使用。通过I2C接口和SRIO的Maintenance数据包不仅能完成CPS1848配置,而且还能监控链路通信状况,提高系统的可靠性。多片CPS1848级联使用,需要进行配置时,可以采用单片机作为I2C总线的主设备,来同时完成几片作为从设备的CPS1848的配置。在交换模块运行的过程中,如果需要改变数据传输的方向,可以通过Maintenance数据包设置CPS1848内部的相关寄存器,重新配置路由表,来动态地更改交换模块节点设备间的拓扑关系[7]。

交换模块的配置方法[8]如下:

①在上电复位时,通过配置引脚的上下拉电阻完成需要的配置;

②复位引脚RST_n由低变高后,立刻开始链接初始化直至完成;

③采用单片机通过I2C接口来完成CPS1848的寄存器初始化;

④通过maintenance数据包来完成CPS1848的路由表动态更改、状态监测等。

3 关键技术

整个交换模块的关键技术主要包括:阻抗稳定、相互间串扰小的高速传输线设计,纹波小、上电顺序符合芯片要求的电源电路设计和抖动低、精度高的时钟电路设计等3个方面的内容。

交换模块外围的Lane都工作在5 GHz,为了保证信号的完整性和电磁兼容性,使用MENTOR公司的Hyperlynx仿真软件[9]对交换模块PCB上的高速信号线进行了仿真分析,使得每对差分线的阻抗保持恒定100 Ω,同一个端口内的各差分线之间的信号传输偏移时间小于11 ns,差分线之间没有大的串扰,从而保证了信号的高质量要求。

CPS1848需要的电源有核电压+1.0 V、PLL模拟电压+1.0 V、IO电压+3.3 V、SerDes电压模拟+1.0 V和模拟+1.2 V。各种电压所耗电流大小必须满足手册中的要求。所有模拟电压需用纹波非常小的线性电源来提供,该SRIO交换模块采用的是TI公司的TPS74401线性电源模块。CPS1848对各电压的上升和下降时间没有要求,但是对各电压的上电顺序有着严格的要求,SerDes的VDDS电压先上电,然后是SerDes的VDDT电压,其余电压顺序没有要求,上电顺序通过控制电源模块使能端来实现。最后利用Allegro PCB PI工具对所有电源进行电源完整性分析,确保电源噪声不会干扰高速信号。

时钟模块原理框图如图3所示。

图3 时钟模块原理

CPS1848的REF_CLK引脚为芯片内部的PLL提供参考时钟,它要求在1~20 MHz范围的相噪要低于 2 ps RMS,频率精确度要好于 100 ppm(156.25 MHz),再考虑到交换模块以及其所连各节点设备的时钟同源可以进一步改善信号完整性,因此选用高精度的VCXO作外部参考,使用ADI公司有两级PLL的时钟芯片AD9523 m提供所需的多路高精度时钟[10]。

4 SRIO交换模块的性能测试及分析

结合实际信号处理过程中的数据传输和交换方式,编写DSP和FPGA测试程序,DSP和 FPGA的SRIO端口都设为4x(4对差分线组成一个端口使用),以SRIO协议中的NWRITE、NREAD方式为例,通过DSP(型号为TMS320C6678)与FPGA(型号为VC6VSX315T)之间的数据传输,对SRIO交换模块的性能进行了实测[11]。

将DSP内存空间0x10800000开始的4 KB数据循环发送131 072次,共512 MB数据至FPGA,然后再回读同样次数至DSP,分别测试写的时间和读的时间。DSP发送数据采用NWRITE方式,读取数据采用NREAD方式,调用TI公司的MCSDK库中的两个函数分别为 SRIO_DIO_NWRITE_BLK()和SRIO_DIO_NREAD_BLK(),使用CCS5软件来统计所耗的时钟周期数,由于DSP主频1 GHz,即每个时钟周期1 ns,据此可以计算出所耗时间。通过CPS1848内部的相关寄存器可以看到,接收并转发的数据包的个数正确,无坏包,无重新发送的情况发生。最终的整个通道的测试结果如表1所示。

表1 DSP与FPGA之间数据传输带宽测试结果

对RapidIO协议进行分析可知,当SRIO数据包中数据有效载荷为256 bytes时,RapidIO的有效数据传输效率约为72%[12]。因此在5 Gbit/s和4x模式下,RapidIO的理论数据传输速率为14.4 Gbit/s。

实测结果与理论值有一定差距。由于进行测试时,DSP的测试程序进行了131 072次的循环,循环程序的执行占用一定的时间开销。另外,DSP内集成的SRIO模块,将最多可达1 Mbyte的数据拆成每包256 bytes的SRIO协议数据包再发送,这种机制也占用一些时间开销。

5 结束语

采用IDT公司最新的CPS1848芯片设计了一种新型的高性能SRIO总线交换模块,作为节点设备(FPGA、DSP等)间的高速数据通道,保证了大数据量的高速传输稳定可靠。该模块的配置方法灵活,性能优良,通过动态改变路由表来改变数据流路径,使得系统的可重构可扩展变得非常容易,具有很强的适应性。随着支持SRIO总线的设备越来越多,SRIO总线交换模块将会有越来越广泛的应用。

[1] 高 毅,刘永强,梁小虎.基于串行RapidIO协议的包交换模块的设计与实现[J].航空计算技术,2010,40(3):123-126.

[2] 翟彦彬,蒋志焱,张保宁.大规模RapidIO协议交换的FPGA 实现[J].现代雷达,2011,33(12):33 -35.

[3] 王学宝,郑波祥,朱 勇.基于TSI568的RapidIO交换模块设计[J].微计算机信息,2009,25(6):104 -105.

[4] 张 静,李汉波.基于TSI578的串行RapidIO交换模块设计[J].电子元器件应用,2010,12(11):30 -32.

[5] 千应庆,王晓锋,劳 力,等.一种基于RapidIO协议的光纤总线硬件架构设计与分析[J].兵工学报,2012,33(12):1 480-1 484.

[6] 姚 钢.全新SerialRapidIOGen2交换器提升嵌入式互联性能[J].EDN 电子设计技术,2010(10):10-11.

[7] 谢丽斌,刘 凯,尚 煜.串行RapidIO交换技术[J].电子科技,2012,25(9):129 -131.

[8] 石海洋.一种RapidIO交换网络配置方法的设计与实现[J].航空计算技术,2012,42(2):132 -134.

[9] 齐青茂,冯 鹤,马友科.基于Hyperlynx的高速数据传输板 SI研究[J].计算机与网络,2012,38(14):47 -49.

[10]张娅娅,张 磊,崔海龙.分相位时钟组的高速数据采样[J].无线电通信技术,2012,38(6):52-55.

[11]饶 坤.基于DSP和FPGA的串行RapidIO系统性能测试与分析[J].信息与电子工程,2012,10(6):680-684.

[12]许烈华.一种基于openVPX的通用信号处理平台设计[J].电讯技术,2012,52(5):796-799.