基于CPCI总线的多卡实现32路采集平台设计

2014-01-01邢占春曹芳菊黄进燕

邢占春,曹芳菊,黄进燕,黄 凯

(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.邢台职业技术学院,河北邢台054000)

0 引言

CPCI是国际工业计算机制造者联合会(PCI Industrial Computer Manufacturer’s Group,PICMG)组织于1994年提出的高性能工作计算机总线标准。CPCI总线在电气方面兼容PCI总线,CPCI架构的设备电气连接性能好、可靠性高、散热好、兼容性强,并且维护使用非常方便,允许有多个外围CPCI插卡需要与CPCI主板进行通信,通过分时复用共享CPCI总线带宽。这些特点允许我们设计更为复杂、灵活的信号采集平台[1,2]。

1 8路采集卡设计与实现

1.1 板卡原理组成

8路采集板卡主要由变压器匹配电路、A/D变换器、FPGA(A/D控制逻辑、数据滤波及处理)、时钟分配模块、9054 桥芯片、FIFO 和电源等组成[3-5]。8路采集处理单元原理框图如图1所示。

图1 8路采集处理单元原理

1.2 ADC选择

设计中选用Analog Devices的AD9252主要基于几方面考虑:

①单通道最高采样率满足信号采集平台采样率的需求。奈奎斯特采样定理指出了在模数转换过程中,当采集频率fs.max大于信号中最高频率fmax的2倍时(fs.max≥2fmax),采样后的数字信号完整保留了原始信号中的信息。一般讲采集频率为信号最高频率的3~4倍。本系统要求中频信号带宽为0~2 MHz,则采样率最高为8 MSPS,而AD9252最高采样率为50 MSPS,可以保证频谱不会发性混叠。

②SFDR和SNR指标。AD9252无杂散动态范围SFDR为84 dBc(to Nyquist);信噪比(SNR)为73 dB(to Nyquist),满足系统要求。

③多通道之间同步问题。单个板卡上实现8路信号采集必然涉及到采集同步问题,如果使用多个芯片实现,还需要考虑芯片间的时钟同步问题,增加了PCB设计的难度,因此选择单芯片设计是最佳选择。AD9252就是一款8通道的采集芯片,每个通道采用Serial LVDS传输数据,实现简单且抗干扰性强,并且减小了实现通道间同步采集的难度,只需要保证各模拟输入接口到芯片相应通道管脚的链路间信号延迟接近即可,不用专门设计同步时钟电路[7,8]。

1.3 FPGA 选择

在设计中选用FPGA完成对ADC芯片控制和数据交互,对采集数据进行数字滤波处理,实现与PCI9054桥芯片及FIFO的信息交互等功能,根据设计需要可在FPGA内实现更多的数据处理和算法功能。

基于以上考虑,选用XILINX公司的Virtex5系列芯片(XC5VSX50T-2FFG665I),该芯片具有8 160个Virtex-5 Slices、4 752 Kb的 RAM、288 个DSP48E Slices(其中每一个DSP48E Slices包含一个25×18的乘法器、一个加法器及一个累加器)以及其他大量资源,设计中的8路数字滤波器耗用资源最多的,基本占用了接近一半的资源。该芯片可以很好地支持多种电平标准,方便与其他芯片互联,硬件上设计简单。可靠性高、功耗低及环境适应性等方面都满足设计要求[9]。

步话机里传来前方断断续续的声音:“报告师长,抓住五连一个逃兵,其余弟兄全部阵亡。全部阵亡。逃兵怎么处置,请师长指示。”

1.4 桥芯片选择

在桥芯片选择上主要基于以下考虑:

CPCI规范中规定 CPCI系统有 33 MHz和66 MHz两种,数据位宽有32 bit和64 bit两种。4个采集卡需要同时工作,通过分时复用共享CPCI总线带宽,所以需要选择合适的总线频率和总线位宽才能满足需求。

为了使8路AD采集卡有更强的适应性,设计中增加了CPCI接口中的J2作为自定义接口,这样模拟信号既可以从前面板输入,也可以通过自定义底板传输到8路AD采集卡中,因此CPCI总线只能选择32位总线。

根据系统要求估算每个采集通道每秒传输2 MB数据,32个通道每秒传输64 MB数据,因此需要总线带宽大于64 MB即可。在总线带宽理论上的简单计算公式是:带宽=(总线频率×数据位宽)/8,单位是MB/s,因此 33 MHz、32位的总线带宽极值为132 MB/s,66 MHz、64位的总线带宽极值为528 MB/s,根据最终设计的单个采集卡测试,采用DMA传输方式,在保证不丢失数据的前提下,可实现最高90 MB/s的数据传输率,所以总线选择32 bit,33 MHz可满足信号采集平台总线数据吞吐率的要求。

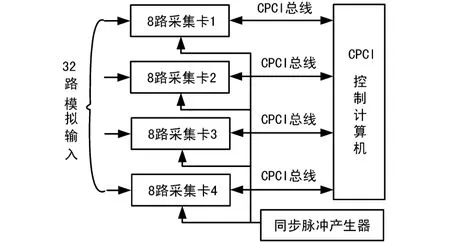

2 32路采集平台设计与实现

该平台主要由一个CPCI主板和4块采集卡构成。之所以采用多块采集实现32路采集,基于以下几点考虑:设计单块采集卡实现8路信号采集功能比设计单卡直接实现32路信号采集功能更容易,尤其是器件选型方面优势明显,能够将单卡设计的指标更高,总体性能指标很好保证,而且由于板卡尺寸的限制,前档板空间有限,模拟信号的接插件更容易选择方便操作和维护的型号。并且这种设计使得平台适应性很强,通过增加或减少采集卡个数满足模拟通道路数不同采集应用需求,在可靠性和维修等方面优势也很明显。

2.1 系统组成

该平台主要由4块8路采集卡、1块CPCI主板(即单板计算机)及4U CPCI机箱组成,可以对32路模拟信号同时进行采集和处理,并能通过CPCI总线传给主板进行相关处理,其原理框图如图2所示。

图2 32路采集平台原理

2.2 数据传输实现

2.2.1 驱动

板卡上采用了PCI9054,同时PLX提供了PLXMON 软件(V3.5),9054 的驱动(Pci9054.sys),inf文件(PciSdk.inf),还有库函数。将 PCI9054配制文件导入PLXMON软件中,根据需求进行修改,设置LocalDesAdrr为不同值,分别对应于卡1到卡4,并且需要在PciSdk文件中Driver information一项中添加相应信息,安装完成后可以在设备管理器中看到4个板卡设备。

2.2.2 采集软件设计

采集软件主要是将4块采集卡的数据进行录取、解包、存储和数据分析。PLX公司在提供驱动的同时还提供了相应的库函数,通过“封装”、调用这些函数可以实现与板卡的PCI接口通信,进而实现采集控制和录取数据等功能。通过PCI方式进行参数设置,简单信息交互;通过DMA方式可以进行大量数据传输,实现录取数据功能。

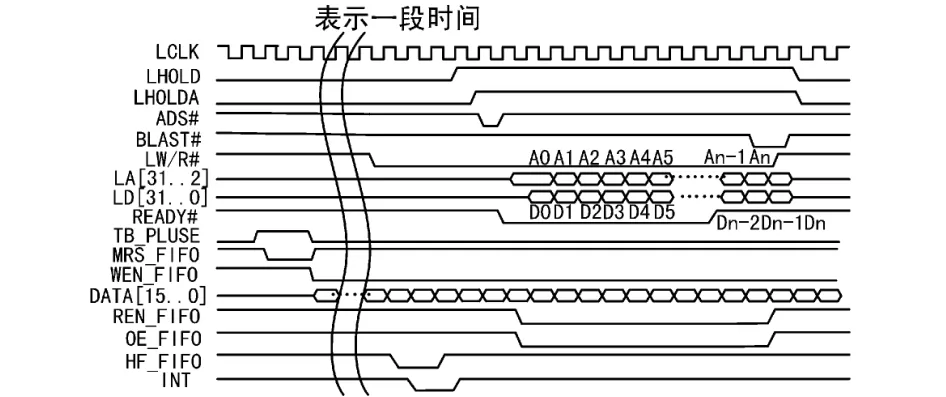

2.2.3 8路采集卡CPCI接口程序设计

FPGA数据传输程序原理:接收主板计算机采集软件发送的控制指令,包括选择采集方式(通过同步脉冲信号触发开始采集或软件通过上发指令主动开始采集),然后等待外部角触发信号(同步脉冲信号脉冲或主板发送的主动采集控制命令),信号到来后,首先发送低脉冲信号(MRS_FIFO)清空FIFO,然后将8路采集数据按规则打包,并发送给FIFO,当FIFO半满时半满标志(HF_FIFO)被置低,同时产生DMA中断信号(INT),FPGA控制产生DMA读时序,主板计算机DMA控制器响应中断,产生 LHOLD、ADS#、LW/R#和 LA[31..2]等信号,FPGA控制FIFO将存储容量一半(即256 KB)的数据通过9054传给主板计算机采集软件。采用同步脉冲信号触发方式的数据传输控制逻辑时序图如图3所示。采集软件通过PCI方式下发控制指令,可随时结束采集过程[10-12]。

图3 同步脉冲触发模式下数据传输控制逻辑时序

2.2.4 采集数据检验

为了防止采集数据丢失、错误以及板卡间数据错乱,在对采集数据打包过程中加入了标志字和校验数据,与8个通道采集数据组一帧,每帧数据内容依次是标志字、8通道采集数据和帧校验数据。标志字包括板卡代号信息和简单计数信息,例如:“A000”表示卡1第1组数据,“CFFF”表示卡3第4 096组数据;帧检验字即对帧内前9个数据按位异或得到的结果。通过板卡代号信息可以判别采集软件采集到的数据分别来自哪个板卡,防止板卡间数据错乱;通过计数信息可以知道有无丢帧,保证数据完整性;通过校验字可以确保数据传输正确。上述判别功能在采集软件中实现。

经工程应用检验,该方法能很好的确保数据正确传输,使用过程中没有卡间错乱和丢帧等问题。

3 结束语

详细介绍了32路采集平台的设计与实现,对软硬件设计中的若干问题作了说明和分析,并提出了实现方案,通过平台采集软件可实现对采集平台具体工作模式的配制,满足不同的应用需求,因此该采集平台有较好的适应能力,并体现了系统可重构的思想,应用面广,较好地满足了工程应用中对较多路信号采集的需求。同时通过Matlab对录取的数据进行综合分析,该平台很好地满足了工程技术需求,具有较高噪比,低误码率,采集通道间同步性好等特点,这些特点在工程应用中已经得到了体现。

[1] PICMG2.0D3.0 CompactPCI Specification[S],1999.

[2] 孙国良.基于FPGA的CPCI接口数据采集系统设计[D].北京:北京邮电大学,2009:17 -33.

[3] 张 奕,余海龙,谭剑美.四通道高速数据采集系统设计[J].现代电子技术,2012(9):10-12.

[4] 杨林楠,李红刚,张丽莲,等.基于FPGA的高速多路数据采集系统的设计[J].计算机工程 ,2007(7):35-37.

[5] 张 博,段哲民.基于 FPGA的数据采集系统设计[J].电子设计工程,2012(7):86 -88.

[6] 白同云.高速PCB电源完整性研究[J].中国电子科学研究院学报,2006(1):22-30.

[7] 杜建和.基于FPGA的高速信号采集与处理系统[D].云南:云南大学,2010:16 -17.

[8] 唐玉蓉.基于FPGA的高速数据采集系统的设计与实现[D].北京:北京邮电大学,2012:9-12.

[9] 郭金鹏,王蕴珠.大容量FPGA设计方法探讨[J].无线电工程,2008,38(1):51 -54.

[10]梁九鹏,李永亮,郑 佳.FPGA器件中PLL的设计应用[J].无线电工程,2007,37(9):62 -64.

[11]周银祥.基于U盘和单片机的FPGA安全配置的设计与实现[D].成都:电子科技大学,2010:1-4.

[12]齐怀龙.基于多 FPGA逻辑仿真系统的研究[D].重庆:重庆大学,2010:6-8.