基于FPGA的数字信号传输性能分析仪*

2013-12-29朱继瑜郝鹏程张成杰

卢 超,朱继瑜,郝鹏程,张成杰

(1.陕西理工学院物理与电信工程学院,陕西汉中723000;2.陕西省汉中中学,陕西汉中723000)

1 系统设计方案

系统采用Altera cycloneⅡ EPLC8Q208C8生成两组序列信号,m序列信号通过传输信道,然后在加上噪声信号伪随机序列信号在终端通过示波器观察信号的眼图,通过切换不同比特率和不同传输环境下的序列信号来观察发现信道的优劣以及不同比特率下的传输对信号的影响,以实现对数字信号分析的目的,实现数据传输速率在一定范围内且检测信号信噪比可调的简易便携数字传输性能分析仪。系统框图如图1所示,该设备的主要计数指标是:数字信号由M_list为f1(x)=1+x2+x3+x4+x8的m序列,信号率为在10 kbit/s~100 kbit/s内可按10 kbit/s步进可调;伪随机信号Noise_list为f2(x)=1+x+x4+x5+x12的噪声序列;数据率为10 Mbit/s,误差绝对值不大于1%;误差绝对值不大于10%,Manchester_cod是对M_list信号的曼切斯特编码后的输出信号,目的在于更加便于提取出位同步信号。

图1 系统功能框图

2 系统设计

2.1 SOPC系统设计

系统主要包括NiosⅡCPU、SDRAM控制器、和PIO接口,通过调用Altera公司提供对应的IP进行定制设计一个基于NiosⅡ的SOPC系统,由四部分组成:NiosⅡ模块块、PLL模和序列信号发生器模块。

NiosⅡ软核通过SOPC Builder中调用IP库组建实现,由NiosⅡ CPU、SDRAM控制器、通用IO、EPCS控制器、system ID、JTAG UART,与外部链接的端口主要5个部分,分别是系统时钟与复位、TFT LCD控制信号线、触摸屏控制信号线、SDRAM接口控制线、序列信号发生器控制信号线等,构成了整个系统的软件底层硬件平台部分,系统时钟100 MHz。

设计中考虑到片上RAM存储的数据量较大而NiosⅡCPU只负责UART串口的数据传输可简单的接口控制,故而选用了经济型内核,已达到节省资源占用的目的。SDRAM控制器用来连接板上集成的64MByte SDRAM,SDRAM控制器的数据端dq[15…0]必须连接输入输出端口bidir,在Presets中选择第一项Custom,在Bits中选择16,其他项不动,点击Next,点击Finish,完成SDRAM控刢器的设置。I/O口用于TFT LCD触摸屏的控制以及相关信号线,还包括信号的输出、SDRAM的控制信号线等。设计采用EPCS16配置芯片,为16Mbyte用于存储配置文件和片上系统的程序.System ID是一种标示符,类似校验,在下载程序之前或者重启之后,都会对其进行检验,以防止Quartus和NIOS程序版本不一致的错误发生。JTAG UART是实现PC和NiosⅡ系统间的串行通信接口,它用于字符的输入输出。PLL模块通过调用QuartusII内嵌的器件函数实现。

2.2 序列发生器

2.2.1 m序列

m序列,即最长线性反馈移位寄存器序列,其特征多项式可表示为:

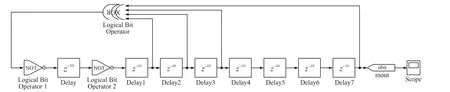

输出为f1(x)=1+x2+x3+x4+x8的m序列,利用在MATLAB中利用DSPBuilder构建一个m序列发生器,图2显示了DSP Builder模型表述,采用相连的延时单元组作为移位寄存器,在开始处使用两个非门,防止出使状态为 0,无法自启动,用异或(XOR)完成模四加运算,输出为mout。

图2 m序列发生器DSPBuilder设计电路

2.2.2 曼切斯特编码

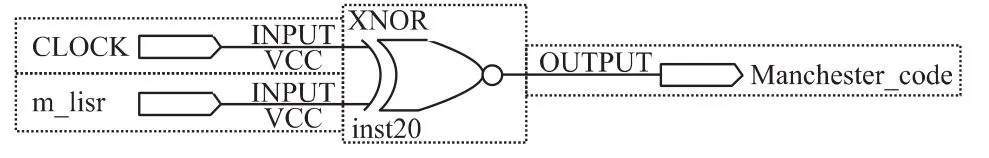

曼彻斯特编码是一个同步时钟编码技术,提供一个简单的方式给编码简单的二进制序列而没有长的周期没有转换级别,因而防止时钟同步的丢失,或来自低频率位移在贫乏补偿的模拟链接位错误。系统要求对数字信号发生器的m序列进行曼彻斯特编码,故将m序列码与其时钟信号取异或(XOR)非(NOT)即可,在Quartus II中使用原理图编程如图3所示。

图3 曼彻斯特编码电路

2.2.3 噪声信号发生器

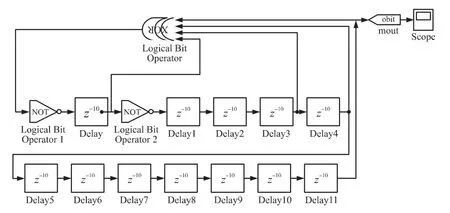

图4为伪随机序列f2(x)=1+x+x4+x5+x12的DSP Builder模型表述,采用相连的延时单元组作为移位寄存器,用异或(XOR)完成模四加运算,输出为mout。

图4 伪随机序列发生器DSP Builder设计电路

2.2.4 分频模块

分频模块是由Verilog HDL直接编程实现,将其转换成图像符号,加入到顶层图中,用于满足序列模块的不同时钟,从而实现系统的不同比特率的输出。设计要求系统序列输出比特率能够满足10 kbit/s~100 kbit/s步进可调,步进量为10 kbit/s,因此分频模块负责将经过倍频后的180 MHz的时钟信号clk_180进过分频至10 kbit/s~100 kbit/s,提供给序列信号时钟。CLOCK为20 MHz的本地时钟,经过二分频后输出10 MHz给噪声信号发生器,输出10 Mbit/s的噪声信号,rest为分频模块的复位信号。

2.3 SOC系统软件设计

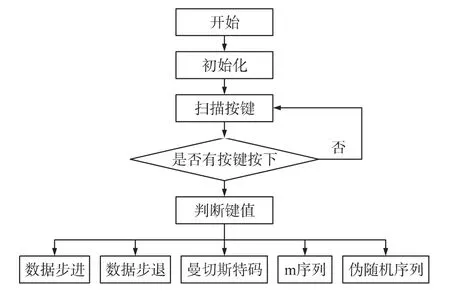

片上系统的软件设计在NiosⅡ IDE中通过C语言编程实现,程序通过中断方式在判断是否触摸位置为有效区,从而来进行波特率的切换及码元的切换,此外包括TFT LCD的显示等,主程序流程图如图5所示。

图5 主程序流程图

在触摸屏程序设计时,通过端口扫描是否有触摸,当有触摸时先判断是那个区域有触发,如果是码元切换区域则进行码元的切换;如果是波特率的步进设置则进行波特率的加减设置。详细触摸屏程序流程图如图6所示。触摸屏的设计与键盘的区别就在于需要精确的判断触摸的位置,在触摸时电阻屏将所触摸的位置转化成电压信息因此根据不同的电压信号来判断位置。程序通过扫描的方式来判断是否有触摸,当检查到有触摸时进入触摸屏处理子程序,为了防止误触,因此在设计时先进行软件滤波。

图6 触摸屏子程序流程图

系统的界面设计主要涉及到中英文显示、背景颜色的显示、字体大小颜色等等。由于TFT LCD内部不带字库,因此在进行软件设计时需要通过字模软件对需要显示的字进行编码建模。字符的编码建模包括ASCII字符编码和汉字编码两个部分。在程序开始时先初始化界面,当触摸屏有触发时,返回来的参数值FLAG,先判断FLAG的值,为0则切换显示当前码元的类型,为1则切换显示波特率的值。

2.4 SDRAM的电路设计

2.4.1 FPGA与SDRAM接口设计

设计采用的是Altera公司提供的片上SDRAM控制接口IP,因此不用单独设计接口时序,将调用的IP模块的接口连接至片外SDRAM接口,主要包括 sdram_addr[11:0]、bank_addr[1:0]、cas_n、cke、cs_n、dq、dqm、ras_n、we_n 等接口控制线。SDRAM的时钟信号CLK采用FPGA的内部PLL生成,要注意片外SDRAM的时钟输入必须比系统的时钟滞后-75°相位。(不同型号的SDRAM时钟偏移度不同)

2.4.2 FPGA下载配置电路设计

配置又称下载,是对FPGA的内容进行编程的一个过程。每次上电后需要进行配置,是基于SRAM工艺FPGA的一个特点。在FPGA内部,有许多可编程的多路器、逻辑、互联节点和RAM初始化内容等,都需要配置数据来控制。Altera的FPGA器件有3类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式,本系统的配置电路中设计了两种配置方式即AS配置和JTAG配置模式,AS配置在系统掉电时可将配置数据保存在EPCS16的配置芯片中,配置文件为.pof文件;JTAG配置是为了便于系统的调试而专门设置的,掉电不保存,配置文件为.sof文件,图7为EPCS16配置芯片与FPGA的两种配置方式的电路图。

2.5 TFT LCD与触摸屏电路设计

设计采用320*240的TFT LCD显示屏触摸屏为电阻式触摸屏,控制芯片分别为sd12900和XPT2046。由于采用的是片上系统,FPGA与TFT和触摸屏模块接口电路由片上系统生成的I/O口直接与TFT和触摸屏控制接口连接,对其进行控制操作。为了满足电平兼容,TFT触摸屏模块采用3.3V供电电压,电源取自于FPGA核心板电源,保证了系统的电源完整性与稳定性。其中TFT控制信号LCD_CS、LCD_DATA、LCD_LIGHT、LCD_RD、LCD_REST、LCD_RS、LCD_ER 分别为片选信号、数据、背光、读信号、复位、读控制和写控制,触摸屏控制信号 TS_CS、TS_IN、TS_IRQ、TS_OUT、TS_SCLK分别为片选、输入、中断、输出、时钟信号。

图7 FPGA配置接口电路

3 系统测试与分析

开发工具主要是Altera公司提供的QuartusII9.0、DSPBuilder9.0、NIOS IDE9.0 和 Mentor公司的仿真工具ModelSim6.4a,编程语言包括VerilogHDL、C语言、MATLAB编辑语言,VerilogHDL语言主要是在Quartus II中完成相关模块的建立,C语言是在NiosⅡIDE平台里完成TFT触摸屏的控制显示与读写,MATLAB编辑语言主要指在集成于MATLAB中的DSP Builder的模型工具完成序列的建立与HDL的导出。系统测试中,主要是在实验室里通过建立不同的传输信道将系统生成的不同比特率的序列码加在进去,在输出端连接至示波器观察其传输信号的眼图,评测其误码率与信道的优劣,测试主要包括以下五个部分:

(1)测试数字信号序列f1(x)=1+x2+x3+x4+x8的m序列的比特率是否正确,10 kbit/s~100 kbit/s之间连续步进为10 kbit/s;

(2)测试数字信号序列f2(x)=1+x+x4+x5+x12的m序列数据率为10 Mbit/s,误差绝对值不大于1%,误差绝对值不大于10%;

(3)利用f1(x)=1+x2+x3+x4+x8产生的时钟信号,在示波器上显示数字信号该信号的信号眼图,并测试眼幅度;

(4)测试f1(x)=1+x2+x3+x4+x8序列采用曼彻斯特编码后的波形;

(5)模拟一个传输信道将f2(x)=1+x+x4+x5+x12序列与f1(x)=1+x2+x3+x4+x8同时添加在该信道中进行传输,在终端观察眼图分析噪声对信号质量的影响。

按照测试步骤连接至示波器(UTD2062CEL,60 MHz 1 GS/s)测试各项数据波形如图8所示,包括m序列发生器、曼切斯特编码、噪声序列发生器的示波器显示波形。

图8 各项数据波形的显示

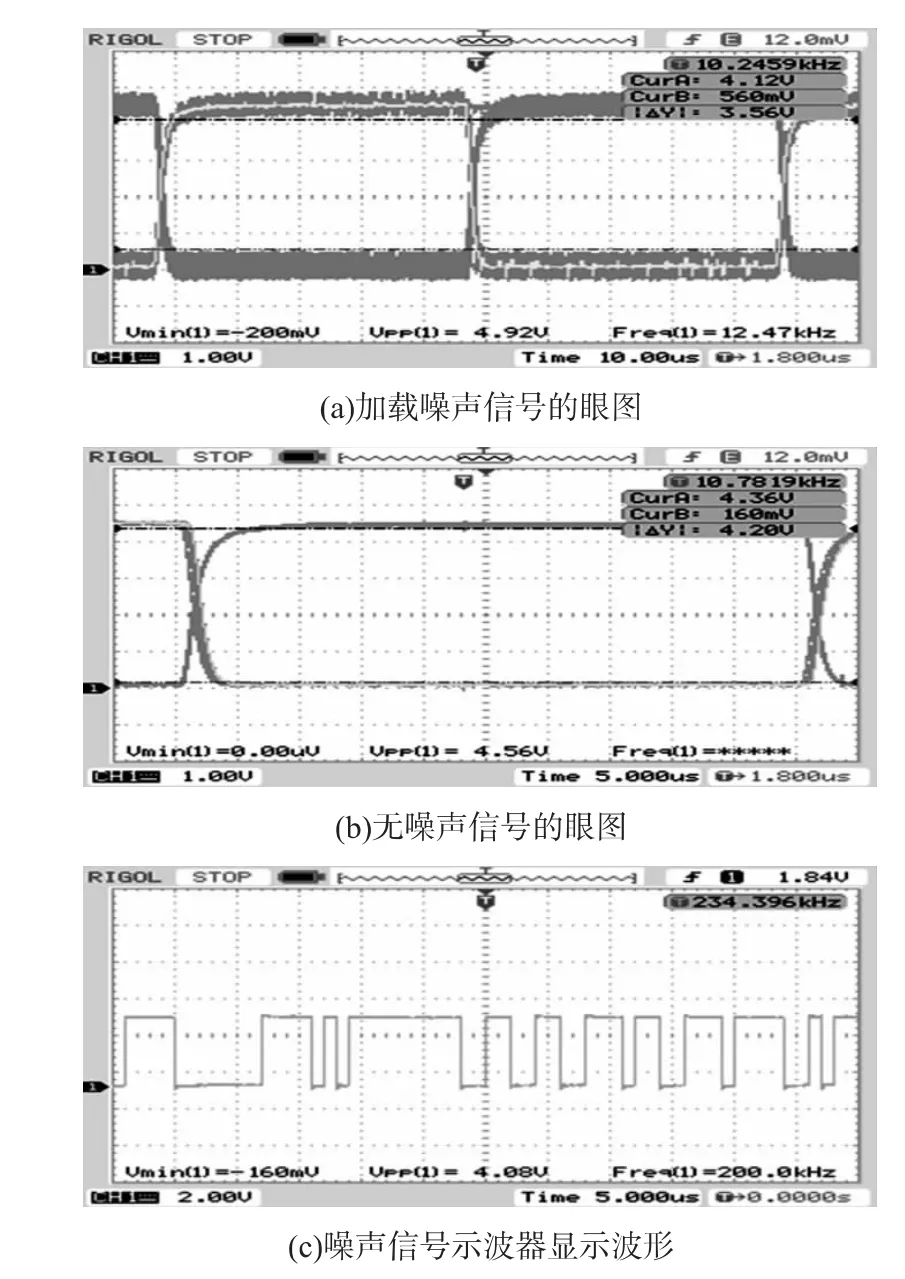

加载噪声信号的眼图如图9(a)所示,无噪声信号的眼图如图9(b)所示,测试条件均为:200 kHz低通滤波器、10 kpbs m序列曼彻斯特编码。噪声信号3.56 V,显示的眼图幅度4.2 V。在原有噪声的基础上,慢慢增大噪声信号的幅值,随着信噪比的降低,还能提取同步信号,并正确的显示开始慢慢闭合的眼图。

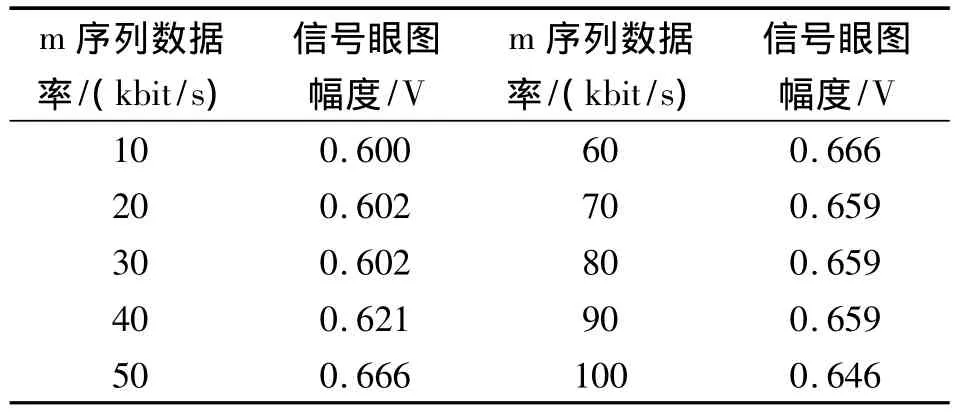

经过测试数字信号发生器的波特率能够达到10 K到100 K步进可调的方波信号,伪随机信号发生器输出了10 MHz的方波信号,m序列数据率的测试如表1所示,可以计算出数据率平均误差为0.157 6%。在fH=200 kHz,伪随机信号 100 mV,输出的TTL=4.46VP-P时,测得眼图幅度为表2所示,均达到系统要求的指标。

图9 各种信号眼图的显示

表1 m序列数据率的测试表格

表2 眼图幅度

存在误差的原因主要是认为误差、硬件误差、测量仪器误差等,此外在测试为随机信号的时钟时发现其时钟信号有信号的反射现象,进过分析发现如果IC之间的互连线比较长,线的特性阻抗又不均匀,或者终端没有匹配,会引起反射,如果始端也不匹配,则会来回反射而造成振铃。该现象的决定因素:特性阻抗、匹配方式、失配大小终端反射系数、始端反射系数、线长,分析原因是因为电路板是手工焊接的,信号完整性不是太好,同时也由于传输阻抗不匹配,因此通过在时钟信号线的终端和源端分别串接一个33 Ω的电阻发现这种振铃现象得到了很大的抑制。

4 结束语

设计的数字信号传输性能分析仪采用Altera公司的Cyclone II系列的FPGA芯片EP2C8Q208C8,实现了波特率步进为10 kbit/s的m序列发生器与曼彻斯特编码,并通过测量眼图的幅度来分析不同信道环境对信号传输的信号完整性及码间串扰的影响,该分析仪采用TFT触摸屏,操作方便,人机交互性好,可广泛推广。

[1]孙盼,姚佳毅,林阅斌.基于FPGA的数字信号传输性能分析仪[J].电子科技,2012(8):32-34.

[2]张骁,宋杰,丁昊.基于FPGA的简易数字信号传输性能分析仪[J].电子测量技术,2012(8):78-81

[3]张芳芳,周火凤,宋丽辉,等.基于DSP和USB的数据采集系统的设计[J].仪表技术与传感器,2010(7):66-68

[4]邓岳平,肖铁军.基于FPGA的并行DDS信号发生器的设计与实现[J].计算机工程与设计,2011(7):2319-2323

[5]褚改霞,潘卫,王栋,等.基于FPGA的多路数字信号复分接器的设计[J].电子技术应用,2009(5):43-46.

[6]李娜,王克甫,吕洁.基于FPGA的数字信号源设计[J].吉林师范大学学报(自然科学版),2006(1):27-28+40.

[7]盛祥佐,徐钊,罗文超.基于FPGA的数字信号发生器及其在QPSK调制中的应用[J].工矿自动化,2007(4):69-72.

[8]李永杰,凌朝东.数字信号处理的FPGA实现[J].电子技术应用,2008(7):19-21.

[9]刘文,冯燕,王巍.基于PCI的DSP+FPGA数字信号处理平台[J].科学技术与工程,2008(9):2348-2351,2355.

[10]袁俊泉,皇甫堪.基于DSP与FPGA的实时数字信号处理系统设计[J].系统工程与电子技术,2004(11):1561-1563.