一种电机驱动芯片的欠压保护电路设计*

2013-12-29黄武康徐建华

湛 衍,姚 远,黄武康,徐建华

(1.中国科学院微电子研究所,北京100029;2.中国科学院嘉兴微电子与系统工程中心,浙江嘉兴314006)

现代高效的、精确的电机控制都是采用计算机实现的,通过电机芯片与主处理器、电机和增量性编码器构成一个完整的运动控制系统。当电源电压低于芯片的正常工作范围时,芯片内部某些电路可能无法正常工作,这有可能产生内部逻辑错误,使外部开关管处于不确定状态。若外部开关管处于导通状态而芯片的其他部分不能正常工作时,有可能使芯片烧毁,或对外部电路造成损坏,因此,芯片内部加入欠压保护电路是必需的,可以保证电源电压低于设定的工作门限时,外部功率管和芯片内部的大部分模块处于关断状态[1-2]。

由于欠压保护电路工作时,芯片带隙基准电路和LDO(Low Dropout Regulator)模块还没有正常工作,也就是说,欠压保护电路必须具有基准电压。

为了使触发电压不随着工艺、温度等变化,基准电压必须是一个不随温度、工艺等变化的电压。在现有技术的欠压保护电路中往往具有基准电路部分以产生基准电压,使用比较器将采样来的电源电压信号与基准电路产生的基准电压信号比较[3]。

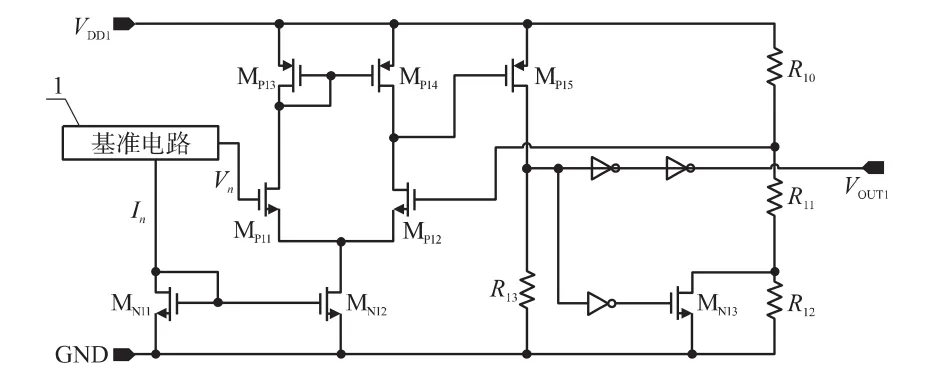

如图1所示的现有技术的欠压保护电路具有基准电路1和比较电路,基准电路1产生基准电流In和基准电压Vn,比较电路将采样来的电源电压VDD1的信号与基准电压Vn的信号比较,判断是否发生欠压。其中,当未发生欠压时,VDD1>Vn,VOUT1输出高电平(VOUT1=1)以控制电机驱动芯片正常工作;当发生欠压时,VDD1<Vn,VOUT1输出低电平(VOUT1=0)以控制电机驱动芯片停止工作。但是,这类现有技术的欠压保护电路容易受到用以产生基准电压的基准电路的干扰,因此需要设计专门的比较器电路,结构相对复杂。

图1 传统欠压保护电路

有鉴于现有技术的上述缺陷,本文提出了一种新的欠压保护电路,省去了额外的产生基准电压的基准电路和比较器电路[4-5]。电路具有传输延时较小的优点,能快速的产生欠压信号,一方面使电机驱动芯片在发生欠压状况时快速停止工作以免造成损坏,另一方面使电机驱动芯片在消除欠压状况后能快速恢复正常工作[4]。

1 电路结构及工作原理

1.1 电路结构

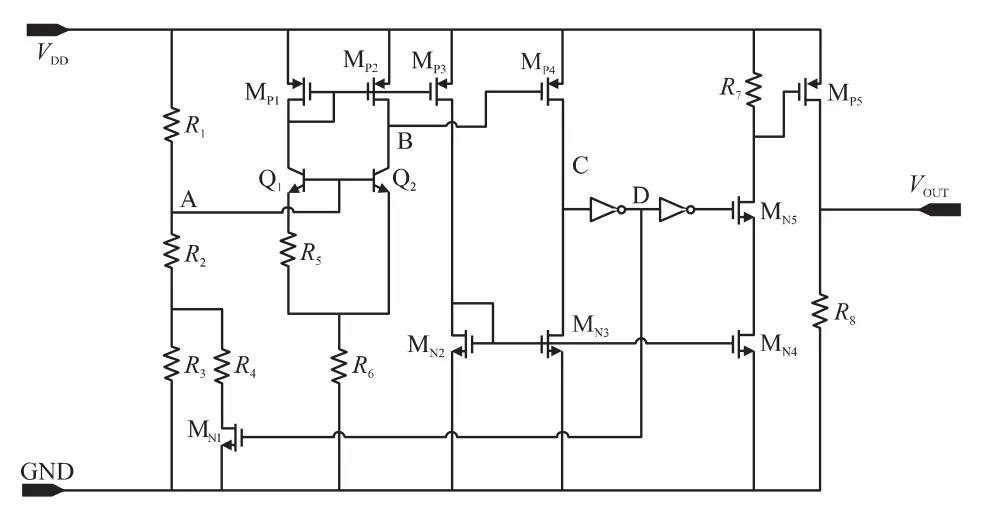

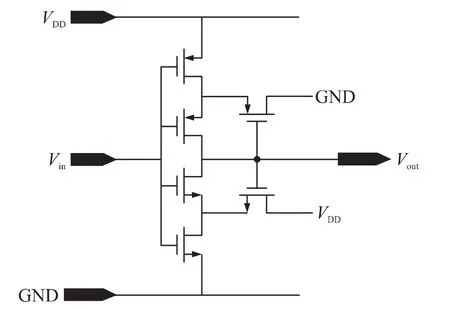

整个欠压保护电路如图2所示,该电路由2个三极管Q1、Q2、两个施密特反相器、5个N型MOS管、5个P型MOS管和若干个电阻构成。其中,三极管 Q1、三极管 Q2、PMOS 管 MP1、PMOS 管 MP2、电阻R5和电阻R6构成带隙基准电路;PMOS管MP1、MP2、MP3构成第一电流镜电路;NMOS管 MN2、NMOS管MN3和NMOS管MN4构成第二电流镜电路。电阻R1、R2、R3构成电源电压VDD采样电路,NMOS管MN1与电阻R4构成迟滞回路。NMOS管 MN4、MN5、MN6和电阻R7、R8为电路输出级,提供足够的输出能力。

图2 改进后的欠压保护电路

1.2 工作原理

三极管Q1、Q2是两个NPN型三极管,两者的发射极面积之比为n:1,即三极管Q1的发射极面积是三极管Q2的发射极面积的n倍。

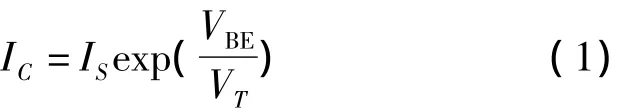

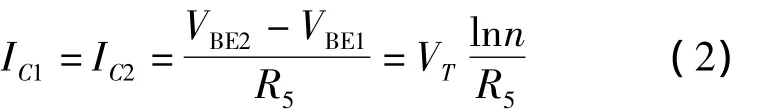

对于一个正向偏置的三极管,有[6]

当VDD电源电压从零开始上升,三极管Q1、Q2的基极A点电位达到阈值VA后,Q1、Q2开始导通,它们所在的支路形成电流通路,P型MOS管MP1、MP2组成的电流镜结构使得这两路电流大小相等[7],B点电位降低,导致P 型 MOS 管 MP4、MP5的栅极电位下降,C点电位随之上升,信号经过两个反相器整形,同时形成一个滞回信号D,最后通过电路输出级输出的逻辑电平为高。同理,当电源电压VDD逐渐下降时,输出的逻辑电平为低。此输出信号提供给后级电路开启或关断关键模块电路,起到保护电路的作用。

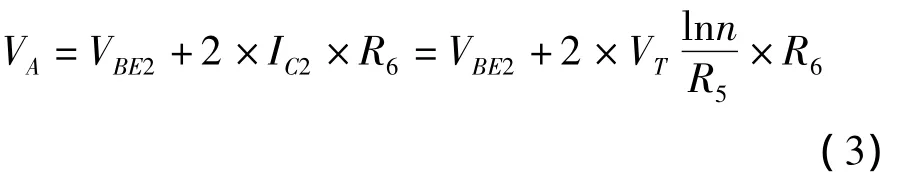

设流过三极管Q1和Q2的电流分别是IC1、IC2,根据上述分析可得

因此,要使得Q1、Q2导通的阈值电压为

根据电阻分压公式,可得电源电压的阈值电压

NMOS管MN1与电阻R4构成迟滞回路,当电源电压VDD超过VDDthresholdH后,D点电位由高变低,MN1管关断,电阻R4被断路,因此当电源电压由高变低时,需要降到比VDDthresholdH更低的一个电压VDDthresholdL才能使逻辑输出电平翻转。迟滞量如式(6)所示。

P型MOS管MP3镜像MP1管中的PTAT(Proportional To Absolute Temperature)电流,再经过 N型MOS管MN2、MN3组成的电流镜给 P型 MOS管 MP4提供偏置电流。

进一步地,VT=kT/q为正温度系数,VBE为负温度系数。因此通过合理设计n、R5和R6的值,可以实现VDDthreshold的零温度系数,尽可能降低温度的变化对VDDthreshold所引入的误差[8]。

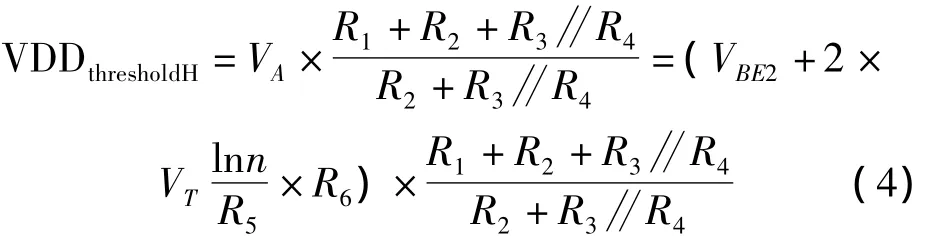

电路中的两个反相器采用施密特反相器结构,作为核心电路和输出级之间的缓冲级,同时提供滞回信号,其具体电路如图3所示。

图3 施密特反相器

2 仿真结果及分析

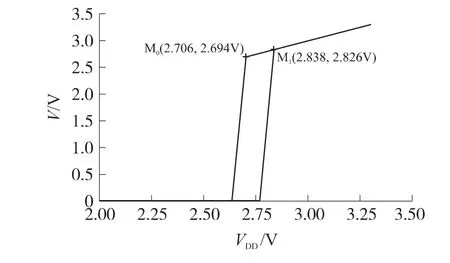

基于国内先进的BCD 0.35 μm工艺模型,采用Cadence Spectre仿真工具进行电路仿真,本设计电源提供数字逻辑和模拟电路的VDD电压范围为3.3 V~5 V。

图4 仿真结果

当电源电压低于2.7 V时,电路输出变低电平;当电源电压重新升高至2.83 V时,电路输出回到高电平,迟滞量为0.13 V左右,满足电路应用要求。

3 结论

本文首先分析了传统欠压保护电路的缺点,然后基于0.35 μm BCD工艺,设计并实现了一种新型欠压保护电路,可应用于电机驱动芯片等领域。本设计电路结构较为简单,不需要额外的带隙基准电路,省去了电压比较器电路,大大减少了电路的复杂性。与此同时,考虑到器件的温度特性,电路引入温度补偿,以此减少温度变化对电路翻转阈值和迟滞量精确度的不良影响。最后使用Cadence Spectre仿真工具进行仿真,结果表明电路工作正常,在电源电压欠压时及时输出逻辑电平信号,具有迟滞功能。

[1]王智鹏,杨虹.一款无电压比较器的欠压保护电路[J].电子世界,2012(7):51-52.

[2]钱金川,朱守敏.一种过压欠压及延时保护电路的设计[J].机床电器,2008(1):57-59.

[3]赵春波,许伟,吴玉广.一种CMOS欠压保护电路的设计[J].集成电路与元器件,2004(10):172-174.

[4]邹雪城,韩俊峰.一种基于比例电流的欠压保护电路的设计和实现[J].华中科技大学学报(自然科学版),2007(35):64-66.

[5]王锐,唐婷婷.一种BiCMOS欠压保护电路的设计[J].电子科技,2006(10):76-78.

[6]Allen P E,Holberg D R.CMOS模拟集成电路设计[M].北京:电子工业出版社,2005.

[7]Gray P R,Meyer R G.Analysis and Design of Analog Integrated Circuits[M].John Wiley,2001.

[8]毕查德.拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2003.