基于IEEE Std1500标准的互连检测构架设计

2013-12-29颜学龙

孙 元,颜学龙,李 鹏

(桂林电子科技大学电子工程与自动化学院,广西桂林541004)

在当今主流工艺条件下,互连线的耦合电容已经占据总电容的60%~70%,随着半导体工艺的继续进步,互连线耦合电容与其总电容的比值将不断增大,因此由耦合电容噪声导致的信号完整性问题成为IC设计的主要挑战之一[1]。SoC芯片在深亚微米工艺和GHz工作频率下工作时所产生的互容和互感,使得连接IP核的系统总线常常发生相互干扰,产生串扰故障[2]。针对串扰故障,国内外一些学者已经提出了许多故障激励检测模型,如MAF模型[3]、MT 模型[4]、HT 模型[5]。

为了解决SoC测试面临的挑战,IEEE组织制定了 IP 核测试标准—IEEE Std 1500[6-7],旨在标准化IP核测试接口,使得IP核的测试变得方便高效。IEEE Std 1500标准定义的硬件结构是环绕在IP核周围的一个标准的可配置的芯核外壳(Wrapper)。Wrapper与周围环境隔离,使得内核既可以做为单独实体检测,也可以进行内核与内核之间的互连测试。

本文通过对MT故障模型的冗余分析,将测试矢量分为两类进行精简,选取种子产生改进型MT模型。并对MT模型和改进型模型的测试矢量数、种子数、施加的时钟数进行计算和比较。在IEEE Std 1500标准下,对可扩展的IP核测试壳各部分进行设计,使测试壳在不同的测试指令下,产生全部的测试矢量集。软件仿真得到的波形结果验证设计的可行性。

1 MT模型及冗余分析

1.1 MT模型

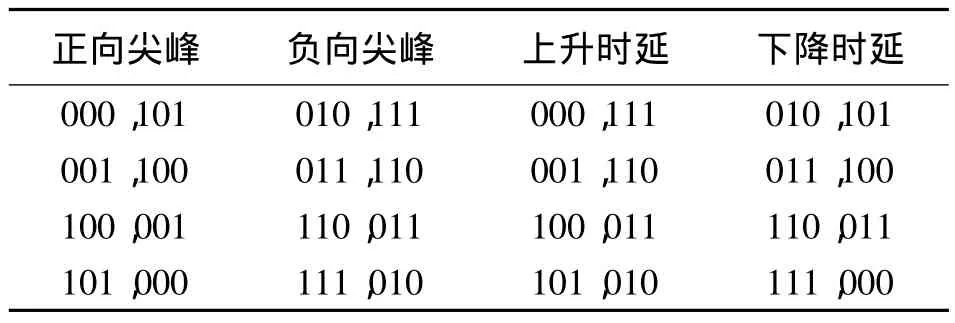

Mohmmad H提出的多重跳度MT(Multiple Transition)故障模型,它同时考虑了交叉耦合电容和电感对互连线的影响,可以确保潜在的信号完整性故障被全部检测出来。MT模型针对的串扰故障主要有4类,即正向尖峰脉冲、负向尖峰脉冲、正跳变延时、负跳变延时。MT模型对测试矢量集的定义为:施加在攻击线上的测试矢量对必须同时发生翻转,而施加在受害线上的激励可以保持静态或翻转。假设互连系统中同一时刻只有一个受害线(简写为V线),其他的互连线均为攻击线(简写为A线)。三线系统中,中间线为V线其余为A线的MT模型测试矢量集如表1所示。

表1 MT模型测试矢量集

MT模型具有100%故障覆盖率。n线系统所需要的种子数为n×2n-1,矢量数为n×2n+1,采用PGBSC(改进的边界扫描单元)产生测试矢量时施加的时钟(update)数为:5n×2n-1。

1.2 冗余分析

MT模型在提供了100%故障覆盖率的同时也存在大量的测试矢量冗余。在MT模型中,存在许多测试矢量对(V1,V2),它的向量V2和其他测试矢量对的向量V1相同,可以将这两组测试矢量对合并,生成包含3个矢量的矢量组,它可以连续激励串扰缺陷两次,同时某些矢量对可以同时激活多根受害线上的串扰缺陷,但是在原始的故障检测模型中,这些测试矢量对被多次重复的应用[8]。测试矢量冗余情况可以根据两方面进行分析:

(1)不同受害线的时延故障测试矢量冗余:由于MT模型的时延故障测试矢量产生机理是受害线和攻击线同时发生跳变,但并没有对正向跳变还是负向跳变进行要求。因此相同的时延故障测试矢量可以同时激励不同受害线的时延故障。例如表1中测试上升时延故障的测试矢量对P(000,111),不仅是中间线为受害线的时延故障测试激励,同时可以测试第1根线和第2根线为受害线时的时延故障。

(2)中间向量相同的测试矢量冗余:如表1中测试尖峰故障的测试矢量对 P1(000,101)和P2(101,000),测试矢量对P1的向量V2和测试矢量对P2的矢量V1相同,存在向量冗余。可以将双矢量的向量组P1、P2变成3向量的1个矢量组P(000,101,000)或 P(101,000,101);测试时延故障时,测试矢量对 Q1(000,111)和 Q2(111,000),中间测试矢量相同,可以精简为3矢量的测试矢量组Q(000,111,000)或 Q(111,000,111)。

2 改进型MT模型

改进型MT模型在时延故障和尖峰故障两方面对传统MT模型进行精简。通过对不同的故障模型种子的选拔,最终得到了改进模型的测试矢量集。本节提出了N线系统的具体改进方法、模型的参数计算及比较。

2.1 N线系统

改进1 针对时延故障的矢量冗余精简。时延故障测试矢量集的产生机理是受害线与攻击线同时发生翻转。根据产生机理,当测试时延故障时,所有传输线均可视为受害线。为此,可将所有传输线同时翻转的测试矢量集,做为所有受害线的时延故障测试矢量集。而具有相同矢量的测试矢量组可以精简为1个3矢量的矢量组。种子的选择与矢量变化如下:

(1)找到所有传输线可能的跳变情况。

(2)总有2个测试矢量,它们的所有信号跳变相反,从中选择1个作为测试时延故障的种子。例如3线系统的001与110,选择其中的1个001或100。

(3)所有的种子跳变2次得到全部的测试矢量组。

改进2 针对尖峰故障—尖峰故障的测试矢量集的产生机理是受害线保持不变,攻击线同时翻转。根据第2类矢量冗余分析,将2个具有相同矢量的矢量对精简为1个3矢量的尖峰测试矢量组。种子的选择与矢量变化如下:

(1)选定要检测的对象为第i根受害线。受害线保持不变,其余传输线作为攻击线。

(2)受害线相同,攻击线信号正好相反的2个测试矢量只选择1个。

(3)受害线与攻击线的信号都相反的2个测试矢量只选择1个。

(4)通过(2)、(3)的筛选,得到测试尖峰故障的种子。种子的受害线每跳变1次,攻击线跳变3次,1个种子共得到6个测试矢量。例如3线系统种子000的变化:000→101→000→111→010→111。

2.2 改进型MT模型N线系统的参数计算:

由上节的筛选方法得到种子数C:

式中:Cp表示改进1的种子数,Cq表示改进2的种子数。

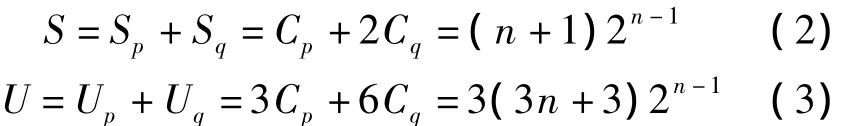

根据改进1和改进2不同的矢量变化情况,所需要的测试矢量数S和施加的update数U计算公式如下:

式中:Sp表示改进1的测试矢量数,Sq表示改进2的测试矢量数,Up表示改进1的update数,Uq表示改进2的update数。由此可见,改进型MT模型所需要的矢量个数明显小于传统MT模型。当n>2时,MT精简模型种子数小于传统MT模型。当n>1时,MT精简模型施加的update数小于传统MT模型。

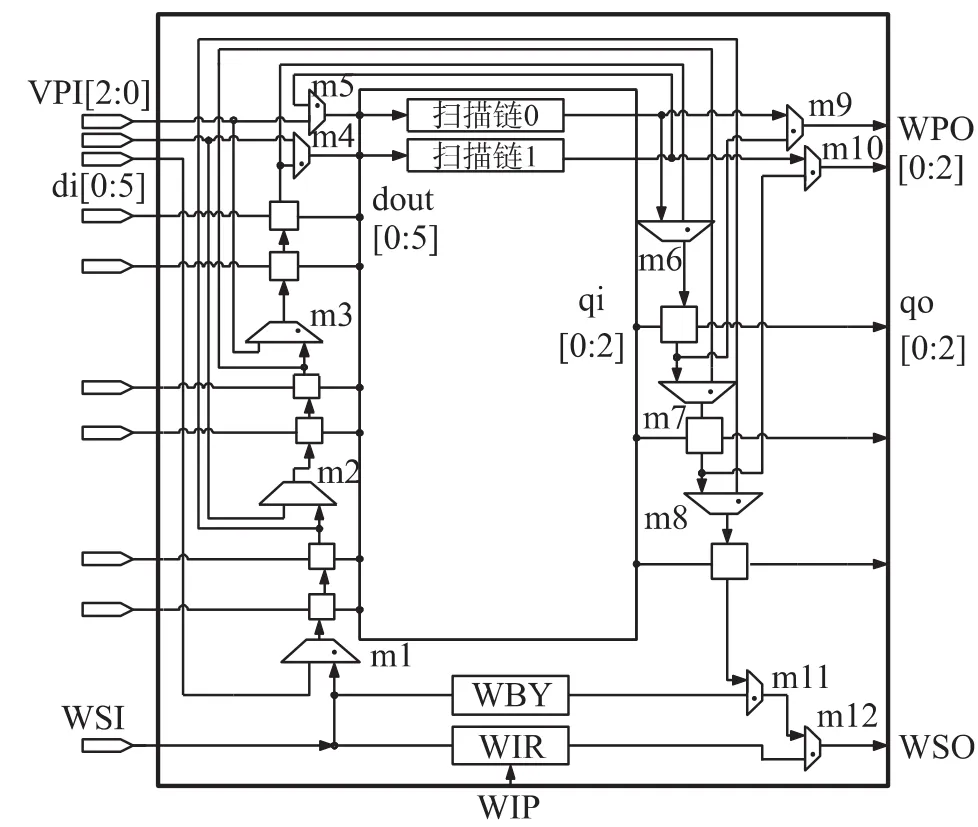

3 IEEE Std 1500外壳构架设计

IEEE Std 1500协议针对IP核的测试与访问定义了一种独立的、标准化的、可升级的可测试性架构[9],是环绕着IP核特殊的“壳”。它主要由6部分组成:串行访问接口WSI/WSO、并行访问接口WPI/WPO、旁路寄存器(WBY)、边界寄存器(WBR)、指令寄存器(WIR)、测试壳控制端口(WIP)。

本文采用自行设计的带进位的二级加法器作为IP核为例,按照IEEE Std 1500标准设计的测试壳的结构如图1。各部分的设计如下。

图1 测试壳结构

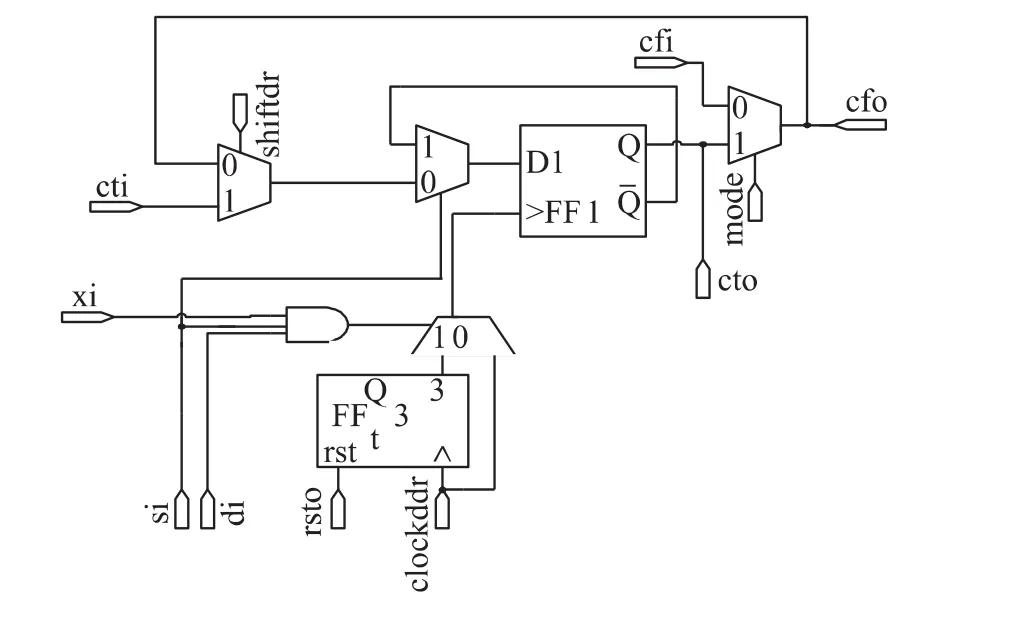

3.1 测试壳边界寄存单元WBC

测试壳边界单元WBC是WBR的基本组成单元,能实现测试激励的施加和测试响应的捕获,从而实现对IP核的可控制性和可观察性[6,10]。WBC数据端口包括:测试输入(CTI),测试输出(CTO),功能输入(CFI),功能输出(CFO)。WBC基本操作功能及数据路径:正常功能操作(CFI-CFO),扫描测试时扫描移入操作(CTI-CTO),扫描测试模式下将扫描数据施加到功能端口(CTI-CFO),扫描测试模式下捕获测试响应进入测试环单元(CFI-CTO)[11]。本文基于这一思想,对BSC单元进行设计,作为改进型MT模型测试矢量的硬件实现。设计的测试环单元具体结构如图2所示。

图2 改进WBC单元原理图

为了符合改进型MT模型测试矢量的生成要求,WBC单元在IEEE Std 1500的基础上4方面进行改进:

(1)使用di选择信号,用于对时延故障和尖峰故障两种故障测试方式进行选择;

(2)设置si端口对输入信号进行选通或者翻转;

(3)当进行尖峰故障检测时,在xi端输入受害线选择信号;

(4)采用四分频器确保测试尖峰故障时受害线每翻转一次,攻击线翻转三次。

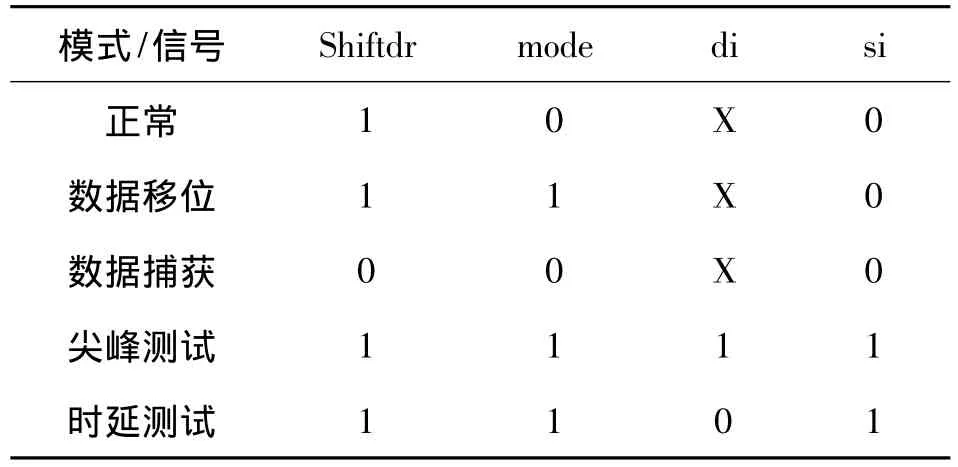

测试模式如表2所示。

表2 测试模式

3.2 指令寄存器

指令寄存器由3部分构成:移位寄存器、更新寄存器、指令译码逻辑。本文的指令编码有4位,控制信号有12个。控制信号从低位到高位分别为:m1~m12。

Wrapper的整个操作是都由WIP的控制信号以及载入到WIR的指令控制的。针对串扰故障的串行测试和并行测试,设计了5个WIR指令编码,具体如表3所示。

表3 WIR指令码及控制信号

4 仿真结果

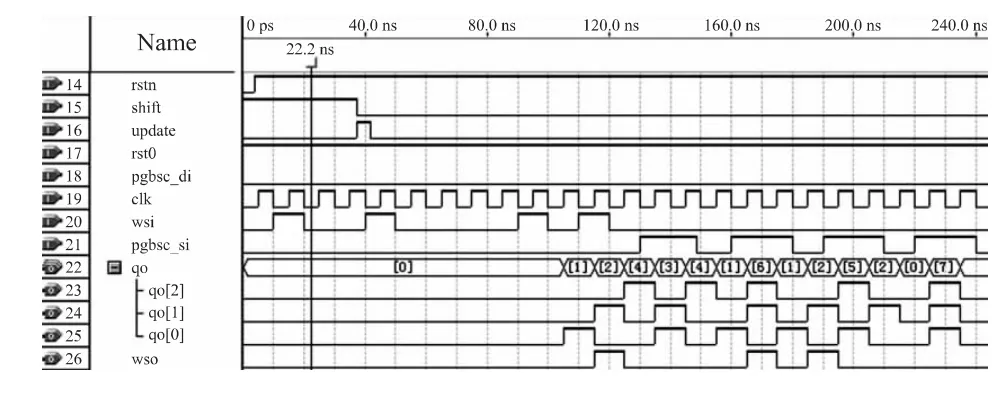

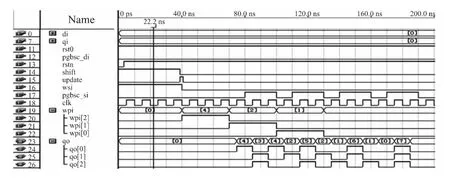

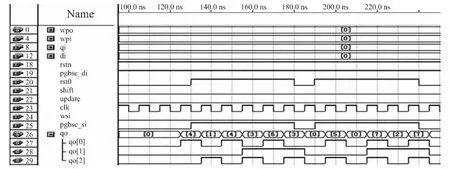

本文采用Verilog HDL语言描述测试壳各部分,并连接成测试壳。通过Quartus ii软件进行仿真。3线系统的改进型MT模型采用尖峰故障和时延故障两部分生成。时延故障通过施加种子000、001、010、100产生全部的时延故障测试矢量;尖峰故障通过施加种子000、001,产生中间线为受害线时全部的尖峰故障测试矢量。

图3和图4表示在指令为串行互连外测试时,qo端生成改进型MT模型的测试矢量。其中图3的测试矢量是在第13个时钟开始产生。

图3 串行外测试的时延故障测试

图4 串行外测试的尖峰故障测试

图5和图6表示在指令为并行互连外测试时的改进型MT模型测试矢量生成。

图5 并行外测试的时延故障测试

本文改进的MT模型与传统MT模型在不同总线系统所需测试矢量数的比较如表4所示。从表4可以看出:本文改进的MT模型在故障覆盖率为100%的前提下,测试速率提高,施加的测试矢量减少。而且随着N线系统的复杂性增加,精简的效果越明显。

图6 并行外测试的尖峰故障测试

表4 改进型MT模型与传统MT模型的比较

5 结论

本文首先在原有的MT模型基础上提出了改进型MT模型,减少了MT模型的矢量冗余,降低了测试成本,体现了改进型MT模型的高效性。然后对IEEE Std 1500协议标准定义的测试壳进行设计,实现了改进型模型对SoC的IP核互连线的串行测试和并行测试,体现了改进型模型的实用性,为集成芯片的测试问题的发展提供了一定的理论基础和技术支持。

[1]张富彬,H O Ching-yen,彭思龙.静态串扰噪声识别算[J].电子器件,2006.

[2]Narender,Hanchateand,Nagarajan,et al.Simultaneous Interconnect Delay and Crosstalk Noise Optimization through Gate Sizing Using Game Theory[J].IEEE Transactions,2006,55:1011-1023.

[3]Cuviello M,Dey S,Bai X,et al.Fault Modeling and Simulation for Crosstalk in System-on-Chip Interconnects[J].Proceedings of the IEEE/ACM International Conference on Computer-Aided Design,1999:297-303.

[4]Mohammad H T,Nisar Ahmed,Mehrdad Nourani.Testing SoC Interconnects for Signal Integrity Using Extended JTAG Architecture[J].IEEE Trans CAD of IC and Syst,2004,23(5):800-811.

[5]张金林,沈绪榜,陈朝阳.SoC中IP核间互联总线完整性故障测试模型[J].电子科技大学学报,2007.

[6]IEEE Std 1500.IEEE Standard Testability Method for Embedded Core Based Integrated Circuits[S].2005.

[7]Institute of Electrical and Electronic Engineers:IEEE Standard Testability Method for Embedded Core-Based Integrated Circuits[C]//IEEE Std.1500-2005,2005:1-127.

[8]张颖,李华伟,李晓维.SoC总线串扰的精简MT测试集[J].计算机辅助设计与图形学报,2008.

[9]杨鹏.嵌入式芯核测试标准IEEE Std 1500综述[J].测控技术,2006.

[10]李广进,陈圣俭,牛金涛,等.数字IP核的IEEE Std 1500外壳构架设计研究[J].微电子学与计算机,2012.

[11]谈恩民,马江波,秦昌明.SoC的存储器Wrapper设计及故障测试[J].微电子学与计算机,2011.