多路突发信号数字分路及其FPGA实现技术

2013-12-23岳田

岳 田

中国电子科技集团公司第五十四研究所,河北石家庄 050081

0 引言

数字分路信道化技术是数字信号处理领域研究的热点,得益于数字分路技术目前国内外的卫星通信系统如MF-TDMA/TDM、星状网等迅速发展,一个中央站或星上载荷设备能够处理多站信号,使得站型和终端的处理能力大大增强。例如基于MF-TDMA/TDM 体系进行星上处理和星上交换的欧洲EuroSkyWay 系统已经得到了广泛的应用,其上行采用MFTDMA 方式,可同时支持102 个160Kbps、32 个512Kbps 和8个2048Kbps 速率的载波。本文针对TDMA 系统提出了一种易于FPGA 实现的多路突发信号的数字分路方法,该结构具有能够满足同时处理多路信号的能力,本文以16 路突发信号的数字分路为例描述了其FPGA 实现结构。

1 数字化分路技术的理论分析

实现多路信号数字分路有多种方法,其中最常用的有:带通滤波器组法、树形结构滤波器组法和多相阵列FFT 法。三种算法各有优缺点,带通滤波器组法和树形结构滤波法虽然相比多相阵列FFT 法简单,但实现困难,且随着分路路数的增加,计算复杂度及效率将成倍增长,以致于难于实现应用。因此对多相阵列FFT 算法的研究显得尤为突出重要,本文主要讨论基于多相阵列FFT 数字分路算法的多相滤波器组的实现。

多相阵列FFT 数字分路算法是基于多抽样率变频的数字信号处理技术,其实现结构是从均匀DFT 滤波器组数学模型引申出来的。DFT 滤波器组最基本的数学模型是在经过DFT滤波器组滤波计算后,每个通路用复调制器分别完成变频处理。

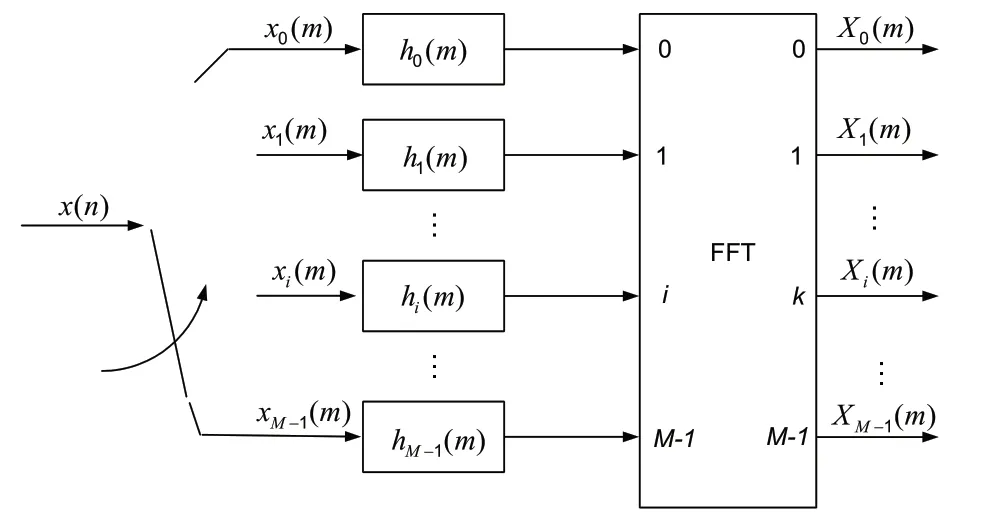

由(1)式可以看出,hi( m) *xi( m)是多相分支第i 路的卷积,对其进行离散傅立叶变换即可得到第k 个通路的信号 Xk(m )。如图1 所示可以看出多相阵列FFT 算法可由多相滤波器组和FFT 模块两部分组成。

图1 多相阵列FFT 算法原理框图

2 数字分路FPGA 实现设计

数字分路技术的FPGA 实现主要由三部分组成。首先进行多相滤波器组的FPGA 实现设计,多相滤波器组实现结构如图2 所示,其中多相滤波器组主要是由N 列存储器构成,每列存储器有16 个数据单元,且每列存储器的数据单元之间是可连续移动的,在采样时钟的作用下,每移入一个信号数据采样点,由于各列连续组成结构类似于移位寄存器,采样点就顺次在大存储器中串行依次移动,当移入12 个采样点后,每列存储单位中的数据分别与对应滤波器系数相乘相加后得到各路成型匹配后的滤波结果,各系数查找表可以复用从而节约资源。其次在完成匹配滤波后,分别对每列做16 点FFT 并行运算,从而将分路后的各路信号移入基带。16 点FFT 运算部分可以通过基2 的FFT 蝶形运算的并行实现结构。

图2 多相滤波器组的FPGA 的实现结构

按照上述相同的过程不断循环完成下一组12 个采样数据的匹配滤波、FFT 运算、消除频偏的计算过程,从而完成多路信号数据的数字分路过程。

利用Matlab 对5 路多路信号分路实现过程进行仿真,如图3 所示仿真为分路前合路信号频谱及分路后第一路信号的眼图,从眼图可以看出经过分路以后眼图张开得很好。通过FPGA 硬件实现整体解调,各路采用LDPC 码后在信噪比为4.5dB 时,误码率可以达到1 ×10-6。

图3 5 路合路信号频谱及第1 路信号的眼图

3 结论

本文针对TDMA 系统,从实现可行性的角度对多路突发信号的数字分路原理及其FPGA 实现进行深入的研究,提出了相应的实现方案。通过这种方案的实现可以得到每路信号每个符号抽取两个采样点,易于后续整体解调的实现,便于工程实现,适用于同时处理多路信号的场合,特别适合星状网通信系统中心站。

[1]Harris, F.J.; Dick, C.; Rice, M.Digital receivers and transmitters using polyphase filter banks for wireless communications [J].IEEE Trans,2003,4:1395-1412.

[2]文增译.多抽样数字信号处理.北京.人民有点出版社,1986,6.

[3]周德锁,田红心.基于星上处理的FDMA/QPSK整体解调及单片DSP实现技术[J].无线通信技术,1999,2.