基于FPGA的信号发生器设计

2013-12-07刘晓妤

徐 建,刘晓妤

(1.湖北民族学院 信息工程学院,湖北 恩施 445000;2.江汉油田采油工艺研究院,湖北 潜江 433123)

基于FPGA的信号发生器设计

徐 建1,刘晓妤2

(1.湖北民族学院 信息工程学院,湖北 恩施 445000;2.江汉油田采油工艺研究院,湖北 潜江 433123)

提出一种信号发生器的设计,采用ALTERA cycloneII EP2C35F676C为主控芯片,采用直接数字频率合成技术,通过数码管和键盘与人交互,能够产生可调频率的正弦波,方波,三角波和锯齿波.通过硬件系统测试,结果表明系统精度较高、带负载能力较强、运行稳定,且能对信号实现峰值检波功能.

直接数字频率合成;信号发生器;峰值检波

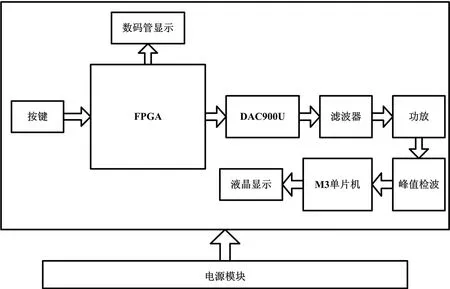

图1 系统设计框图Fig.1 System design diagram

随着数字系统的集成度的提高,使得人们对数字系统的设计有了新的思路.EDA技术的发展使得这一思路成为现实.信号发生器作为现代测试领域不可或缺的仪器之一,发挥着重要作用.

传统的信号发生器大多采用分立元件和中小规模集成电路设计或者是采用单片压控函数发生芯片MAX038进行设计.但频率准确度,稳定度较差,很难满足频率变化范围及步进要求.

现在的信号发生器基本上采用微处理器加DDS芯片进行设计,或者直接采用FPGA进行设计.采用微处理器和DDS芯片进行设计固然有控制简单,完全能满足频率变化范围和步进要求.但也有其缺点,即:外围器件较多,在对方波进行积分产生三角波时,积分电路中RC的值要随着频率范围而改变,比较复杂,且不能产生任意波形[1].因此,本文提出了采用FPGA为核心器件来设计信号发生器.其优点是采用VerilogHDL语言在FPGA中通过编程产生任意波形,集成度很高,并且能满足频率变化范围和步进要求.

1 信号发生器的系统设计

系统采用FPGA完成波形产生、频率和波形的改变.在FPGA中嵌入波形产生的数据ROM表,通过查表取值的方法得到波形数据,经过DAC900U后得到模拟波形,经滤波和功放后输出[2].系统设计框图如图1所示.

2 信号发生器的硬件设计

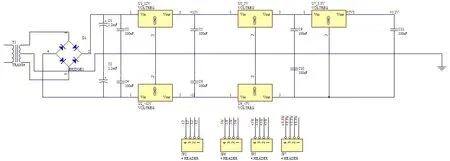

2.1电源模块设计

2.1.1 15 V电源(0.7A) 对于滤波电容的选择,要考虑三点:(1)整流管的压降;(2)7812/7912最小允许的压降Ud;(3)电网波动10%.由此而计算得到允许纹波的峰-峰值:

按近似电流放电计算,设θ=0°(通角),则:

故选取电容C=2 200 uF/30 V.

2.1.2 5V电源(1A) 计算得到允许纹波的峰-峰值:

故选取滤波电容C=4 700 uF/16 V.

系统的电源模块如图2所示[3].

图2 电源模块Fig.2 Power supply module

2.2 时钟分频模块设计

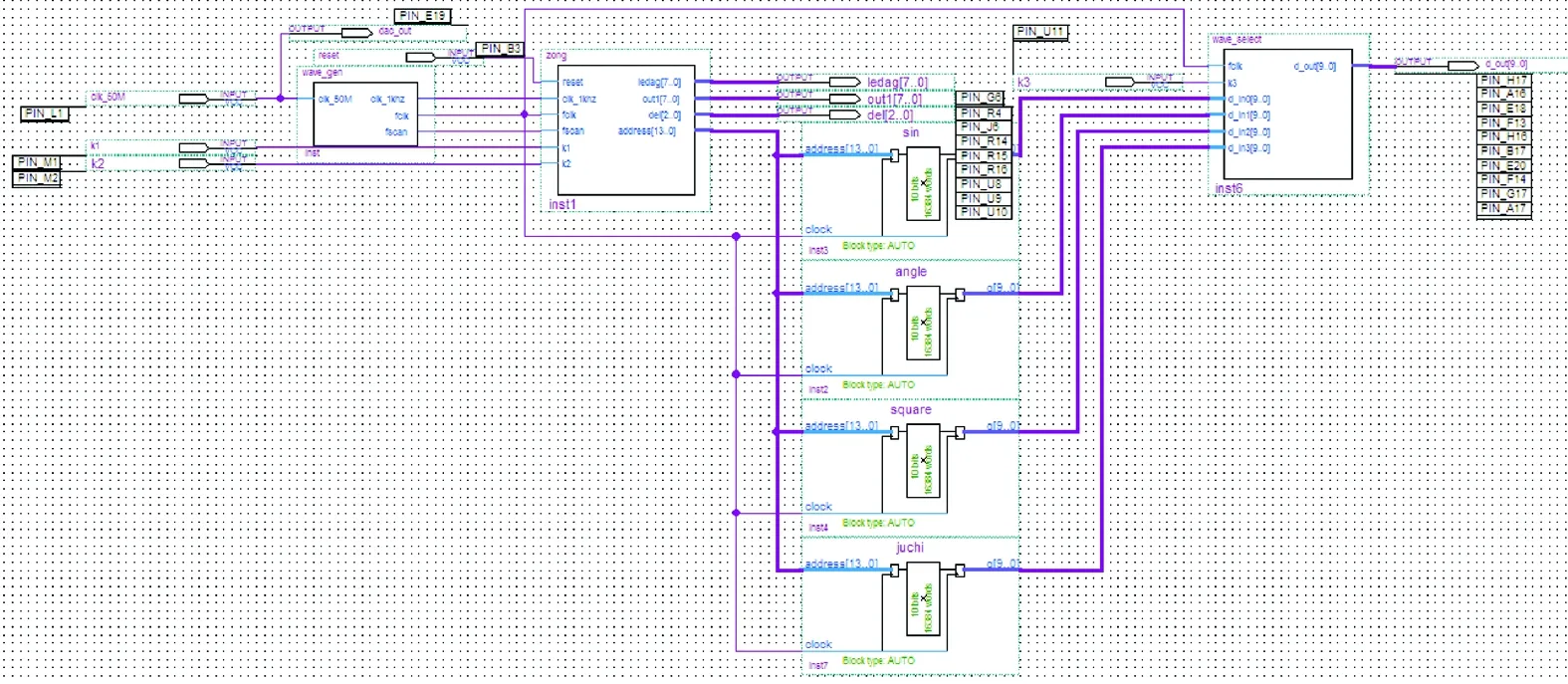

本设计中时钟模块的要求较高,要产生频率很稳定的时钟,通过设计一个计数器来对50 MHz主时钟进行分频产生1 KHz,1 MHz,400 KHz的时钟信号,设计模块如图3所示[4].

2.3 波形数据ROM设计

波形数据ROM就是存放波形数据的存储器,通过采样数据得到所要的波形.模块设计如图4所示.

2.4 波形选择模块

通过外部的控制按键key1,key2,选择不同的波形信号输出,波形选择模块如图5所示.

图3 时钟分频模块 图4 数据ROM表模块 图5 波形选择模块 Fig.3 Clock frequency modules Fig.4 The data ROM table module Fig.5 Waveform selection module

将各个模块连接如图6所示.

图6 各模块连接图Fig.6 Each module connection diagram

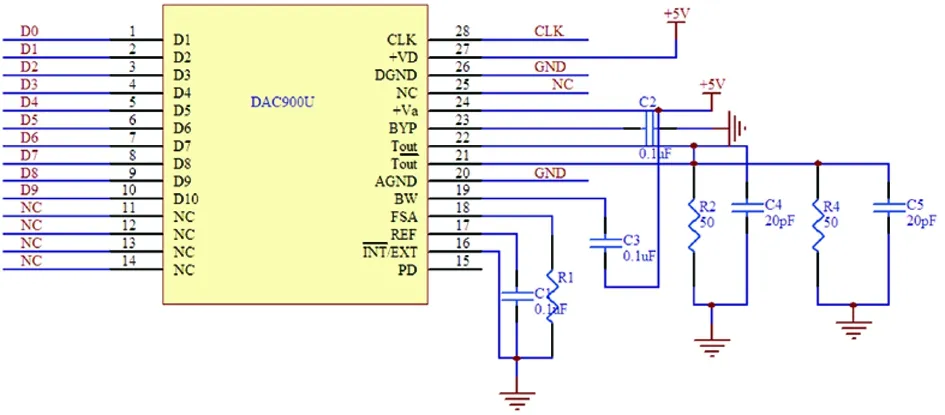

3 DAC模块设计

从FPGA中输出的数字信号通过DAC900U得到模拟信号:DAC900U属于10位高速DAC,数据吞吐率完全能满足设计要求.DAC模块设计电路如图7所示[5].

4 功率放大电路设计

图7 DAC电路模块Fig.7 DAC circuit module

5 峰值检波电路设计

峰值检波的原理是将交流信号变换成直流信号,然后通过M3单片机的AD采样电路和控制算法得到实际峰峰值.其电路原理如图9所示[6].

图8 功率放大电路模 图9 峰值检波电路Fig.8 Power amplification circuit module Fig.9 Peak detector circuit

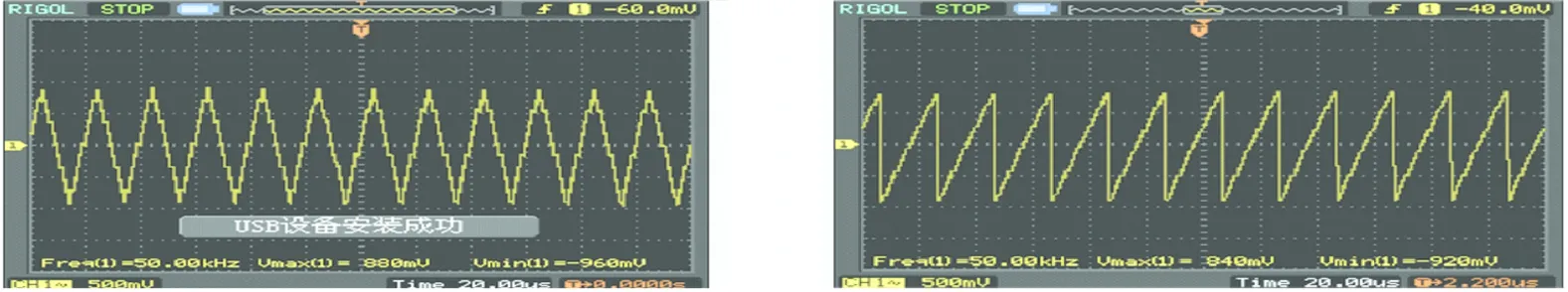

6 系统测试结果

根据本系统的设计方案,制作电路并对系统进行测试.通过示波器进行测试系统输出波形的结果如图10所示:

正弦波 频率50 KHz 方波 频率50 KHz

三角波 频率50 KHz 锯齿波 频率50 KHz图10 系统测试输出波形Fig.10 The outpar waveform of system testing

7 结语

本系统实现了基于FPGA的信号发生器的设计,通过实验样机的测试,其输出步进可以设置为10 Hz、100 Hz、1 000 Hz.而且可以产生频率范围为1 Hz-1 MHz的正弦波、方波、三角波以及锯齿波等波形,系统还可以经过扩展产生其它波形.除此之外,系统带负载的能力较强,通用性和实用性较好.

[1] 曹郑蛟,滕召胜,李华忠,等.基于FPGA的DDS信号发生器设计[J].计算机测量与控制,2011,19(12):3175-3177.

[2] 李雪梅,张宏财,王学伟.基于DDS技术的信号源设计[J].电测与仪表,2010,47(1):55-56.

[3] 徐建,刘晓妤.机器人灭火控制系统设计[J].湖北民族学院学报:自然科学版,2012,30(4):415-417.

[4] 吴丽华,刘洪涛,李胜明.基于FPGA的程控多波形发生器的研制[J].电测与仪表,2007,12(4):52-54.

[5] 吕矿生,周杏鹏.基于FPGA & Nios II 的任意信号发生器的设计[J].仪器仪表与分析监测,2008,21(2):21-23.

[6] 张金波,湛向,刘二伟,等.基于DDS/SOPC的多路可调谐波信号发生器[J].电力自动化设备,2008,27(11):74-78.

DesignofSignalGeneratorBasedonFPGA

XU Jian1,LIU Xiao-yu2

(1.School of Information and Engineering,Hubei University for Nationalities,Enshi 445000,China;2.Oil Production Technology Research Institute,Jianghan Oilfield,Qianjiang 433123,China)

This paper presents the design of a signal generator, using ALTERA cycloneII EP2C35F676C as the main control chip, with direct digital frequency synthesis technology, through the digital tube and keyboard to interact with people, can have adjustable frequency sine wave,square wave,triangle wave,sawtooth wave.Through the hardware test, the results show that the load capacity is strong,the precision of the system is high,the operation is stable,and can realize the signal peak detection function.

direct digital frequency synthesis;signal generator;peak detector

2013-07-30.

湖北省教育厅科学技术研究项目(B2013072;XD2012413).

徐建(1981- ),男,硕士,讲师,主要从事嵌入式与智能控制方面的研究.

TP346

A

1008-8423(2013)03-0330-04