LTE系统中小区搜索定时同步的FPGA设计*

2013-12-07张德民李小文

张德民,朱 翔,李小文

(重庆邮电大学 重庆市移动通信技术重点实验室,重庆 400065)

LTE作为3G技术的演进,在频带利用率、带宽的可配置性和数据传输速率上都有突出的优越性,受到了全球的关注[1]。而小区搜索是指移动台UE在初始接入小区时或移动台UE在进行小区切换的过程中,找到服务小区ID号以及与服务小区取得时间和频率同步的过程。在TD-LTE系统中,小区搜索是无线链路的关键步骤,是用户设备(UE)和EnodeB网络建立通信链路的前提。主同步信号(PSS)的接收和检测是小区搜索的第一步,其检测性能的好坏直接影响到下行链路同步的建立[2]。因此对PSS定时同步的研究具有重要的价值。

本文通过对常见的PSS定时同步算法的研究和分析,结合PSS本身的特性,给出了一种基于FPGA的并行流水线设计方案。与传统的DSP串行处理模式相比,FPGA的定时同步设计减少了数据处理的时延,提高了小区搜索的成功率,可保证用户终端更加迅速地接入LTE网络。

1 定时同步算法

TD-LTE系统中,主同步信号采用频域Zadoff-Chu序列的方式来生成,Zadoff-Chu具有良好的自相关特性。在TD-LTE系统中有3组可用的主同步信号,通过根序列指示u进行区分。主同步信号的生成如下:

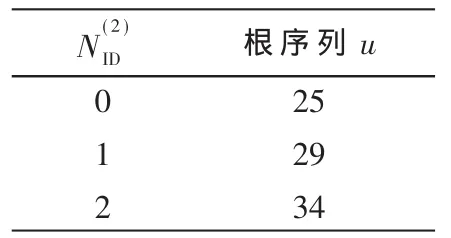

Zadoff-Chu序列的根序列指示u值如表1所示,它和N(ID2)一一对应。

主同步信号在频率上共占用72个子载波,并且其频率位置总是在所分配的带宽中央,中间的DC被打孔,为直流载波,两边各有5个资源元素的保护间隔,不携带任何信息。在时域上PSS信号被映射到子帧1和6的第3个OFDM符号上,具有5 ms的周期性[3]。

表1 根序列指示u

同一根序列的主同步信号具有良好的自相关特性,不同根序列对应的主同步信号之间的相关性较差。所以可以利用主同步信号的这一特性,在接收端用3个不同的N(ID2)产生的3个主同步信号分别与接收信号进行相关运算,确定主同步信号所在的位置并确定小区ID组内标识N(ID2)[4-5]。

为了降低计算的复杂度,将定时同步分为粗同步和精同步。粗定时同步用本地PSS和接收序列互相关的方法,对接收序列和3组本地PSS副本均进行1/16降采样,取滑动窗长度为2 048,3组PSS副本分别与接收序列做滑动相关,由最大值所在的相关集的PSS即可确定小区组内标识N(ID2),最大值所在的位置即为定时粗同步点的位置。图1所示为定时粗同步算法流程。

图1 定时粗同步算法流程

在PSS检测中,采用设定门限的方法可以提高PSS检测速度[6],即将查找最大值转换为当存在 θp、up使得滑动相关值Cup(θp)>TThreshold成立时,则停止剩余相关值的计算,物理组内ID为 up根序列所对应的 ID,PSS的起始位置为=θp。因此合适的门限值TThreshold是PSS正确检测的关键参数。设每个滑动窗内2 048个数据的总功率为Pω,理论上功率值即可作为该序列相关集门限值,但由于噪声及频偏可能会使粗同步时间点发生偏移,因此引入门限系数 η,使得其中η的经验值范围为 0.7~0.995,可根据仿真测试精度的要求及调试环境的改变而改变。

在粗同步点确定后,取容错范围(ncoarse-64,ncoarse+63),从第一个接收数据开始,取窗长度仍然为2 048,与N(ID2)对应的PSS信号r(n)不降采样进行逐个Ts滑动相关,从相关集中找出最大值对应的位置,即为定时精同步的位置。

2 FPGA设计模块

FPGA采用自顶而下的设计思想,将硬件任务分解后由各模块实现,上一级模块调用下一级模块[7]。下面分别介绍本设计的整体框架和两个公共复用子模块:乘累加模块和存储比较模块。

2.1 整体框架

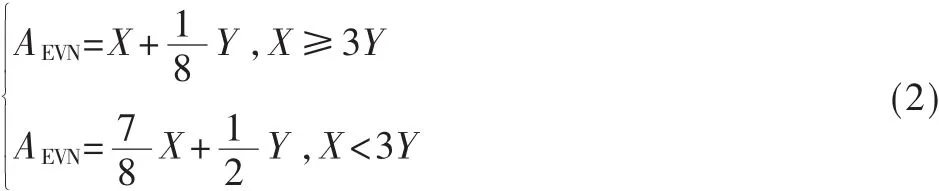

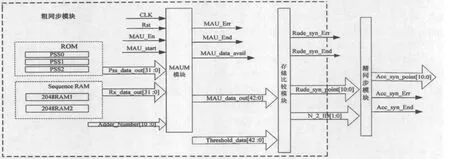

本地PSS副本补零后作IFFT运算存入3个ROM中,接收序列交替存到两个2 048 B的RAM中,以相同的处理时钟输出数据到MAUM模块,然后经过存储比较模块,就可以解出粗同步点和N(ID2),接着把数据传到精同步模块,确定精同步点,完成PSS定时同步。其中MAUM模块和存储比较模块完成本地PSS和接收序列互相关并从相关集中找最值的过程,也是粗、精同步公共复用的部分。MAUM模块加入了使能和启动信号,可以实时控制MAU单元,减少功耗。存储比较模块完成了复数的求模取最值,该模块使用了一种简化的复数求模近似算法,避免了平方运算,如下式:

粗、精定时同步模块整体实现框图如图2所示。采集到的数据传至后面的模块进行数据处理,经过短暂的几个时钟后,系统就以流水线模式开始运转。

2.2 MAUM模块

图2 PSS定时同步FPGA实现框图

MAUM模块,即乘累加模块。定时同步仍然按照上面的算法分为粗同步和精同步。而粗同步和精同步都采用了互相关的方法,因此相关的计算就成为本设计的关键。从射频接收的基带信号都是I、Q两路的复数信号,因此相关就是复数的乘累加计算。设计一个MAUM模块,它由6个MAU单元组成,每个MAU由 4个乘法器和2个加法器组成。每个MAU可在2个时钟内完成一次复数乘加,FPGA的并行设计使得乘法器能够以流水线方式输入/输出数据,整体只延迟1到几个时钟。RAM采样时钟为 30.72 MHz,FPGA主时钟为 200 MHz,在粗同步过程中采用了1/16降采样,因此要至少满足每接收16个数据的同时完成一次128点的相关,即在作本次相关的同时准备好下一次的相关数据,保证了数据采集和数据处理的无隙衔接,通过控制时序实现输入数据和相关后结果的流水线输出。如图3所示,时钟频率为250 MHz,相关点数为 64,仿真时间为 272 ns,时钟周期数为 68。

图3 MAU单元FPGA仿真图

2.3 存储比较模块

粗同步相关集大小为128,精同步为 2 048,输入数据来自MAUM模块。先将一个寄存器初值设为0,每次输入的数据与该寄存器的值作比较,若大于该值就更新寄存器的值,否则丢弃。在与最后一个输入数据比较完之后,寄存器的值就是该组相关集的最大值。这种边存储边比较的方式大大减少了数据处理的时间,也节约了内存空间。同时还引入了容错机制,若在一个相关集中发现了至少两个大于门限的值,则丢弃数据,系统跳回起始状态,重新进行定时同步。

粗同步数据在进行互相关的同时要完成动态门限的配置,从当前数据流截取窗长度为2 048的数据,作1/16降采样,计算当前窗的功率及门限值,与粗同步的当前相关集作比较,判断PSS点的位置,以确定粗同步状态的跳转。

3 仿真与实现

图 4、图 5分别是粗、精同步模块的 ModelSim仿真图和基于Xilinx Virtex-6板级验证的Chipscope截图。

仿真中采用系统带宽为5 MHz,子载波间隔为15 kHz,OFDM的子载波数为 2 048,普通 CP,AWGN信道,发送端发送的小区N(ID2)为0,时延偏移为 0。因为在 TDD模式下,PSS映射在子帧1和 6的第 3个 OFDM符号上,所以在前半帧中理论上PSS定时同步点的计算为35 264=30 720+160+2×2 048+2×144。

图4 粗同步模块FPGA仿真图

图5 粗同步模块FPGA实现图

实现条件:采样率为30.72 MHz,FPGA工作主时钟为 200 MHz,芯片型号 XC6VSX475T。

由图 4、图 5可以看出,从 MAUM模块开始到存储比较模块结束完成一次相关,MAU_data_r_flag是每次相关的启动标志位,rude_syn_opt为相关次数,rude_syn_point为粗同步点,rude_syn_finish是粗同步结束标志。图中N_2_ID初始值设为3,PSS定时同步后结果是0。rude_syn_opt计数到2 204,由于接收序列和本地PSS副本是1/16降采样,所以粗同步点rude_syn_point=2 204×16=35 264。前面已经提到,粗同步点比理论值有(-16,16)的偏差,为了尽可能减小误差,取容错范围(-64,63)来完成下面的精同步。仿真结果表明,精同步点与粗同步点没有出现偏差,PSS起始位置为35 264,与理论完全吻合。

从表2中可以看出,在采用相同算法的前提下,FPGA完成定时同步的时间比DSP缩短了85%。DSP完成小区搜索定时同步需要1帧半的时间,其串行处理模式要求必须将这些数据全部存储起来,这显然增加了系统的内存消耗和资源成本。而FPGA采用的多级流水线结构和并行运算则大大提高了数据处理的效率,使得用户终端可以更快地接入LTE网络。

表2 FPGA与DSP性能比较

本文提出了一种基于FPGA的PSS定时同步设计方案,并最终在硬件平台得以实现。结果表明,FPGA在算法结构固定、运算量大的前端数字信号处理中表现出先天优势,具有很好的应用前景。该设计方案能够满足LTE系统小区搜索算法的性能要求,可应用到LTE系统开发中。

[1]SESIA S,TOUFIK I,BAKER M.LTE,the UMTS long term evolution from theory to practice[M].John Wiley&Sons Ltd,2009.

[2]沈嘉,索士强,全海洋,等.3GPP长期演进(LTE)技术原理与系统设计[M].北京:人民邮电大学出版社,2008.

[3]3GPP TS 36.211 v9.0.0 evolved universal terrestrial radio access(E-UTRA)physical channels and modulation(Release 9)[S].2009.

[4]MANSOUR M M.Optimized architecture for computing Zadoff-Chu sequences with application to LTE[C].IEEE Global Telecommn.Conf.(GLOBECOM),Hawaii,HI,2009.

[5]BEEK J J V,SANDEL M,BRJESSON P O.ML estimation of timing and frequency offset in OFDM systems[J].IEEE Transactions on Signal Processing,1997,45(7):1800-1805.

[6]盛渊,罗新民.LTE系统中小区搜索算法研究[J].通信技术,2009,42(3):90-92.

[7]夏宇闻.Verilog数字系统设计教程(第 2版)[M].北京:北京航空航天大学出版社,2008.